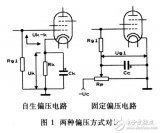

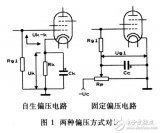

本文提供一個簡單實(shí)用的電子管測試裝置電路(Tube Tester),適用于DIY發(fā)燒友使用。工欲善其事,必先利其器,利用此裝置能比較精確地檢測電子管的靜態(tài)工作點(diǎn)、互導(dǎo)和配對特性等,在膽機(jī)制作或摩機(jī)時就胸有成竹,成功在望。

2015-01-07 10:22:48 22347

22347

,是不可能產(chǎn)生爆發(fā)性創(chuàng)新的。華為要開放地吸取“宇宙”能量,華為胸有成竹在2020年銷售收入超過1500億美元。

2016-06-02 16:24:06 2655

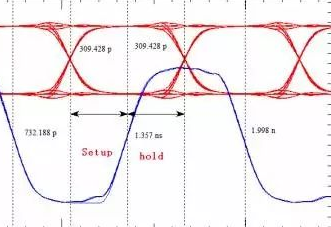

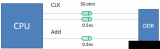

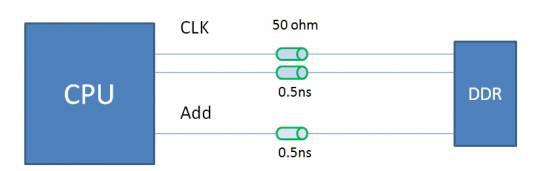

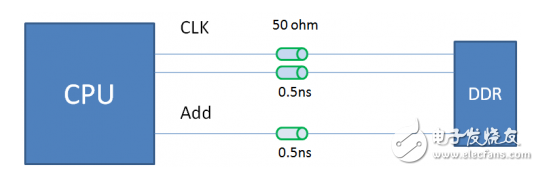

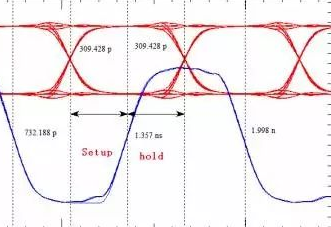

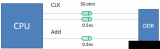

2655 DDR布線在PCB設(shè)計中占有舉足輕重的地位,設(shè)計成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,

2017-09-26 11:39:47 6363

6363

多年前,無線時代(Beamsky)發(fā)布了一篇文章關(guān)于DDR布線指導(dǎo)的一篇文章,當(dāng)時在網(wǎng)絡(luò)上很受歡迎,有很多同

2017-10-16 09:22:08 36277

36277

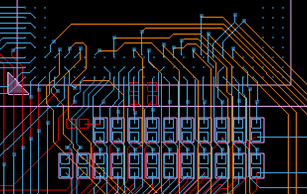

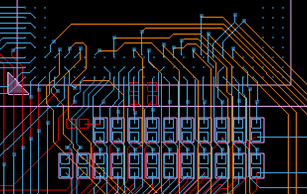

本文首先列出了DDR2布線中面臨的困難,接著系統(tǒng)的講述了DDR2電路板設(shè)計的具體方法,最后給出個人對本次電路設(shè)計的一些思考。

2020-11-20 10:28:35 6386

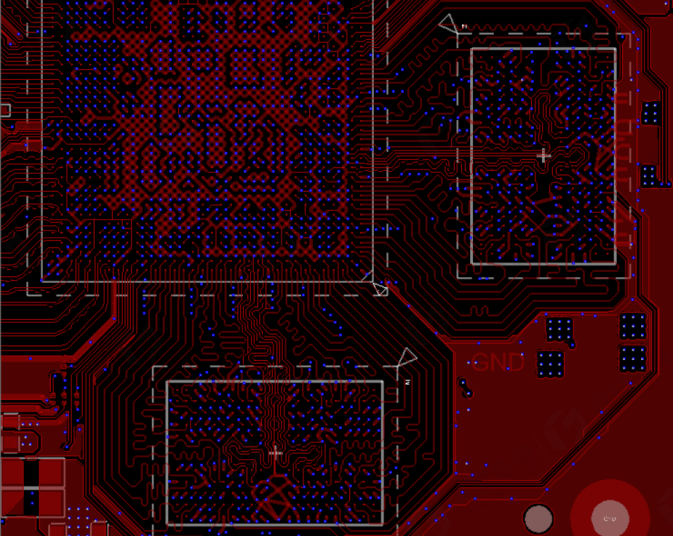

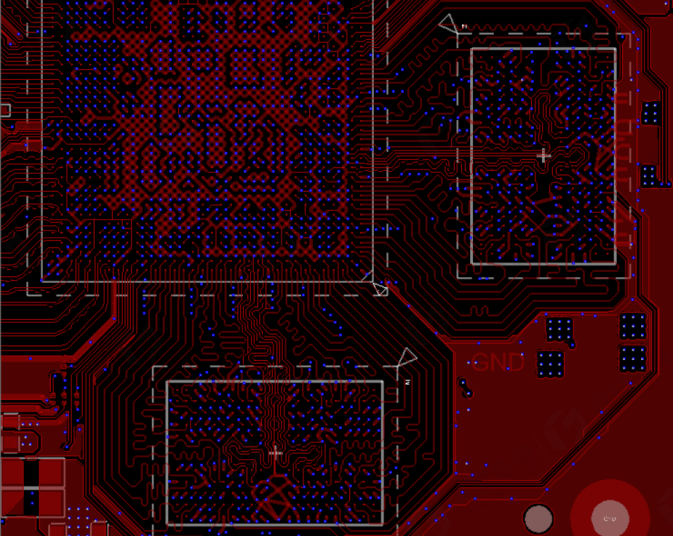

6386 上期和大家聊的電源PCB設(shè)計的重要性,那本篇內(nèi)容小編則給大家講講存儲器的PCB設(shè)計建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計要如何布局布線。

2023-08-16 15:20:58 1378

1378

上期和大家聊的電源PCB設(shè)計的重要性,那本篇內(nèi)容小編則給大家講講存儲器的PCB設(shè)計建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計要如何布局布線。 由于

2023-08-21 17:16:50 563

563

上期和大家聊的電源PCB設(shè)計的重要性,那本篇內(nèi)容小編則給大家講講存儲器的PCB設(shè)計建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計要如何布局布線。 由于

2023-08-24 08:40:05 899

899

[table=98%][tr][td]剛剛?cè)胧?b class="flag-6" style="color: red">一個51開發(fā)板,興致勃勃的編起了程序,很是胸有成竹。因?yàn)橹霸趐roteus上仿真了不少。可是在開發(fā)板上卻是處處碰壁啊。就說一個簡單的檢測按鍵是否按下

2012-07-15 10:48:43

看懂,如果你看不懂,那么請按這樣一個通用的基本法則做: (1)DDR和主控芯片盡量靠近(2)高速約束中設(shè)置所有信號、時鐘線等長(最多允許50mils的冗余),所有信號、時鐘線長度不超過1000mils(3

2015-01-15 10:39:37

主要是針對DDR2 667內(nèi)存的設(shè)計。信號分組:DDR2的布線中習(xí)慣把信號分成若干組來進(jìn)行設(shè)計,分成同組的信號具有相關(guān)或者相似的信號特性。時鐘組:差分時鐘信號,每一對信號都是同頻同相的。ckp0

2011-10-27 14:53:32

共享交流一下,DDR3布線技巧

2016-01-08 08:17:53

這篇帖子跟大家一起來討論下DDR3布線的那些事:DDR3的設(shè)計有著嚴(yán)格等長要求,歸結(jié)起來分為兩類(以64位的DDR3為例): 數(shù)據(jù) (DQ,DQS,DQM):組內(nèi)等長,誤差控制在20MIL以內(nèi),組間

2016-10-28 10:25:21

DDR2,DDR3等 因頻率不同,可以會有不同的要求,就一般而言,DDR布線時,要將DDR的網(wǎng)絡(luò)分成幾個組:地址線,控制線,數(shù)據(jù)線,時鐘等差分線。我的疑問是,在6層板中,需不需要將地址線與數(shù)據(jù)線分別

2015-11-04 13:40:02

DDR布線參考Hardware and Layout Design Considerations for DDR Memory InterfacesEmbedded systems

2009-11-19 10:08:48

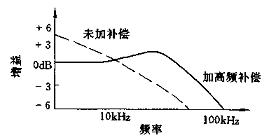

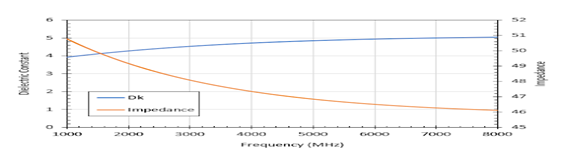

DDR-Topology DDR布線通常是一款硬件產(chǎn)品設(shè)計中的一個重要的環(huán)節(jié),也正是因?yàn)槠渲匾裕W(wǎng)絡(luò)上也有大把的人在探討DDR布線規(guī)則,有很多同行故弄玄虛,把DDR布線說得很難,我在這里要

2019-05-31 07:52:36

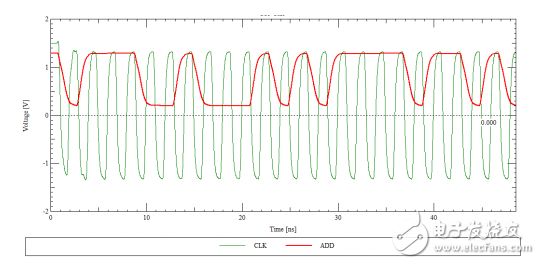

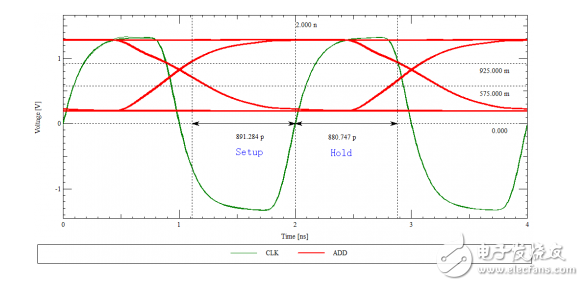

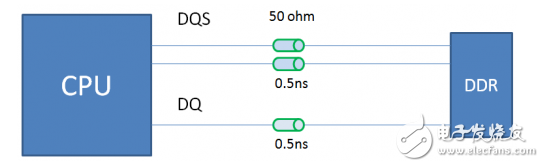

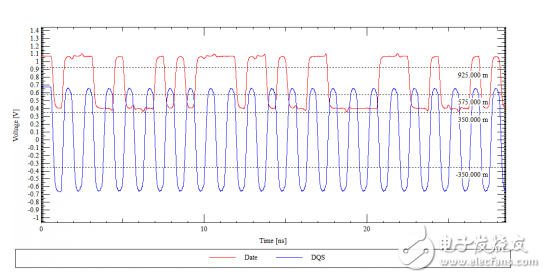

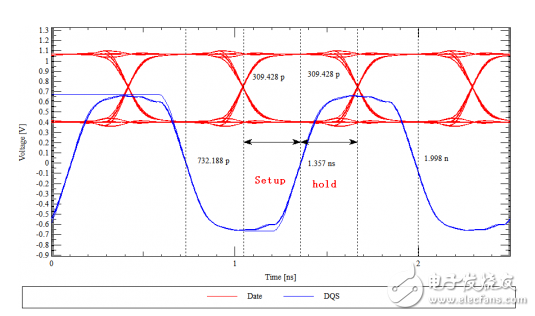

800Mbps。但是DDR的數(shù)據(jù)信號卻是雙倍速率的,如果DQS頻率為800MHz,那么數(shù)據(jù)信號的速率就應(yīng)該為1600Mbps。下面將通過具體的仿真實(shí)例來看一下。有興趣的朋友可戳附件下載。

2016-11-08 16:59:51

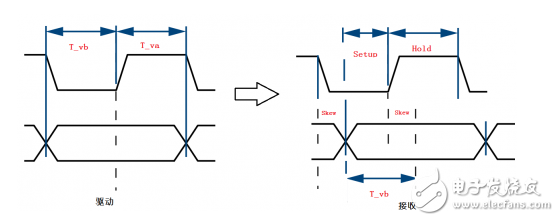

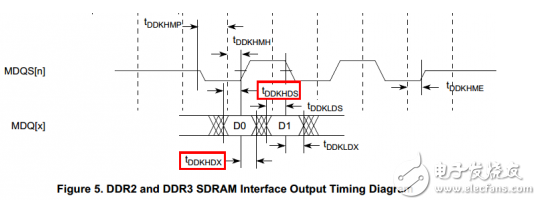

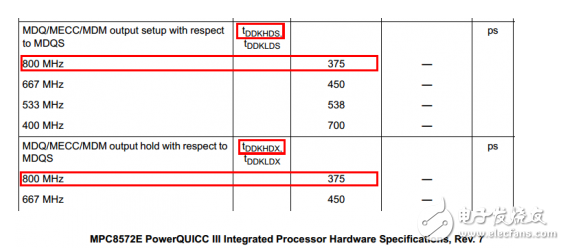

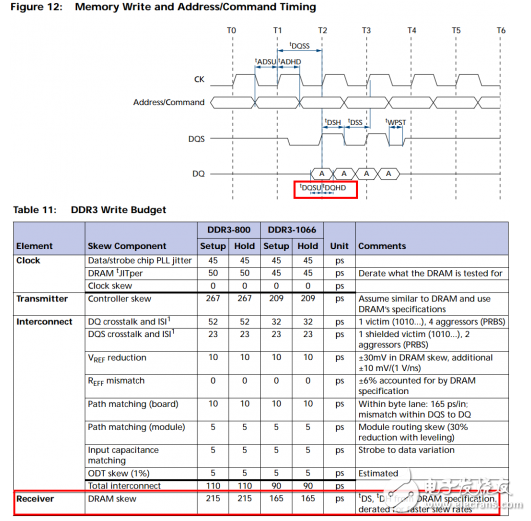

考慮時鐘抖動以及數(shù)據(jù)信號的抖動,以及串?dāng)_、碼間干擾帶來的影響,如果把這些因素都考慮進(jìn)來,留給我們布線偏差的裕量就比較小了。綜上所述,時序控制的目的就是要保證數(shù)據(jù)在接收端有充足的建立時間與保持時間,明白了這一點(diǎn),我們在線長匹配這個問題上就能做到胸有成竹,游刃有余了。

2018-09-20 10:29:55

層,用來抑制EMI; 導(dǎo)線走線長度:所有DDR的差分時鐘線CK與CK#必須在同一層布線,誤差+-20mil,最好在內(nèi)層布線以抑制EMI。如果系統(tǒng)有多個DDR器件的話,要用阻值100~200ohm的電阻進(jìn)行差

2012-12-29 19:20:36

上期和大家聊的電源PCB設(shè)計的重要性,那本篇內(nèi)容小編則給大家講講存儲器的PCB設(shè)計建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計要如何布局布線。

由于

2023-08-16 15:15:53

并不會注意一些數(shù)字上的差異,如DDR3和DDr2,或許大多數(shù)人都會追求時髦選擇DDR3,但是你真的了解DDR2與DDR3的區(qū)別嗎?作為消費(fèi)者,其實(shí)我們可主宰自己的命運(yùn),用知識的武器捍衛(wèi)自己的選擇。下面

2011-12-13 11:29:47

有了之前的硬件設(shè)計前期準(zhǔn)備,大家已經(jīng)能夠做到對整個方案的硬件設(shè)計(PCB板子)胸有成竹了,可謂是“萬事俱備,只欠東風(fēng)”。(注:關(guān)于AD10的使用不在本手記的內(nèi)容范圍,但這里假設(shè)大家都已

2012-03-30 10:18:07

有了之前的硬件設(shè)計前期準(zhǔn)備,大家已經(jīng)能夠做到對整個方案的硬件設(shè)計(PCB板子)胸有成竹了,可謂是“萬事俱備,只欠東風(fēng)”。(注:關(guān)于AD10的使用不在本手記的內(nèi)容范圍,但這里假設(shè)大家都已

2012-12-04 23:14:03

請問 在TI 給出的 ?EVM 參考設(shè)計中 DDR 的走線都串入一個22歐姆的電阻,按照SI 的理論這個電阻是保證匹配減少過沖的,在POWER PC 及MIPS 架構(gòu)的CPU ?DDR布線中不需要增加這個電阻 ,請問這個電阻在TI ?ARM 的CPU 中一定需要嗎?

2018-05-15 09:35:28

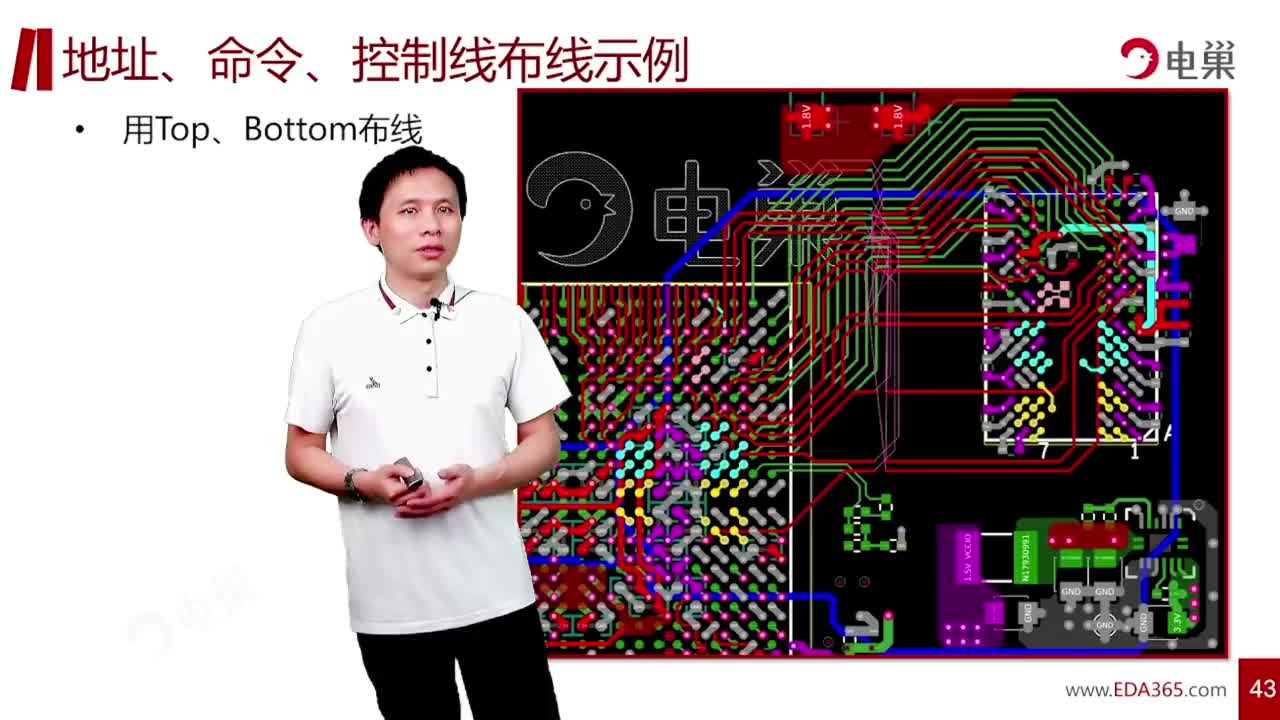

`直播鏈接:http://t.elecfans.com/live/574.html直播內(nèi)容及亮點(diǎn):詳解DDR高速存儲器模塊的布局布線的設(shè)計思路,從原理圖分析到PCB布局布線,從一片到兩片、四片DDR

2018-10-10 11:49:20

問題:在HW-USB-FLYLEADS-G電纜上使用的最大布線長度是多少?請看下面的圖片。背景:我使用HW-USB-FLYLEADS-G電纜和DLC10平臺電纜USB II連接到我板的JTAG端口

2020-05-20 07:45:06

,SI攻城獅很喜歡;作為一種片內(nèi)端接,由于去掉了PCB上的終端電阻,大大的簡化了設(shè)計,Layout攻城獅很鐘意;作為一種可以靈活配置的片內(nèi)端接,硬件攻城獅也愛不釋手。總而言之,喜大普奔。早在DDR2時代

2022-12-28 14:47:13

分信號布線問:在pcb上靠近平行走高速差分信號線對的時候,在阻抗匹配的情況下,由于兩線的相互耦合,會帶來很多好處。但是有觀點(diǎn)認(rèn)為這樣會增大信號的衰減,影響傳輸距離。是不是這樣,為什么?我在一些大公司

2014-12-31 14:32:05

在PCB設(shè)計中,通訊模塊天線的布線是十分重要的。大家來探討一下其注意事項(xiàng)有哪些?我列舉一下:1、天線的線寬最好多寬;2、天線的線長,天線都有一個匹配電阻,那么這個線長是不是根據(jù)公式R=p*(L/S

2013-08-26 11:41:17

多年前,無線時代(Beamsky)發(fā)布了一篇文章關(guān)于DDR布線指導(dǎo)的一篇文章,當(dāng)時在網(wǎng)絡(luò)上很受歡迎,有很多同行參與了轉(zhuǎn)載。如今看來,那篇文章寫得不夠好,邏輯性不強(qiáng),可操作性也不強(qiáng)。在近幾年的硬件產(chǎn)品

2022-08-11 09:07:02

平面。特征阻抗控制在50~60 Ω。信號線寬參考具體設(shè)計實(shí)施細(xì)則。信號組與其他非DDR信號間距至少保持在20 mil以上。組內(nèi)信號應(yīng)該與DDR時鐘線長度匹配,差距至少控制在25 mil內(nèi)。串聯(lián)匹配

2017-10-16 15:30:56

,以及串?dāng)_、碼間干擾帶來的影響,如果把這些因素都考慮進(jìn)來,留給我們布線偏差的裕量就比較小了。 綜上所述,時序控制的目的就是要保證數(shù)據(jù)在接收端有充足的建立時間與保持時間,明白了這一點(diǎn),我們在線長匹配這個問題上就能做到胸有成竹,游刃有余了。

2018-09-20 10:59:44

問題,保證內(nèi)存正確訪問,你的內(nèi)存電路就設(shè)計成功了。有了這個指導(dǎo)思想,內(nèi)存布線就可以按部就班地完成。不過,不同的RAM類型,雖然目標(biāo)都是避免判決和時序錯誤,但實(shí)現(xiàn)方法因工作模式不同而有較大差異。 高速系統(tǒng)一

2014-11-10 10:09:13

SDRAM和DDR布線技巧ecos應(yīng)用是與硬件平臺無關(guān)的,雖然開發(fā)板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內(nèi)存布線問題,為了完整敘述,這里一并給出說明。&

2010-03-18 15:33:07

存儲器控制器用戶指南列出了數(shù)據(jù),地址,控制和時鐘信號的長度匹配要求。給出的數(shù)字是否必須補(bǔ)償FPGA和DDR2封裝內(nèi)的鍵合線長度?如果是這樣,我在哪里可以找到這些長度?謝謝,TL以上來自于谷歌翻譯以下

2019-03-15 10:06:16

led顯示屏參數(shù)看這一篇就夠了

2021-06-01 07:17:31

、碼間干擾帶來的影響,如果把這些因素都考慮進(jìn)來,留給我們偏差的裕量就比較小了。 綜上所述,時序控制的目的就是要保證數(shù)據(jù)在接收端有充足的建立時間與保持時間,明白了這一點(diǎn),我們在線長匹配這個問題上就能做到胸有成竹,游刃有余了。

2018-09-19 16:21:47

的影響后,自動布線的質(zhì)量在一定程度上可以得到保證。7、布線的整理如果你所使用的EDA工具軟件能夠列出信號的布線長度,檢查這些數(shù)據(jù),你可能會發(fā)現(xiàn)一些約束條件很少的信號布線的長度很長。這個問題比較容易處理,通過

2018-10-04 16:50:52

Altium18.0.11無法正常顯示From-To兩點(diǎn)的布線長度,這是軟件的bug嗎

2019-09-27 05:35:33

的接口連接。DDR2芯片的連接電路如圖2.27所示。 圖2.27 DDR2芯片接口電路DDR2芯片接口以及PCB layout,通常需要遵循以下的原則。● 單端信號的電路板阻抗一般控制在50 ohm

2016-08-12 17:59:50

信號);2. 布局時應(yīng)注意以下幾點(diǎn):(1)對于DIMMs,匹配電阻應(yīng)靠近第一個DIMMs 放置對于SOP/BGA,匹配電阻應(yīng)根據(jù)不同的芯片確定放置端,若時鐘有加匹配電配,則電阻可靠控制芯片放置;(2

2012-09-17 21:15:33

DDR總線結(jié)構(gòu)是什么嵌入式DDR總線的布線分析

2021-04-25 07:36:29

體會到一種心里清澈明亮的感覺,因?yàn)樵谠O(shè)計的時候,你要對要實(shí)現(xiàn)的邏輯要非常的了解,要胸有成竹。看到小梅哥寫代碼,對著系統(tǒng)框圖一氣呵成,思路很清晰。這不僅僅是對設(shè)計系統(tǒng)整體的把握了然于胸,對底層細(xì)節(jié)也是

2015-11-03 21:31:23

設(shè)計問題案例集”兩大內(nèi)容體系系統(tǒng)化指導(dǎo)學(xué)習(xí),讓工程師對“設(shè)計規(guī)范”游刃有余、對“價格影響”胸有成竹。可一鍵計價、警示價格趨勢、建議調(diào)整方向,揭露板廠定價內(nèi)幕、消除行業(yè)潛規(guī)則。掃碼加入華秋DFM用戶交流群

2021-04-25 14:06:14

大家好,我正在研究我的第一個Kintex7 DDR3接口。為了實(shí)現(xiàn)RAM,我想在PCB上包含長度匹配的封裝走線長度。要獲取包延遲信息,我使用了命令(在Vivado中)link_design

2020-08-12 10:17:19

新東西且不斷地實(shí)踐之,在疑問中找到成長的路徑。為了利用有限的實(shí)驗(yàn)時間獲得最大的收益,我們希望每一個做實(shí)驗(yàn)的人都能做到以下四點(diǎn):1.做實(shí)驗(yàn)之前熟讀相關(guān)的資料,做到胸有成竹,最好能在課前準(zhǔn)備好程序2.不放過

2011-03-03 16:58:36

且不斷地實(shí)踐之,在疑問中找到成長的路徑。為了利用有限的實(shí)驗(yàn)時間獲得最大的收益,我們希望每一個做實(shí)驗(yàn)的人都能做到以下四點(diǎn):1.做實(shí)驗(yàn)之前熟讀相關(guān)的資料,做到胸有成竹,最好能在課前準(zhǔn)備好程序2.不放過實(shí)驗(yàn)

2011-03-09 13:52:59

根據(jù)需要進(jìn)行處理; 7.4信號越不重要,自動布線工具對其布線的自由度就越大。 8、布線的整理 如果你所使用的EDA工具軟件能夠列出信號的布線長度,檢查這些數(shù)據(jù),你可能會發(fā)現(xiàn)一些約束條件很少的信號布線

2018-08-23 17:02:59

的長度匹配關(guān)系。其他信號走線長度應(yīng)按照組為單位來進(jìn)行匹配,每組內(nèi)信號長度差應(yīng)該嚴(yán)格控制在一定范圍內(nèi)。不同組的信號間雖然不像組內(nèi)信號那樣要求嚴(yán)格,但不同組長度差同樣也有一定要求。信號組布線順序?yàn)榱舜_保

2015-10-21 10:37:10

對于平行線布線時是不是走線長度越短越好?

2014-02-14 09:56:19

PCB布線設(shè)計的好壞直接影響到硬件電路能否正常工作或運(yùn)行多快的速度。而在高速數(shù)字PCB設(shè)計中,DDR2是非常常見的高速緩存器件,且其工作頻率很高本文將針對DDR2的PCB布線進(jìn)行討論。DDR

2016-12-26 16:56:05

面對4片ddr3改怎么布局,我想雙面對稱布局改怎么走拓弧結(jié)構(gòu),第一次畫沒經(jīng)驗(yàn)忘指導(dǎo)。還有都有什么需要等長,都在什么上面有要求C:\Users\yg\Desktop

2019-06-03 03:00:21

DDR3布線時CPU到DDR3的地址線長2037mil ,數(shù)據(jù)線長1613mil,這樣會不會有問題

2019-06-05 03:34:28

本帖最后由 gk320830 于 2015-3-5 12:38 編輯

飛思卡爾的關(guān)于DDR內(nèi)存布線設(shè)計資料,主要涉及了內(nèi)存高頻控制線的等長,阻抗匹配的等設(shè)計

2013-08-26 13:31:20

本期講解的是高速PCB設(shè)計中,關(guān)于DDR布線知識。一.DDR信號功能與網(wǎng)絡(luò)名了解DDR的各個信號功能與網(wǎng)絡(luò)名。與DDR相比,DDR2/3最大差別多了功能OTD與OCD。重要信號線1.DQS信號

2017-10-27 10:48:26

SDRAM與DDR布線指南:ecos應(yīng)用是與硬件平臺無關(guān)的,雖然開發(fā)板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內(nèi)存布線問題,為了完整敘述,這里一并給出說明。 很

2010-03-18 15:29:08 0

0 本章先對自制電子管功放的元件選配、安裝程序、調(diào)試技巧及關(guān)鍵制作要領(lǐng)作一簡要介紹。當(dāng)你胸有成竹,躍躍欲試時,就可以動手操作了。

電子管音頻功率

2010-06-04 09:41:52 7959

7959

研究了MPC8379E處理器的相關(guān)資料和DDR2的特性,以及它們之間PCB布線的規(guī)則和仿真設(shè)計。由于MPC8379E和DDR2都具有相當(dāng)高的工作頻率,所以他們之間的走線必須滿足高速PCB布線規(guī)則,還要結(jié)

2013-03-12 15:22:26 80

80 PCB的DDR布局布線規(guī)則與實(shí)例教程說明

2015-11-13 16:13:47 0

0 DDR2_DDR3_SDRAM,PCB布線規(guī)則指導(dǎo)

2017-10-31 10:06:48 78

78 DDR布線在PCB設(shè)計中占有舉足輕重的地位,設(shè)計成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制

2017-11-28 11:34:58 0

0 DDR布線在PCB設(shè)計中占有舉足輕重的地位,設(shè)計成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制

2018-03-23 10:05:00 1334

1334

DDR布線在PCB設(shè)計中占有舉足輕重的地位,設(shè)計成功的關(guān)鍵就是要保證系統(tǒng)有充足的時序裕量。要保證系統(tǒng)的時序,線長匹配又是一個重要的環(huán)節(jié)。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號與時鐘做等長。

2018-09-27 09:56:00 6659

6659

在普通印制電路板的布線中由于信號是低速信號,所以在3W原則的基本布線規(guī)則下按照信號的流向?qū)⑵溥B接起來,一般都不會出現(xiàn)問題。但是如果信號是100M以上的速度時,布線就很有講究了。由于最近布過速度高達(dá)300M的DDR信號,所以仔細(xì)說明一下DDR信號的布線原則和技巧。

2019-03-24 10:00:06 6902

6902

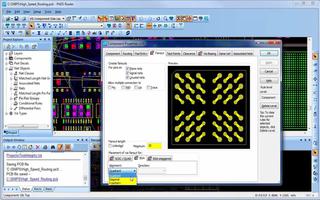

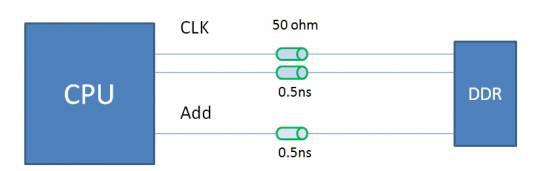

PADS 為高速網(wǎng)絡(luò)布線提供了一個可擴(kuò)展的環(huán)境,在該環(huán)境中可進(jìn)行交互和自動兩種模式。高速網(wǎng)絡(luò)的規(guī)則,例如匹配長度、差分對等,非常容易設(shè)置。在布線過程中,您將得到針對關(guān)鍵和敏感網(wǎng)絡(luò)的實(shí)時布線長度反饋。PADS 高速布線可成為提高您 PCB 設(shè)計生產(chǎn)率的“利器”。

2019-05-14 06:02:00 3230

3230

在現(xiàn)代高速數(shù)字電路的設(shè)計過程中,工程師總是不可避免的會與DDR或者DDR2,SDRAM打交道。DDR的工作頻率很高,因此,DDR的布線(或者Layout)也就成為了一個十分關(guān)鍵的問題,很多時候,DDR的布線直接影響著信號完整性。下面本文針對DDR的布線問題(Layout)進(jìn)行討論。

2019-06-08 14:35:00 4347

4347 他們很少用奇技淫巧。他們寫的代碼質(zhì)量高,并清楚知道代碼會如何演化,對整個代碼結(jié)構(gòu)胸有成竹。他們最多編寫一個設(shè)計文檔,他們的代碼就是文檔。

2019-07-18 10:09:06 1738

1738 、消費(fèi)多元化,電子商務(wù)完善、整裝渠道崛起、商業(yè)成本提升等方面的影響,現(xiàn)今家居建材行業(yè)的生意越來越難做。這兩年來,面對該如何轉(zhuǎn)型破局的問題,行業(yè)及大部分企業(yè)從開始的胸有成竹逐漸變得迷茫和懷疑。 厚積薄發(fā) 隱形巨頭的智慧商道 被譽(yù)為

2019-12-09 17:50:28 267

267 DDR布線在pcb設(shè)計中占有舉足輕重的地位,設(shè)計成功的關(guān)鍵就是要保證系統(tǒng)有充足的裕量。要保證系統(tǒng)的時序,線長又是一個重要的環(huán)節(jié)。

2020-01-14 14:46:10 1187

1187 本文檔的主要內(nèi)容詳細(xì)介紹的是DDR和DDR2與DDR3的設(shè)計資料總結(jié)包括了:一、DDR的布線分析與設(shè)計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設(shè)計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 如果您閱讀了許多PCB設(shè)計指南,尤其是有關(guān)并行協(xié)議和差分對布線的指南,則將看到很多關(guān)于走線長度匹配的內(nèi)容。當(dāng)您需要進(jìn)行跡線長度匹配時,您的目標(biāo)是最大程度地減少串行協(xié)議中的差分對,并行協(xié)議中的多個

2021-01-05 10:56:22 3656

3656

IT史上有一個經(jīng)典故事。那就是在1943年,IBM的董事長老托馬斯·沃森胸有成竹地告訴人們:未來5臺計算機(jī)就可以滿足全世界的市場。

2020-12-15 00:36:22 138

138 DDR4布線之a(chǎn)llegro約束規(guī)則設(shè)置綜述

2021-09-08 10:34:29 0

0 受委托讓我整理一個關(guān)于PCIe的主題分享文章,半月有余實(shí)在沒辦法交差,首先,我自己本身,對PCIe并沒有做到胸有成竹,我的PCIe知識也只是停留在理論階段,我并沒有實(shí)際做過任何有關(guān)PCIe的東西

2022-11-28 10:25:52 6522

6522 根據(jù) 50 歐姆阻抗線寬進(jìn)行布線,盡量從焊盤中心出線,線成直線,盡量走在表層。在需要拐彎的地方做成45 度角或圓弧走線,推薦在電容或電阻兩邊進(jìn)行拐彎。如果遇到器件走線匹配要求的,請嚴(yán) 格按照datasheet上面的參考值長度走線。比如,一個放大管與電容之間的走線長度(或電感之間的走線長度)要求等等。

2023-04-19 14:10:50 479

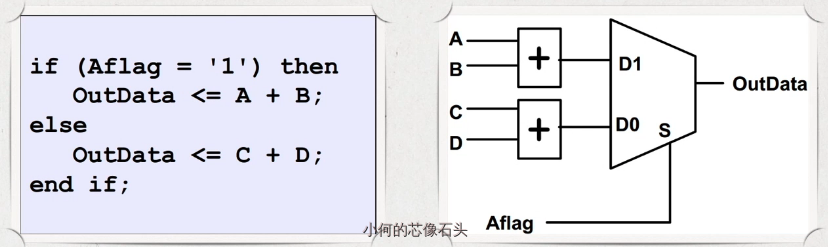

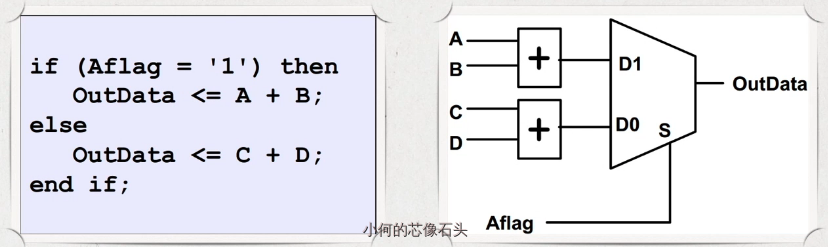

479 HDL 語言僅是對已知硬件電路的文本表現(xiàn)形式編寫前,對所需實(shí)現(xiàn)的硬件電路“胸有成竹”

2023-06-27 11:16:32 898

898

上期和大家聊的電源PCB設(shè)計的重要性,那本篇內(nèi)容小編則給大家講講存儲器的PCB設(shè)計建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計要如何布局布線。 由于

2023-08-17 18:15:02 325

325

上期和大家聊的電源PCB設(shè)計的重要性,那本篇內(nèi)容小編則給大家講講存儲器的PCB設(shè)計建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計要如何布局布線。由于

2023-08-18 08:09:43 384

384

SDRAM與DDR布線指南

2022-12-30 09:20:50 10

10 再談DDR內(nèi)存布線

2022-12-30 09:21:08 2

2 PCB的DDR4布線指南和PCB的架構(gòu)改進(jìn)

2023-12-07 15:15:58 759

759 DDR加終端匹配電阻和不加信號質(zhì)量的區(qū)別? DDR(雙倍數(shù)據(jù)傳輸速率)是一種常用于計算機(jī)內(nèi)存的高速數(shù)據(jù)傳輸技術(shù)。在DDR中,終端匹配電阻和信號質(zhì)量是對于數(shù)據(jù)傳輸穩(wěn)定性至關(guān)重要的兩個方面。下面將詳細(xì)

2023-12-29 13:54:22 316

316 話說,轉(zhuǎn)魔方真真是特別解壓的事情!雖然未必能如高手那樣胸有成竹“咔咔咔"幾下,行云流水間就還原。但,誰還不會“摳籽歸位”大法呢?不過,當(dāng)有人為你遞上一個不知經(jīng)歷了什么的神奇魔方,又滿懷期待

2024-01-13 08:04:39 488

488

電子發(fā)燒友App

電子發(fā)燒友App

評論