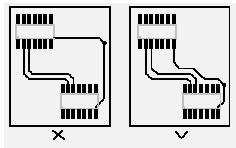

布線是PCB設(shè)計的重要組成部分,也是整個PCB設(shè)計中工作量最大和最耗時間的部分,工程師在進行PCB布線工作時,需要遵循一些基本的規(guī)則,如倒角規(guī)則、3W規(guī)則等。

2022-10-31 14:30:32 1100

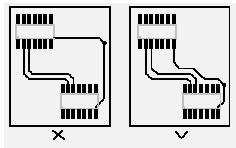

1100 。也就是說,同層的布線的寬度必須連續(xù),不同層的走線阻抗必須連續(xù)。圖4 特性阻抗連續(xù)規(guī)則規(guī)則五:高速PCB設(shè)計的布線方向規(guī)則相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串?dāng)_,增加EMI輻射

2018-11-28 11:14:18

能夠應(yīng)用和生產(chǎn),繼而成為一個正式的有效的產(chǎn)品才是PCB layout最終目的,layout的工作才算告一個段落。那么在layout的時候,應(yīng)該注意哪些常規(guī)的要點,才能使自己畫的文件有效符合一般PCB加工廠規(guī)則,不至于給企業(yè)造成不必要的額外支出?

2019-09-23 06:26:58

結(jié)構(gòu)的對稱性。常用的疊層結(jié)構(gòu):下面通過4層板的例子來說明如何優(yōu)選各種層疊結(jié)構(gòu)的排列組合方式。對于常用的4層板來說,有以下幾種層疊方式(從頂層到底層)。(1)Siganl_1(Top),GND

2015-03-06 11:02:46

4.3.3 實驗設(shè)計3:4層PCB 本章將考慮4層PCB疊層的幾種不同變體。這些變化中最簡單的是基于實驗設(shè)計2層疊層(第4.3.2節(jié)),外加兩個額外的內(nèi)部信號層。假設(shè)附加層主要由許多較薄的信號

2023-04-20 17:10:43

既然說到了參考平面的處理,其實應(yīng)該屬于疊層設(shè)計的范疇了。PCB的疊層設(shè)計不是層的簡單堆疊,其中地層的安排是關(guān)鍵,它與信號的安排和走向有密切的關(guān)系。多層板的設(shè)計和普通的PCB相比,除了添加了必要的信號

2016-05-17 22:04:05

在設(shè)計多層PCB電路板之前,設(shè)計者需要首先根據(jù)電路的規(guī)模、電路板的尺寸和電磁兼容(EMC)的要求來確定所采用的電路板結(jié)構(gòu),也就是決定采用4層,6層,還是更多層數(shù)的電路板。確定層數(shù)之后,再確定內(nèi)電層

2018-09-17 17:41:10

轉(zhuǎn)自賽盛技術(shù)分享在設(shè)計多層PCB電路板之前,設(shè)計者需要首先根據(jù)電路的規(guī)模、電路板的尺寸和電磁兼容(EMC)的要求來確定所采用的電路板結(jié)構(gòu),也就是決定采用4層,6層,還是更多層數(shù)的電路板。確定層數(shù)之后

2016-08-24 17:28:39

本帖最后由 lee_st 于 2017-10-31 08:48 編輯

PCB疊層設(shè)計及阻抗計算

2017-10-21 20:44:57

PCB疊層設(shè)計及阻抗計算

2017-09-28 15:13:07

PCB疊層設(shè)計及阻抗計算

2016-06-02 17:13:08

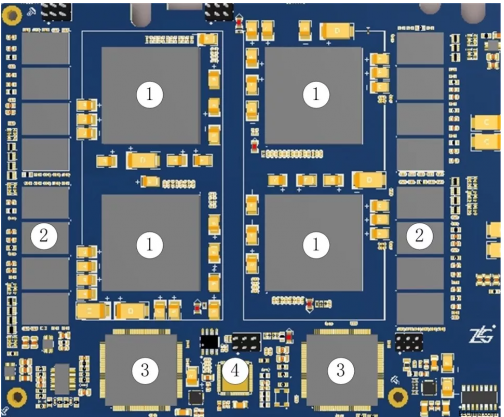

到的電源優(yōu)先鋪整塊銅皮;易受干擾的、高速的、沿跳變的優(yōu)選走內(nèi)層等等。 下表給出了多層板層疊結(jié)構(gòu)的參考方案,供參考。 PCB設(shè)計之疊層結(jié)構(gòu)改善案例(From金百澤科技) 問題點 產(chǎn)品有8組網(wǎng)口與光口,測試

2018-09-18 15:12:16

、EMC、制造成本等要求有關(guān)。對于大多數(shù)的設(shè)計,PCB的性能要求、目標(biāo)成本、制造技術(shù)和系統(tǒng)的復(fù)雜程度等因素存在許多相互沖突的要求,PCB的疊層設(shè)計通常是在考慮各方面的因素后折中決定的。高速數(shù)字電路和射須電路通常采用多層板設(shè)計。

2019-09-17 14:11:49

4.4.3 實驗設(shè)計9:通用的4層PCB 通過增加兩個內(nèi)部信號層,實驗設(shè)計6的2層疊加現(xiàn)在將增加到4層。與以前一樣,假設(shè)這些層主要由許多較薄的信號走線組成,而不是大面積連續(xù)鋪銅。 模擬的內(nèi)部

2023-04-21 15:04:26

PCB線路板疊層設(shè)計要注意哪些問題呢?

2021-03-29 08:12:19

PCB設(shè)計中疊層算阻抗時需注意哪些事項?

2019-05-16 11:06:01

在高速PCB設(shè)計流程里,疊層設(shè)計和阻抗計算是登頂?shù)牡谝惶荨W杩褂嬎惴椒ê艹墒欤煌浖挠嬎悴顒e不大,相對而言比較繁瑣,阻抗計算和工藝制程之間的一些"權(quán)衡的藝術(shù)",主要是為了達到

2018-01-22 14:41:32

`PCB設(shè)計線寬、線距規(guī)則設(shè)置多大比較好? 中國IC**1、需要要做阻抗的信號線,應(yīng)該嚴(yán)格按照疊層計算出來的線寬、線距來設(shè)置。比如射頻信號(常規(guī)50R控制)、重要單端50R、差分90R、差分100R

2019-02-19 13:36:26

是電路板設(shè)計的一個重要指標(biāo),特別是在高頻電 路的PCB設(shè)計中,必須考慮導(dǎo)線的特性阻抗和器件或信號所要求的特性阻抗是否一致,是否匹配。這就涉及到兩個概念:阻抗控制與阻抗匹配,本文重點討論阻抗控制和疊層設(shè)計的問題。

2019-05-30 07:18:53

pcb內(nèi)電層設(shè)計的規(guī)則中plane下面的三個規(guī)則應(yīng)該怎么設(shè)計?如圖所示?都選擇默認(rèn)?還是說根據(jù)自己設(shè)計規(guī)則里面電源線的寬度來設(shè)計?內(nèi)電層不走信號線

2017-07-24 09:12:34

進PowerPCB了。如果修改了設(shè)計規(guī)則,必須同步原理圖,保證原理圖和PCB的一致。除了設(shè)計規(guī)則和層定義外,還有一些規(guī)則需要設(shè)置,比如Pad Stacks,需要修改標(biāo)準(zhǔn)過孔的大小。如果設(shè)計者新建了一個

2015-07-24 12:29:05

完美的疊層圖,板框圖

2019-03-19 09:54:23

本帖最后由 yfsjdianzi 于 2014-5-11 14:23 編輯

疊層電感也就是非繞線式電感,是電感分類的其中一類。外形尺寸小,閉合電路,無交互干擾,適合于高密度安裝,無方

2014-05-10 20:04:18

疊層電感在現(xiàn)實中應(yīng)用也十分廣泛,目前疊層電感類產(chǎn)品被廣泛用于筆記本電腦數(shù)位電視,數(shù)位錄放影機,列表機,硬式磁碟機,個人電腦和其安一般消費性及電腦主品上輸入、輸出線路之雜訊消除。

2019-10-17 09:00:27

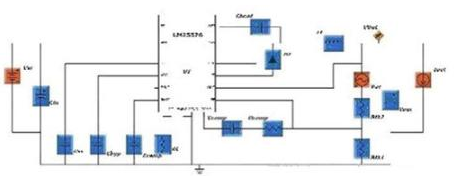

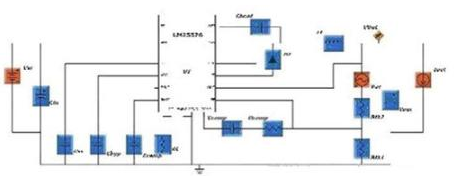

疊層電池的升壓電路

2019-11-07 03:31:57

在8層通孔板疊層設(shè)計中,頂層信號 L1 的參考平面為 L2,底層信號 L8 的參考平面為 L7。

建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅

2023-12-25 13:46:25

在8層通孔板疊層設(shè)計中,頂層信號 L1 的參考平面為 L2,底層信號 L8 的參考平面為 L7。

建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅

2023-12-25 13:48:49

不慌不忙的打開PCB文件,雷豹見Chris直接跳過了檢查PCB上的走線這一步,徑直的打開了疊層設(shè)置,然后給雷豹指一下這個地方,沒錯,指的就是下面這個紅框框的地方。

雷豹感覺好像懂了一點了,原來該客戶

2023-06-02 15:32:02

allegro16.5多層PCB板的疊層設(shè)計時,內(nèi)電層設(shè)計為正片或負(fù)片的選項不知道怎樣處理,我原來用的是allegro15.7,allegro15.7設(shè)置內(nèi)電層時,它有個選項,可選為正片或負(fù)片,但allegro16.5沒看到這個選項,求教知道的人指導(dǎo)一下

2015-09-20 18:45:24

在設(shè)計多層PCB時,疊層是必須得考慮的問題,層分布好壞直接影響產(chǎn)品的性能。下面推薦幾個使用最穩(wěn)定的疊層結(jié)構(gòu):

2020-06-10 20:15:31

多層板疊層設(shè)計規(guī)則,單層、雙層PCB板的疊層,推薦設(shè)計方式,設(shè)計方案講解。

2021-03-29 11:58:10

`完整的參考平面可以用來保證回路的連續(xù)性,寬的線寬可以降低信號的導(dǎo)體損耗,背鉆工藝可以減小過孔的Stub,提高信號的完整性,但是這樣往往會導(dǎo)致成本的增加。本文章將介紹兩種六層板疊層結(jié)構(gòu)。`

2021-03-30 10:42:55

常見的PCB疊層結(jié)構(gòu),四層板、六層板、八層板十層板疊層設(shè)計及注意事項。

2021-03-29 11:49:35

阻抗的電流返回路徑最重要的就是合理規(guī)劃這些參考平面的設(shè)計。圖1所示為一種典型多層PCB疊層配置。圖1 一種典型多層PCB疊層配置回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:18:25

在電路板設(shè)計上創(chuàng)建PCB疊層也會遇到類似情況:我們可能不了解最適宜的PCB材料,也不知道如何有效地構(gòu)建疊層。在作出決定之前,清楚了解我們的需求才能對設(shè)計最為有利。優(yōu)化設(shè)計意味著梳理可供考慮和選擇

2021-08-04 10:13:17

手機PCB Layout層數(shù)選擇與疊層設(shè)計方案剖析。回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:10:24

本文主要介紹多層PCB設(shè)計疊層的基礎(chǔ)知識,包括疊層結(jié)構(gòu)的排布一般原則,常用的疊層結(jié)構(gòu),疊層結(jié)構(gòu)的改善案例分析。回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:06:58

4.3.6 實驗設(shè)計6:一個4層的PCB板與熱散熱過孔 為了完整性,“4層+散熱過孔”結(jié)構(gòu)也被實驗設(shè)計為1層銅的幾個尺寸,并再次疊層,如圖8所示。結(jié)果如圖13所示。 (1)單層板。 (2

2023-04-21 14:51:37

本帖最后由 張飛電子學(xué)院呂布 于 2021-4-12 16:36 編輯

一到八層電路板的疊層設(shè)計方式 電路板的疊層安排是對 PCB 的整個系統(tǒng)設(shè)計的基礎(chǔ)。疊層設(shè)計如有缺陷,將最終影響到整機

2021-04-12 16:35:28

請問一下為什么我的疊層管理器打不開。。

2019-09-02 01:15:06

高速疊層設(shè)計原則:考慮因素:BGA 扇出、局部布線密度、阻抗控制、顧客要求、SI/PI考慮、成本、電設(shè)計源分割、板厚、板厚與孔徑比工藝要求:對稱性表層與內(nèi)層不要選擇4.0mil以下介質(zhì)不要選

2022-03-02 06:09:06

PCB設(shè)計中層疊結(jié)構(gòu)的設(shè)計建議:1、PCB疊層方式推薦為Foil疊法2、盡可能減少PP片和CORE型號及種類在同一層疊中的使用(每層介質(zhì)不超過3張PP疊層)3、兩層之間PP介質(zhì)厚度不要超過21MIL

2017-01-16 11:40:35

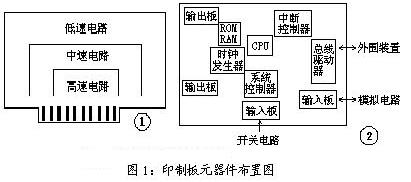

)后者則是較低頻的部分(<30MHz), 所以不能只注意高頻而忽略低頻的部分,一個好的EMI/EMC 設(shè)計必須一開始布局時就要考慮到器件的位置, PCB 疊層的安排,重要聯(lián)機的走法

2009-03-20 14:06:23

多層PCB如何定義疊層呢?

2023-04-11 14:53:59

搞定疊層,你的PCB設(shè)計也可以很高級

2020-12-28 06:44:43

射頻板設(shè)計PCB疊層時,推薦使用四層板結(jié)構(gòu),層設(shè)置架構(gòu)如下【Top layer】射頻IC和元件、射頻傳輸線、天線、去耦電容和其他信號線,【Layer 2】地平面【Layer 3】電源平面

2022-11-07 20:48:45

開關(guān)電源PCB排版技術(shù)需要遵循哪些規(guī)則?

2021-04-26 06:05:04

倒角規(guī)則 器件去耦規(guī)則 器件布局分區(qū)/分層規(guī)則 孤立銅區(qū)控制規(guī)則 電源與地線層的完整性規(guī)則 重疊電源與地線層規(guī)則 3W規(guī)則 20H 規(guī)則 五——五規(guī)則二、規(guī)則詳細(xì)解釋1.地線回路規(guī)則[/url

2015-02-03 14:44:13

普通鐵氧體電感、疊層扼流電感及疊層功率電感有何區(qū)別?

2011-10-16 20:20:01

貼片電感從制造工藝上可分為:繞線型、疊層型、編織型和薄膜片式電感器,常用的為繞線型電感和疊層型電感,繞線型電感是傳統(tǒng)繞線電感器小型化的產(chǎn)物,而疊層型電感采用多層印刷技術(shù)和疊層生產(chǎn)工藝制作,體積比繞線

2020-06-02 09:33:23

`疊層電感也就是非繞線式電感,疊層電感是電感按結(jié)構(gòu)不同對電感進行分類的其中一類。特 性: 1.外形尺寸小。 2.閉合電路,無交互干擾,適合于高密度安裝。 3.無方向性,規(guī)范化的自動貼片安裝外形

2013-08-29 17:41:52

電路板的疊層設(shè)計是對PCB的整個系統(tǒng)設(shè)計的基礎(chǔ),疊層設(shè)計若有缺陷,將最終影響到整機的EMC性能。疊層設(shè)計是一個復(fù)雜的,嚴(yán)謹(jǐn)過程,當(dāng)然,設(shè)計開發(fā),沒必要從零開始經(jīng)過一系列的復(fù)雜計算和仿真,來確定設(shè)計方案是否合適,僅需要總結(jié)前人的經(jīng)驗,選擇合適系統(tǒng)的疊層方案。

2021-11-12 07:59:58

畫ddr的八層板子這樣疊層可以嗎?這兩個哪個比較好?@chenzhouyu @鄭振宇_Kivy @cesc

2019-05-29 03:20:49

的連續(xù),否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續(xù),不同層的走線阻抗必須連續(xù)。 圖4 特性阻抗連續(xù)規(guī)則 規(guī)則五:高速PCB設(shè)計的布線方向規(guī)則 相鄰兩層間的走線必須遵循垂直走線的原則

2018-09-20 10:38:01

工作,其他7組光口通信正常。1、問題點確認(rèn)根據(jù)客戶端提供的信息,確認(rèn)為L6層光口8與芯片8之間的兩條差分阻抗線調(diào)試不通;2、客戶提供的疊構(gòu)與設(shè)計要求改善措施 影響阻抗信號因素分析: 線路圖分析:客戶

2019-05-29 08:11:41

設(shè)計的布線方向規(guī)則相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串?dāng)_,增加EMI輻射。簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串?dāng)_。規(guī)則六:高速PCB設(shè)計中的拓?fù)浣Y(jié)構(gòu)

2017-11-02 12:11:12

的經(jīng)驗 設(shè)計混合信號的電路板時,必須遵循的14個規(guī)則:考慮單獨的模擬和數(shù)字電源。了解所有返回路徑。雖然價格昂貴,但如果可能,請使用四層電路板。請勿將模擬信號與時鐘或快速數(shù)字信號并行布線。如果模擬和數(shù)

2018-07-30 08:25:01

RT,現(xiàn)有一個項目,需要布置八層板,兩層信號,因整塊板的平均功率達50W,需要布置兩層電源,其它層全鋪地,最佳的疊層順序是怎么樣較好。

2019-09-24 05:07:43

八層板常用的疊層方式有哪幾種?

2021-04-25 07:16:59

貼片疊層電感和貼片功率電感的作用和應(yīng)用有什么不同呢?

2015-09-15 16:27:53

在設(shè)計多層PCB電路板之前,設(shè)計者需要首先根據(jù)電路的規(guī)模、電路板的尺寸和電磁兼容(EMC)的要求來確定所采用的電路板結(jié)構(gòu),也就是決定采用4層,6層,還是更多層數(shù)的電路板。確定層數(shù)之后,再確定內(nèi)電層

2016-08-23 10:02:30

這個疊層圖是什么意思呢

2015-06-11 09:23:35

在《PCB的筋骨皮》一文中,我們提出了當(dāng)板厚在1.6mm及以上時,怎樣避免使用假八層的疊層,而導(dǎo)致PCB成本增加的問題。感覺大家的回答很踴躍哈,看來這個問題還是比較典型的。本來想截取一些回答放在

2019-05-30 07:20:55

在《PCB的筋骨皮》一文中,我們提出了當(dāng)板厚在1.6mm及以上時,怎樣避免使用假八層的疊層,而導(dǎo)致PCB成本增加的問題。感覺大家的回答很踴躍哈,看來這個問題還是比較典型的。本來想截取一些回答放在

2022-03-07 16:04:23

在《PCB的筋骨皮》一文中,我們提出了當(dāng)板厚在1.6mm及以上時,怎樣避免使用假八層的疊層,而導(dǎo)致PCB成本增加的問題。感覺大家的回答很踴躍哈,看來這個問題還是比較典型的。本來想截取一些回答放在

2019-05-29 07:26:53

的低阻抗的電流返回路徑最重要的就是合理規(guī)劃這些參考平面的設(shè)計。圖1所示為一種典型多層PCB疊層配置。 信號層大部分位于這些金屬實體參考平面層之間,構(gòu)成對稱帶狀線或是非對稱帶狀線。此外,板子的上、下兩個

2018-11-27 15:14:59

相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串?dāng)_,增加EMI輻射。簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串?dāng)_。規(guī)則六、高速PCB設(shè)計中的拓?fù)浣Y(jié)構(gòu)規(guī)則在高速

2021-03-31 06:00:00

,不同層的走線阻抗必須連續(xù)。規(guī)則五、高速PCB設(shè)計的布線方向規(guī)則 相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串?dāng)_,增加EMI輻射。 簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以

2022-04-18 15:22:08

高速PCB設(shè)計的疊層問題

2009-05-16 20:51:30

。也就是說,同層的布線的寬度必須連續(xù),不同層的走線阻抗必須連續(xù)。 規(guī)則五:高速PCB設(shè)計的布線方向規(guī)則 相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串?dāng)_,增加EMI輻射。 簡而言之

2016-01-19 22:50:31

PCB設(shè)計時應(yīng)該遵循的規(guī)則

1) 地線回路規(guī)則:

環(huán)路最小

2007-12-12 14:48:15 1096

1096

pcb布線設(shè)計規(guī)則.pdf,pcb布線設(shè)計規(guī)則.pdf

2015-12-28 11:31:11 0

0 PCB設(shè)計不是一件隨心所欲的事,它是有規(guī)則需要大家遵循的。

2020-02-28 17:24:29 1644

1644 【原創(chuàng)】PCB Layout必須遵循的“33條規(guī)矩”!

2019-08-20 17:34:53 4102

4102 1、遵照“先大后小,先難后易”的布置原則,即重要的單元電路、核心元器件應(yīng)當(dāng)優(yōu)先布局。這個和吃自助餐的道理是一樣的:自助餐胃口有限先挑喜歡的吃,PCB空間有限先挑重要的擺。

2、布局

2019-09-11 14:29:25 2436

2436

有一點需要注意,PCB布線沒有嚴(yán)格的規(guī)定,也沒有能覆蓋所有PCB布線的專門的規(guī)則。大多數(shù)PCB布線受限于線路板的大小和覆銅板的層數(shù)。一些布線技術(shù)可以應(yīng)用于一種電路,卻不能用于另外一種,這便主要依賴于布線工程師的經(jīng)驗。然而還是有一些普遍的規(guī)則存在,下面將對其進行探討。

2019-09-20 15:19:09 1752

1752

在墊,添加和分配相關(guān)網(wǎng)個人網(wǎng)或網(wǎng)與無源元件很容易。凈協(xié)會后,您可以設(shè)置規(guī)則長度的網(wǎng)或相關(guān)的網(wǎng)絡(luò)路由過程中遵循。

2019-11-04 07:09:00 1614

1614 Pcb板布線是能不能運行的重要之一。Pcb布線是按照電原理圖和導(dǎo)線表以及需要的導(dǎo)線寬度與間距布設(shè)印刷導(dǎo)線,布線一般應(yīng)遵循如下幾點規(guī)則:

2019-09-30 11:39:13 5312

5312 Webench選項包括對體積或效率的設(shè)計最佳化,這些均為單一選項。即高效率要求低開關(guān)頻率(降低FET內(nèi)的開關(guān)損耗)。因此需要大容量的電感和電容,因而需更大PCB空間。

2020-01-19 17:17:00 868

868

中,您將學(xué)習(xí) 12 條最基本但可行的 PCB 設(shè)計規(guī)則和技巧,以簡化 PCB 布局。基本的 PCB 布局規(guī)則將幫助初學(xué)者避免潛在的錯誤。對于高級工程師來說,這篇文章中的技巧也將有助于提高您的 PCB 布局技能。 1. 最重要的部分放在第一位 最重要的部分是什么?

2020-10-27 19:12:24 2563

2563 布線是 PCB 設(shè)計的重要組成部分,也是整個 PCB 設(shè)計中工作量最大和最耗時間的部分,工程師在進行 PCB 布線工作時,需要遵循一些基本的規(guī)則,如倒角規(guī)則、3W 規(guī)則等。 地線回路規(guī)則 環(huán)路最小

2023-02-02 14:46:36 830

830 布線是 PCB 設(shè)計的重要組成部分,也是整個 PCB 設(shè)計中工作量最大和最耗時間的部分,工程師在進行 PCB 布線工作時,需要遵循一些基本的規(guī)則,如倒角規(guī)則、3W 規(guī)則等。

2020-11-25 15:48:00 11

11 PCB設(shè)計規(guī)則你知幾何,20個PCB設(shè)計規(guī)則送給你。

2021-11-06 15:36:00 63

63 硬核分享,使用高速轉(zhuǎn)換器時應(yīng)遵循哪些重要的PCB布線規(guī)則?

2023-10-17 16:34:09 263

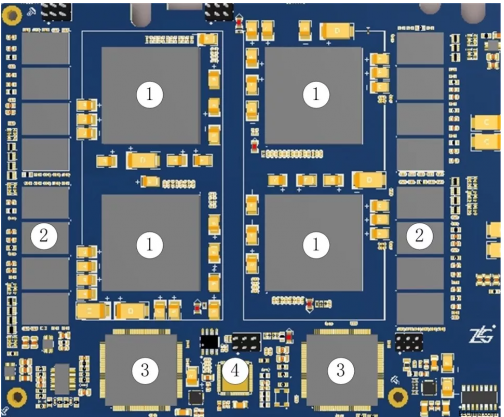

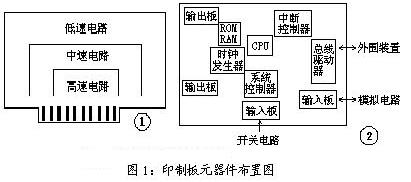

263 的不良影響。在進行PCB布線設(shè)計時,需要遵循一定的規(guī)則和原則,下面我們將會介紹PCB設(shè)計中的六大布線規(guī)則。 PCB設(shè)計六大布線規(guī)則 一:按照傳輸信號速度分類 在布線時需要按照信號傳輸速度的不同進行分類布線。一般來說,傳輸速度越快的信號需要

2024-01-22 09:23:53 495

495

電子發(fā)燒友App

電子發(fā)燒友App

評論