筆者根據自己日常使用PROTELFORWINDOWS的經驗教訓和讀者朋友問到的一些共性問題,歸納出10個問題,再以一問一答的形式,介紹有關PROTEL的使用技巧,希望對讀者有所裨益。

問 運行PROTEL時老是被提醒“系統錯誤WINDOWS無法從A:讀取數據,非法操作……”。如此反復,直至重新啟動系統甚至死機,這是為什么?

答 這說明您最近一次操作時曾打開過A:的文件且退出時未關閉。PROTEL有對打開文件的記憶功能,每次開機時它會自動找尋上次退出前所打開的那個文件,若A:有此文件,則自動予以調入,否則就出現上述現象。以原理圖編輯為例,這種記憶被保存在WINDOWS子目錄中一個名為SCH.INI的文件內,打開它即可得以驗證。為避免此麻煩,每次打開過軟驅中的文件后,記住關閉此文件(菜單是:File-Close)再退出PROTEL系統(File-Exit);也可以關閉Options-Preferences…中的“Save Defaults”。當然,后一種方法會對其它方面的使用帶來少許影響。

問 為什么有時會找不到繪圖和布線工具條?

答 這往往是由于調整顯示器分辨率造成的。假如您現在的顯示分辨率為1024×768,則兩個快捷工具條就已被您拖到了畫面的邊緣。若此時把分辨率調整為800×600,則由于這時實際所能顯示的畫面變小,原來已在邊緣的工具條勢必被“擠”到畫面以外,導致工具條“失蹤”。因此,在把分辨率由高調低之前把工具條拉到畫面中部即可解決這一問題。另外,顯示器分辨率的調整以及在WINDOWS系統中改變字體的大小均會造成這一現象,還會影響某些對話框內字符的完整性。

問 數字系統的原理圖上,經常要在集成塊引腳名或網絡標號的字母上方畫橫線,如WR、RESET等,PROTELFORWINDOWS能否做到?如何實現?

答 PROTELFORWINDOWS中有此功能。在原理圖或其元件庫的編輯中,遇到需要在網絡標號或引腳名等字符上方劃橫線時,只要在輸入這些名字的每個字母后面再補充輸入一個“”號,PROTEL軟件即可自動為您把“”號轉為前一字母的上劃線。這種方法絲毫不影響將來網絡表和印板設計系統對其原意的識別。

問 原理圖上各連線畫得清清楚楚,但在作“ERC”檢查時總被提示出錯,或建立網絡表后發現某些引腳沒連上,或是據此設計出的PCB上對應焊盤之間沒連上。總之,原理圖有連接,可印板圖自動布線時卻沒有對應走線。這是什么原因?

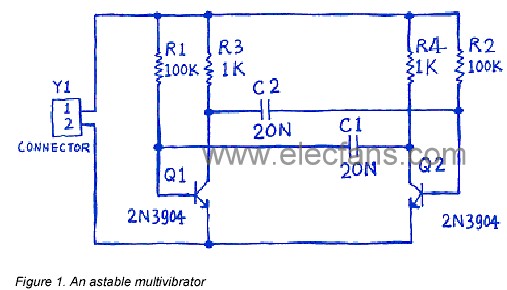

答 這是設計者最常遇見的也是最難自我察覺的問題,原因有以下幾種:(1)原理圖繪制時沒能嚴格區分繪圖工具條(Drawing Tools)和布線工具條(Wiring Tools)這兩者所畫出的直線的區別。前者所繪的直線是“圖畫”意義上的直線(Line);后者所繪制的直線才是具有“電特性”意義上的連接導線(Wire)。遺憾的是,軟件所給的兩者的缺省顏色太接近,以至于設計時很容易混淆。如果僅僅是繪制原理圖,即使混淆兩者也無妨,但要用這種原理圖來提取網絡表,則混入“Line”的對應兩點間必定連接不上。PROTEL給出前者的目的是供用戶在圖面上繪制一些與布線無關的圖案等,換言之,如果與布線無關的線條用了“Wire”繪制,同樣也會在布線時被提示出錯。解決的方法很簡單,就是在放置這兩種線中的任一種時把缺省色改為其它色。

(2)繪制“Wire”時,線畫長了,以至于越過元件引腳端點與引腳線重疊。避免這種現象可在為每個元件連線時點選該元件,使之顯示出外廓虛線。PROTEL的“ERC”功能可以查出此類毛病(菜單是:File-Reports-Electrical Rules Check……)。

(3)柵格(Grids)選項設置不當,其中柵格捕捉精度(Snap)取得太高,可視柵格(Visible)取得較大,導致繪制“Wire”時稍不留神就在導線端點與引腳端點之間留下難以察覺的間隙,PCB設計時必然缺線。例如,當Snap取為1,Visible取為10時,就很容易產生這種問題。這種設置可在菜單Options-Sheet…所打開的Grids對話框中查找。另外,自己編輯庫元件的過程中,在放置元件引腳時如果把柵格捕捉精度取得太高(具體在菜單“Options-Workspace…”調出的對話框中)同樣也會使得該元件在使用中出現此類問題,所以,進行庫編輯時最好取與原理圖編輯相同的柵格精度。

(4)在編輯原理圖庫中的元件時沒有注意引腳的首尾之分(首端是指應當靠近元件圖案的一端;尾端指遠離元件供導線連接的那一端),導致凡使用了這種元件的地方在原理圖上看似被導線連上了,實質上卻是連在了引腳的首端,實際布線時當然無法連接上。這種問題可這樣考慮:由于每個引腳的引腳名(例如VCC)必定是引腳的首端,故把帶引腳名的端子落在元件圖案內即可。為此,在編輯元件庫時應把各引腳(Pin)的“Show Name”項打開,顯示出各管腳名,以此作為標識。

問 電源或接地在PCB布線時經常發生混亂,如某些該接電源或地的地方沒接上,甚至出現電源正端與地短接的嚴重問題。舉例說來,原理圖中各處的電源地(Powerground)符號“”畫得很明白,可實際布線時PROTEL卻并沒把標了這種符號的各點連到電源地端,反倒是有些點竟被連在了電源正端。另外,原理圖上標了“”的端點往往也沒能接于電源輸出的對應端。這是為什么?

答 出現這類問題的關鍵在于原理圖繪制時只注意到正確“圖形”的獲得,而忽視了對這些圖形符號電特性(主要是網絡名)的準確定義。要知道,PCB自動布線軟件并非依據原理圖中各個圖形的識別來布線的,而是依據在原理圖中放置這些圖形的時候給這些圖形所起的名字來布線的。換言之,若在放置電源地(Power Ground)符號“”時您沒給它賦予“GND”的名字,而是沿用了放置其它部件時所用的名字,那么,實際布線時該點必定不會被連到“GND”,而被連接到它實際所用名字所指定的網絡。如果在放置電源地(Power Ground)符號時給了它一個“VCC”的名字,則勢必出現電源被短接的問題。這個問題可在使用菜單“Place-PowerPort”或快捷工具條放置電源端子時,觸發一下“Tab”鍵,調出每一次被放置的電源端子的屬性(Attributes)對話框,在選擇好圖符形式(Style)的同時,千萬別忘了在“Net”欄目中賦予它一個正確的名字。

原理圖上標了+5V、+VCC()的端點往往也沒能接于電源這一問題看似與上述分析相同,其實這兩類問題還是有區別的。該問題產生的根源在于沒能搞清PROTEL元件庫所給出元件的電源端子的缺省表達形式,這些缺省形式有:VCC、VSS、GND、VPP、VEE、VCC1、VCC2、VCCA等等,可見,+5V、+VCC根本不在此之列,故您的電源輸出端子若用“+5V、+VCC”命名,那么,所有元件的電源端都將無法連接到它們上面。值得注意的是,PROTEL軟件為了原理圖圖面的簡潔美觀,多數庫元件的這些端子在原理圖上是不顯示(Hidden Pins)出來的,這就更增加了這一問題的隱蔽性。除此而外,元件上還有不少非電源端子需要接高電平(例如多輸入“與”門、觸發器的置1端等),在給這些端子接電源獲得高電平時也務必要注意與元件電源端子和供電電源端子所用名稱的一致性。

問 從PROTEL自己的原理圖庫(Device.LIB)提取的諸如三極管(NPN、PNP)、電位器(POT2)等元件用在原理圖上,同時也給它指明了PROTEL自己的封裝圖庫(Pfw.LIB)中對應的封裝(Footprint)形式(例如給三極管指定了TO-126、TO-220等形式的封裝;電位器被指定了VR1、VR2…等封裝),但是,在PCB設計中用網絡表來放置元件(菜單是:Netlist-Load…)時,總會出現“丟失引腳(Missing Pin)”的提示。仔細審核PCB圖上的連線,會發現三極管的三個引腳均未被連接;電位器總有一個引腳懸空。這是什么原因?

答 實質上這是PROTEL封裝庫一個圖形樣式多種用途帶來的麻煩。以TO-220封裝為例,它三個引腳的排列可以是E、B、C,E、C、B,C、B、E,等等。另外,某些場效應管的引腳名稱是GATE、DRAIN、SOURCE,但它也可能采用TO-220封裝。PROTEL封裝圖庫中像TO-220一類“三極管”封裝形式各焊盤的原始名稱(Designator)都被命名為1、2、3。封裝焊盤的這種命名方式帶來了靈活性,但用戶使用前必須要按實際所用元件和它的引腳排列的具體順序,再結合原理圖庫中對應元件的引腳命名,對這類封裝的焊盤重新命名。筆者就另開辟了一個封裝庫,把原始的TO-220封裝多次反復以不同的名字拷入其中,如:TO220EBC、TO220ECB、TO220GDS、TO220GSD……,然后,再把這些封裝的3個焊盤名稱依次由1、2、3分別改成為E、B、C;E、C、B;GATE、DRAIN、SOURCE;GATE、SOURCE、DRAIN……,這就大大方便了以后工作中的反復調用。當然,這也要求您在原理圖設計階段就要籌劃好所用元件的封裝類型,并按以上所述的元件封裝名稱來填寫原理圖編輯中各元件的封裝名稱(Footprint)項。

同理,電位器的三個引腳中中間抽頭也未必就是物理位置上的中間焊盤,PROTEL封裝庫對它三個焊盤的原始命名也是1、2、3,為區別起見,使用前也要編輯出中間抽頭(W)位于不同位置時的具體封裝供調用,否則,出現丟失其中間抽頭的現象也就不足為奇了。

問 “塊移動”使用很方便,但為什么有時用它卻會導致圖面其它部分已繪好的地方變得重重迭迭或支離破碎?另外,編輯封裝圖庫時,明明繪制的是某一個元件的封裝,為什么往PCB上放置該元件時卻同時出現幾個不相干的封裝?

答 這兩個問題同出一轍,都是忘記及時清除前一次的選擇操作所致。PROTEL FOR WINDOWS不同于以前的版本,它所提供的框選(即DOS版中的塊選擇)具有“累積效應”,即作新的選擇時并不取消原有的選擇,這樣設計的目的是能夠通過多次選擇來獲得任意形狀內圖素,但是,如果一次選擇的矩形已能滿足要求,那么,每次選擇過后務必要取消本次選擇以便為下一次選擇提供條件,取消的菜單是“Edit-DeSelect-All”。由于此功能使用率相當高又容易被忘記,故較高版本中已專門為它在主工具條中設置了快捷按鈕。至此不難理解,以上導致繪好的畫面破碎或重疊正是由于多次框選的塊被同時移動所導致,PCB上放置封裝時出現多個元件也是入庫前的塊定義前沒有取消先前的框選結果所引起的。這些問題只有使用時多加注意才能避免。

問 為什么使用自己編輯的原理圖庫元件或PCB元件封裝圖形時總是發生光標與被選圖形相距很遠的現象,甚至在放置元件時光標指定在圖面上,元件卻落在工作簿以外?這類元件在被鼠標點選后為什么還都會出現一個遠超出元件外圍尺寸的虛線框?

答 這是所編輯的元件或封裝沒被指定基準點或定位原點的緣故。首先,對于原理圖庫的元件編輯,當圖形和引腳等全都完成后,要把整個圖形框選后剪切下來,剪切時會在屏幕下部的命令行中提示您指定參考點(Choose Clipboard Reference,一般多選在元件第1腳的端部),然后,調用菜單“Edit-JumpToOrigin”,將鼠標光標落在基準點上,為保證找到的這個基準點不再改變,往下的操作不應再挪動鼠標而改由鍵盤完成,調用“Edit-Paste”菜單,將圖形粘貼在此基準點上即可。由于軟件設計問題,上述過程軟件并沒給出提示要您必須指定基準點,故該步驟經常被人忽視,導致自己編輯的元件幾乎無法使用。其次,對于封裝圖庫元件的編輯,Windows的老版本(如V1.5)反倒有讓用戶給出原點的提示,較少出錯,而較新的版本例如PROTEL98中卻需要在編輯好圖形后回到“Edit-Set Reference-Location”菜單中指定定位原點。

分析至此,也就能明白為什么出現超大的外圍輪廓線了,因為輪廓線是包含被選中元件定位基點的,所以,一旦基點未定義且落在元件以外,輪廓線自然會大于元件實際尺寸。另外,庫編輯時如果元件以外散落一些字符等圖素,也會導致該現象,所以庫元件編輯完后應用Zoom-All查看整個圖面。

根據以上分析,讀者可反復試驗以加深理解。要提醒的是,每次對庫中某元件作修正后,最好作一下庫的重新加載(Library-Add/Remove…)或運行一下“Library-Update Parts in Cache”,方能在往后的操作中見效。

問 為什么很多時候設計出的PCB元件排列順序總是事與愿違,有些元件還不得不從反面插入?

答 這是設計過程與制作過程相脫節時較容易發生的問題。PCB設計時,計算機屏幕上所顯示的元件和印板走線等圖案是假想一個裝配完成的電路板從離元件最近的位置上(即元件引腳尖端背離自己時)觀察所得到的結果,也就是說,是從印板的頂面(Top Layer)觀察所得到的結果。對于雙面印板的底面(Bottom Layer),是假想印板透明,通過透明體仍按以上方位進行觀察所得的結果被顯示于屏幕上的。也正是基于此理,PROTEL專門提供了一個“鏡像”打印方式(Print-FinalArt work…-Output-Mirroning),該方式的打印結果相當于從底面(即元件引腳尖端指向自己時)觀察印板所得到的圖案。舉例說來,若想通過復寫紙把底面(Bottom Layer)的圖案轉印到敷銅板上就需要這種打印結果。

明白以上所述即可理解以下幾條:(1)PCB設計中往印板上放置元件時務必注意是放在哪一面的[如無特殊要求,應放在頂面(Top Layer)];(2)為了便于裝配,數碼管經常被裝在底面(Bottom Layer),如果是整體式的多位數碼管倒也無妨,直接把它放在底面即可;但對于散裝的多位數碼管必須同時考慮放在底面和“個十百位”從右往左排的習慣這雙重因素;(3)放置雙列直插式的元件(例如DIP8)時只允許按空格鍵獲得元件繞定位點的旋轉,而不能按X鍵或Y鍵進行關于過此點的軸線的翻轉。否則您只能從背面裝元件;(4)對于三極管一類的三腳元件,如果三腳呈三角形分布(例如TO-5)可任意旋轉或翻轉,只要在裝配時把中間腳彎折到不同側即可適應。如果三腳呈直線分布(例如TO-126),也可任意旋轉或翻轉,但若裝有散熱片,您就必須在旋轉或翻轉前考慮好散熱片的安裝位置。對于無特殊要求的直線排列的多腳元件(如SIP9)和兩腳元件(如RB.2/.4)的放置無任何要求。

問 PROTEL能否設計單面板?

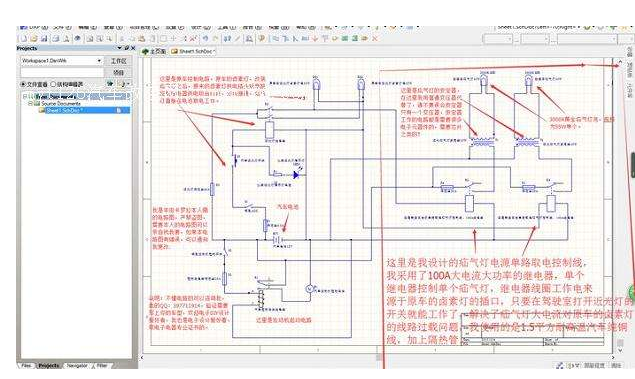

答 可以,但較困難。對此本人也在摸索中,愿提供幾條思路共同探討。(1)簡單的印板可考慮在PROTEL中手工布線(Auto-Manual Route);(2)自動布線前(Auto-Auto Route-All)關閉頂層(Top)、關閉過孔選項(在Options-Preferences所調出對話框中的“AutoVia”選項)。另外,在“Auto-SetupAutoRoute”調出的對話框中將底層(Bottom)的走線方式取為“NoPreference”,同時關閉此對話框中的“LineProbe”選項;(3)盡量選用表面焊裝器件,對插裝類元件,應通過“批處理”方式把所有焊盤的通孔(Multi-Layer)屬性改為單面(Bottom Layer)特性;(4)實在無法避免而被自動布置在TopLayer的少量走線可用手工編輯方式將它引到BottomLayer,殘存少量無法這樣編輯的可刪除,用額外設置的焊盤連上“飛線”代替之。

電子發燒友App

電子發燒友App

評論