PCB設(shè)計(jì)是硬件工程師的必備技能之一。現(xiàn)在,工程師常常面臨的局面是產(chǎn)品功能越來(lái)越強(qiáng)大,而尺寸越來(lái)越小,設(shè)計(jì)周期越來(lái)越短的挑戰(zhàn)。如果有非常強(qiáng)大的PCB設(shè)計(jì)技能在身,相信肯定可以輕松搞定。

PCB設(shè)計(jì),僅僅是開(kāi)始

走出誤區(qū),PCB設(shè)計(jì)、功能實(shí)現(xiàn),僅僅完成30%的工作。

很多同學(xué)會(huì)認(rèn)為硬件設(shè)計(jì)指的是電路設(shè)計(jì),這樣說(shuō)也沒(méi)問(wèn)題的,因?yàn)槟闼械墓ぷ鞫际菄@電路設(shè)計(jì),最終的目標(biāo)也是產(chǎn)出一個(gè)優(yōu)秀的電路,能夠滿足各種要求,經(jīng)歷各種考驗(yàn)。但實(shí)際上我們要求的是產(chǎn)品,而不是單板。

真正的硬件設(shè)計(jì)就是根據(jù)產(chǎn)品經(jīng)理的需求PRS(Product Requirement Specification),在滿足性價(jià)比的要求下,利用目前業(yè)界成熟的芯片方案或者技術(shù),在規(guī)定時(shí)間內(nèi)完成符合:要求的硬件產(chǎn)品(注意:是產(chǎn)品,而不是開(kāi)發(fā)板)。

√ PRS功能(Function)

√ 電源設(shè)計(jì)(Power Supply)

√ 功耗(Power Consumption)

√ 散熱(Thermal/Cooling)

√ 噪音(Noise)

√ 信號(hào)完整性(Signal Integrity)

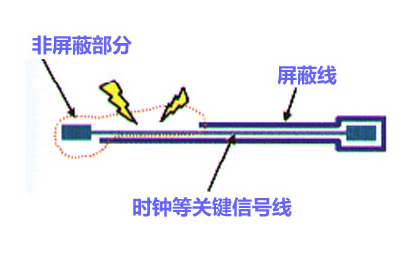

√ 電磁輻射(EMC/EMI)

√ 安規(guī)(Safet)

√ 器件采購(gòu)(Component Sourcing)

√ 可靠性(Reliability)

√ 可測(cè)試性(DFT: design for test)

√ 可生產(chǎn)性(DFM:design for manufacture)

可以看到,一個(gè)成功的硬件設(shè)計(jì),主要功能的實(shí)現(xiàn)只是所有環(huán)節(jié)中的一小部分。剛開(kāi)始工作的時(shí)候,覺(jué)得板子電路設(shè)計(jì)完就完成了50%工作,PCB回板主要功能都能實(shí)現(xiàn)了,那就完成了80%的工作。實(shí)際上不是的,PCB回板主要功能都實(shí)現(xiàn)了,連30%工作都沒(méi)有。所以不管是時(shí)間上,還是階段上,產(chǎn)品的硬件設(shè)計(jì)是一個(gè)漫長(zhǎng)的過(guò)程。

工程師技能要求

初級(jí)硬件工程師技能要求:

熟悉模擬電路、數(shù)字電路知識(shí),熟悉常用電子元器件特性

熟悉PCB設(shè)計(jì)流程和規(guī)范,熟悉Altium Designer等EDA軟件

熟練使用測(cè)試儀器(示波器、萬(wàn)用表、烙鐵、焊臺(tái)、邏輯分析儀等)

熟悉嵌入式硬件架構(gòu)和通用硬件接口(RAMNAND FLASHEMMCUSBDVIHDMICANI2CI2SUARTLCDLVDS等)

熟悉電子產(chǎn)品開(kāi)發(fā)流程、生產(chǎn)工藝流程

中級(jí)硬件工程師技能要求:

精通STM32、ARM、DSP、FPGA等處理器硬件設(shè)計(jì)

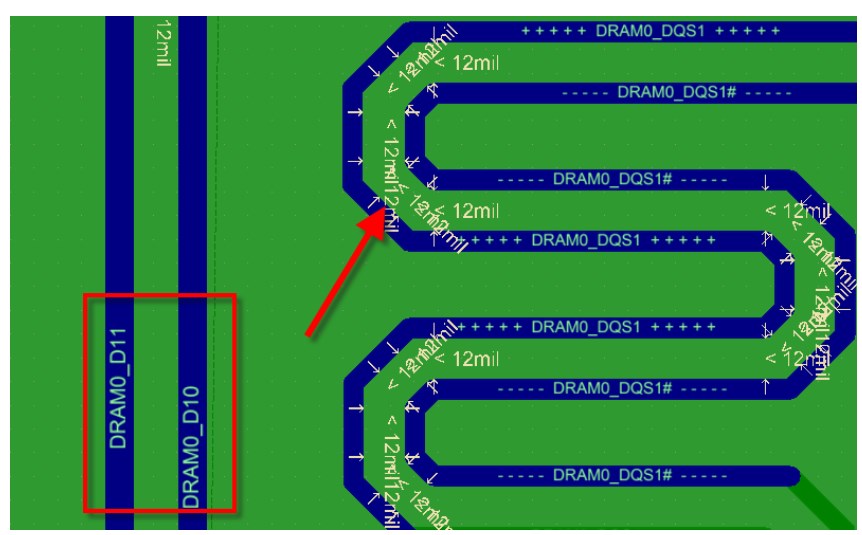

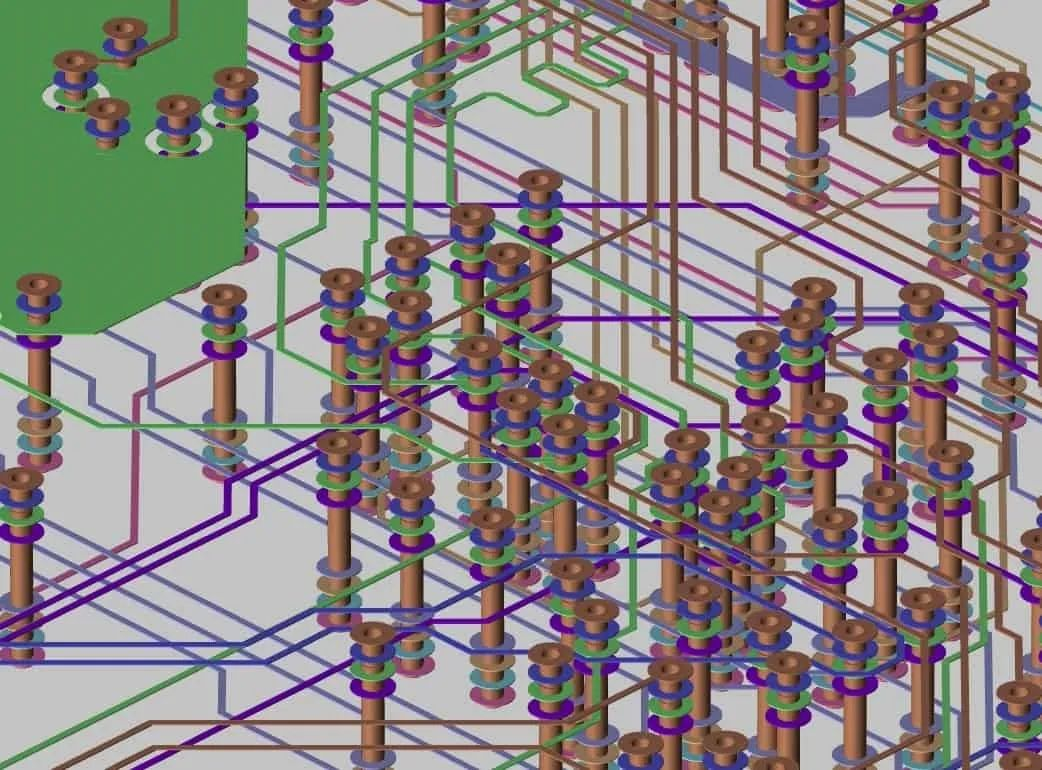

具有高速數(shù)字電路,熟練進(jìn)行六層或以上層數(shù)的PCB設(shè)計(jì),有豐富的PCB設(shè)計(jì)經(jīng)驗(yàn)

獨(dú)立完成硬件產(chǎn)品的原理圖設(shè)計(jì)、PCB設(shè)計(jì)、調(diào)試、順利閱讀器件datasheet

熟悉硬件電路可靠性設(shè)計(jì)和測(cè)試方法,具備RF、SI、PI、EMC的相關(guān)知識(shí)

負(fù)責(zé)產(chǎn)品生命周期的硬件開(kāi)發(fā)工作,包括攢寫(xiě)設(shè)計(jì)規(guī)格書(shū)、詳細(xì)設(shè)計(jì)方案、硬件測(cè)試以及產(chǎn)品的維修指導(dǎo)書(shū)等工作

高級(jí)硬件工程師技能要求:

負(fù)責(zé)硬件產(chǎn)品的戰(zhàn)略規(guī)劃

完成產(chǎn)品的開(kāi)發(fā)、測(cè)試、版本管理、評(píng)審發(fā)布、產(chǎn)品上線等相關(guān)工作

負(fù)責(zé)與外觀、模具、元器件、制板、焊接、外包裝、組裝、配件等第三方合作廠商深度溝通

為產(chǎn)品研發(fā)團(tuán)隊(duì)擬定明確有競(jìng)爭(zhēng)力的產(chǎn)品方向,并能夠統(tǒng)籌和推動(dòng)研發(fā)執(zhí)行

持續(xù)關(guān)注并研究行業(yè)前沿技術(shù),挖掘新技術(shù)在產(chǎn)品上實(shí)施的可行性,以保證產(chǎn)品在技術(shù)上的持續(xù)創(chuàng)新

負(fù)責(zé)軟硬資源整合,把控產(chǎn)品的品質(zhì)管理、生產(chǎn)成本等

優(yōu)秀PCB工程師特征:好的PCB設(shè)計(jì)考慮的技術(shù)方面眾多,包括電路性能、DFX、熱設(shè)計(jì)、EMC設(shè)計(jì)、信號(hào)完整性、電源完整性、結(jié)構(gòu)設(shè)計(jì)、可靠性、成本等諸多方面,甚至也需要考慮布局美觀。

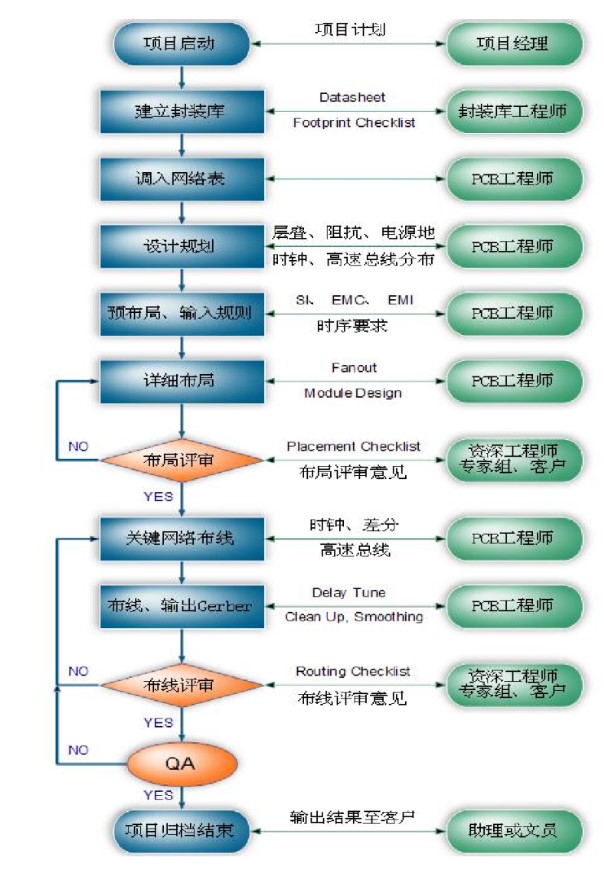

高速PCB設(shè)計(jì)流程

高速PCB設(shè)計(jì)流程:

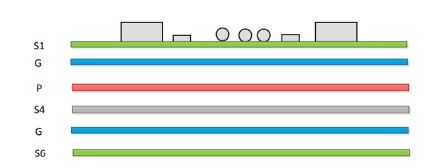

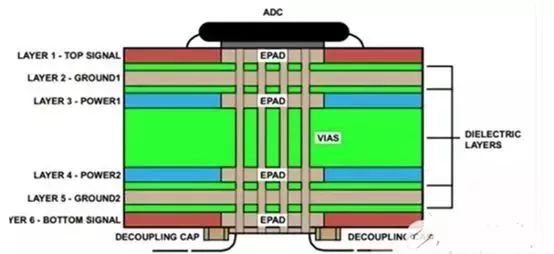

PCB疊層理論基礎(chǔ)?

多層板層疊的一般原則:

1)元件面相鄰層為地平面(屏蔽和提供連續(xù)的參考平面);2)所有的信號(hào)層盡可能與地平面相鄰;3)盡量避免兩個(gè)信號(hào)層直接相鄰;4)主電源盡可能與其對(duì)應(yīng)地相鄰;5)兼顧層壓結(jié)構(gòu)結(jié)構(gòu); (翹曲度<0.75%)

6)采用偶數(shù)層結(jié)構(gòu);(制造工藝,成本,層壓,翹曲度)

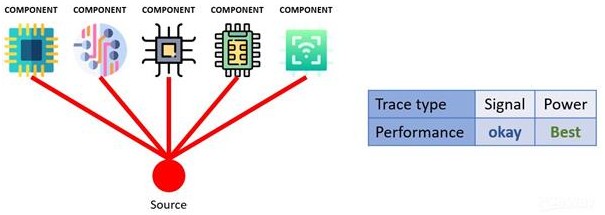

地和電源平面實(shí)現(xiàn)3個(gè)功能:為數(shù)字信號(hào)的轉(zhuǎn)換提供穩(wěn)定的參考電壓、為所有的邏輯器件分配電源、控制信號(hào)之間的串?dāng)_。

在低速電路中,電流沿著最小電阻路徑前進(jìn);在高速電路里、高速電流沿著最小電感路徑前進(jìn)。

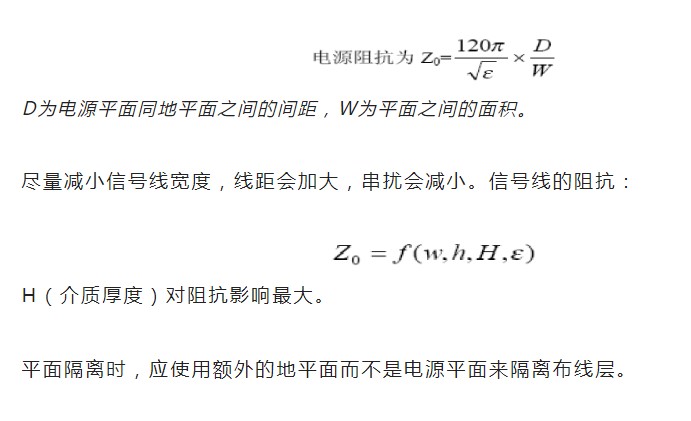

電源的對(duì)地阻抗應(yīng)該最低:

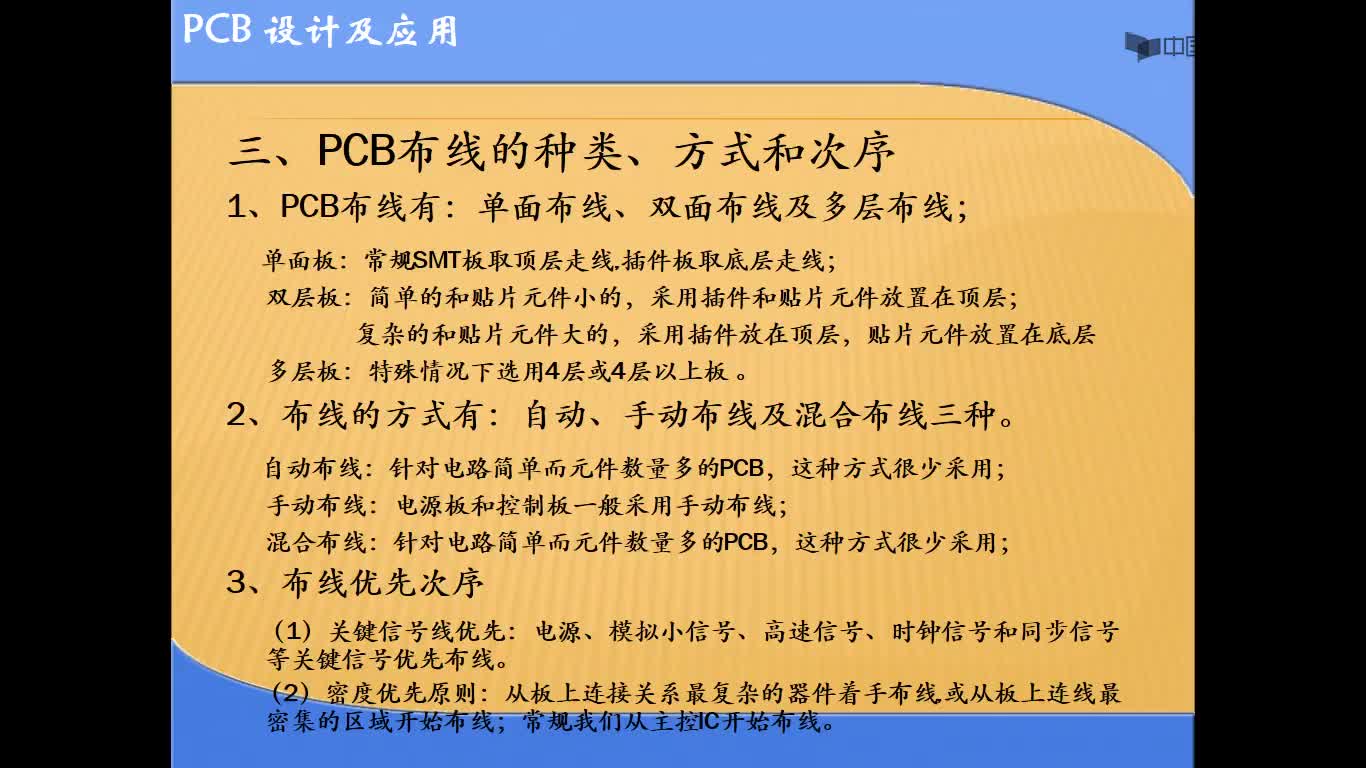

高速PCB布局設(shè)計(jì)技巧

布局的好壞往往決定著單板的成敗!

快速模塊化,高速PCB布局常用的一種方法,根據(jù)原理圖把一個(gè)個(gè)小功能模塊布好后再往板內(nèi)整體布局;分清主次,需要特殊處理的地方要提前考慮。

除此之外,還包含交互式布局、飛線引導(dǎo)布局法、Net標(biāo)注法、位號(hào)居中、以及各種結(jié)構(gòu)件對(duì)齊。

好的設(shè)計(jì)習(xí)慣是PCB一板成功的基礎(chǔ):

1)優(yōu)先規(guī)劃地平面和電源平面

2)先打孔、后走線:布線時(shí)候盡量避免過(guò)孔讓線,漏打孔是初級(jí)設(shè)計(jì)師經(jīng)常容易犯的問(wèn)題之一,比如濾波電容。

設(shè)計(jì)驗(yàn)證

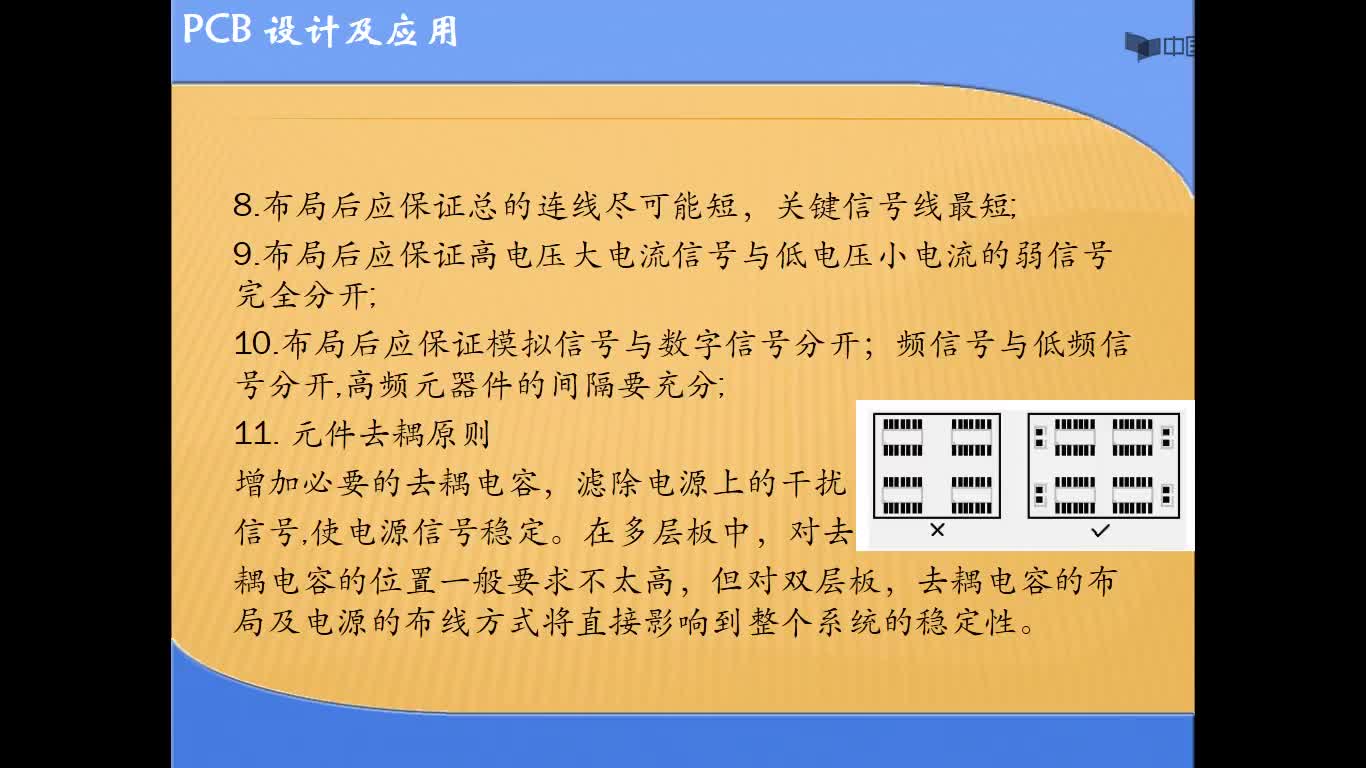

1)檢查整板濾波電容、去耦電容的設(shè)計(jì)

2)檢查每路電源的電源平面是否存在瓶頸

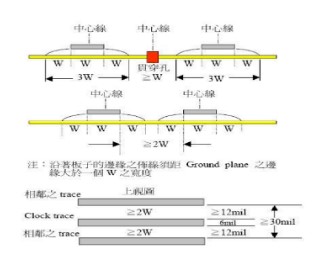

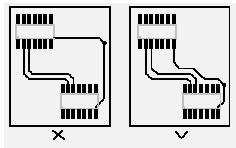

3)3W原則,PCB設(shè)計(jì)中為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持大部分電場(chǎng)不互相干擾

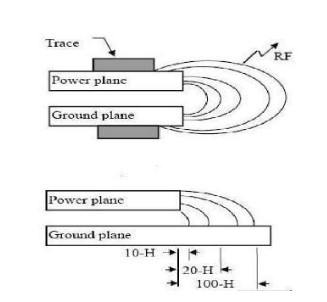

4)20H原則:指電源層相對(duì)地層內(nèi)縮20H的距離,這是為了抑制邊緣輻射效應(yīng)。在板的邊緣會(huì)向外輻射電磁干擾。將電源層內(nèi)縮,使得電場(chǎng)只在接地層的范圍內(nèi)傳導(dǎo)。

5)環(huán)繞地設(shè)計(jì),地空越多越好,使每一層緊密的連接在一起

6)跨島處理,在 PCB 設(shè)計(jì)過(guò)程中,由于平面的分割,可能會(huì)導(dǎo)致信號(hào)參考平面不連續(xù),對(duì)于低頻信號(hào),可能沒(méi)什么關(guān)系,而在高頻數(shù)字系統(tǒng)中,高頻信號(hào)以參考平面作返回路徑,即回流路徑,如果參考平面不連續(xù),信號(hào)跨分割,這就會(huì)帶來(lái)諸多的問(wèn)題,如 EMI、串?dāng)_等問(wèn)題。這種情況下,需要對(duì)分割進(jìn)行縫補(bǔ),為信號(hào)提供較短的回流通路。

常見(jiàn)的跨島處理方式:添加縫補(bǔ)電容(Stiching Capacitor),跨線橋接。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論