在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。##在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵

2016-04-26 14:00:01 5104

5104

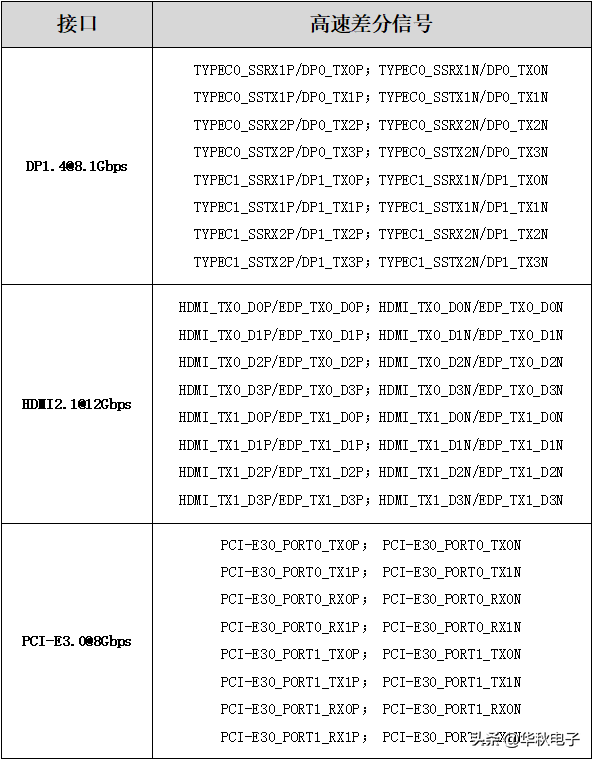

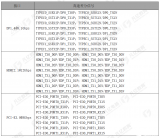

接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進(jìn)行PCB布線設(shè)計(jì)。 高速信號布線時(shí)盡量少打孔

2023-08-02 08:41:11 1432

1432

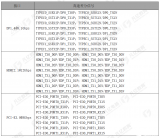

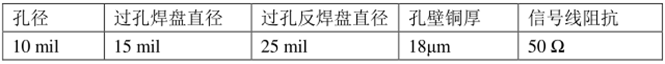

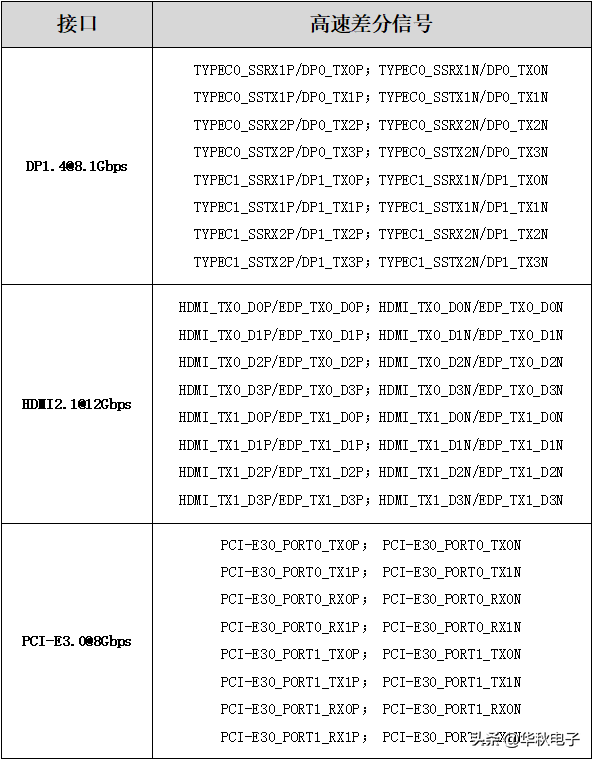

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進(jìn)行PCB布線設(shè)計(jì)。 高速信號布線時(shí)盡量

2023-08-01 18:10:06 1263

1263

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進(jìn)行PCB布線設(shè)計(jì)。 高速信號布線時(shí)盡量

2023-08-03 17:13:35 644

644

向大神請教:在設(shè)計(jì)一個(gè)10層板PCB時(shí),一些關(guān)鍵信號需要做阻抗匹配,對于如何選擇參考層有一些不明白,如下:1、中間信號層5做阻抗匹配時(shí),是否可以選用電源層4和電源層7共同作為參考層?2、TOP信號層1某些信號做阻抗匹配時(shí),是否可選用信號層3作為參考層?層疊示意圖

2022-04-24 11:23:09

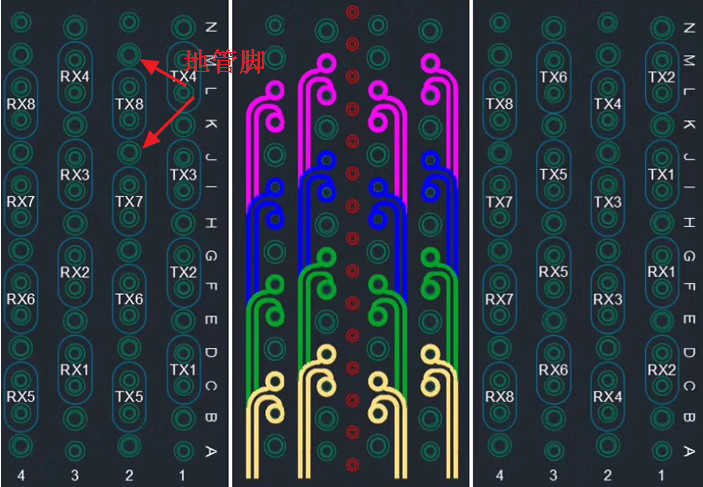

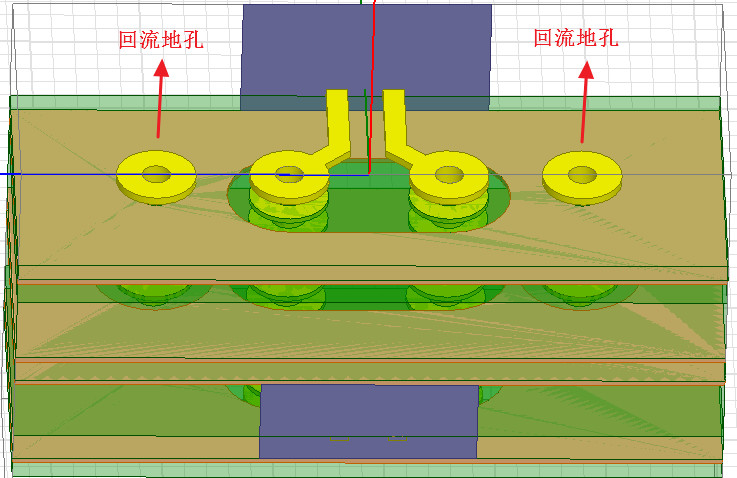

。最后再放置小的元器件。 3、差分打孔換層處添加回流地孔,且盡可能減少打孔換層,點(diǎn)對點(diǎn)連接 4、對于相同的模塊,采取復(fù)用設(shè)計(jì),保持走線扇出一致性,整齊且美觀。 5.考慮整板空間,及布局布線通道分析

2023-04-19 15:39:07

打開通道走線,需先經(jīng)過TVS去除整板下部眾多電源區(qū)域以及外部接口拔插可能帶來的電源干擾及靜電干擾。 高速信號組采取完整包地處理,嚴(yán)格控制信號誤差,對于打孔換層處增加回流地過孔,考慮到空間的原因,未采取立體

2023-04-19 15:23:50

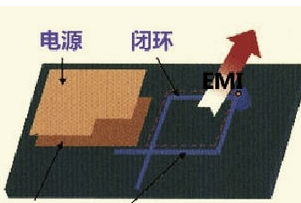

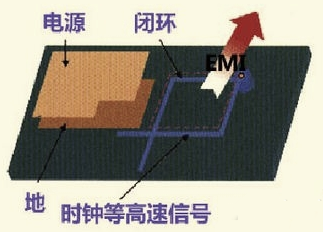

規(guī)則一:高速信號走線屏蔽規(guī)則在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。圖1 高速

2018-11-28 11:14:18

信號打孔換層的幾種情況分析

2021-02-26 08:02:45

我想問下你們用什么給PCB打孔啊網(wǎng)購打孔機(jī)不太好用軸心偏移啊你們用什么工具啊

2012-08-26 10:44:11

夾雜在差分信號之間的非查份(單獨(dú)一條)走線方式有什么要求嗎?這就是要畫的連接線PCB高速差分信號線四層怎么弄,還要求阻抗,就是一個(gè)連接線

2023-04-07 17:46:45

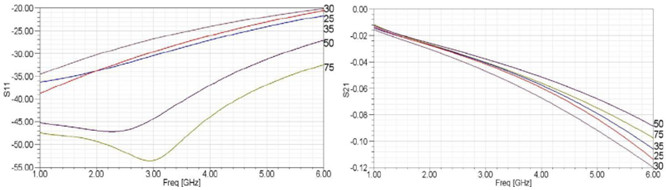

4.3.3 實(shí)驗(yàn)設(shè)計(jì)3:4層PCB 本章將考慮4層PCB疊層的幾種不同變體。這些變化中最簡單的是基于實(shí)驗(yàn)設(shè)計(jì)2層疊層(第4.3.2節(jié)),外加兩個(gè)額外的內(nèi)部信號層。假設(shè)附加層主要由許多較薄的信號

2023-04-20 17:10:43

高速的情況下,可以加入多余的地層來隔離信號層,多個(gè)地敷銅層可以有效地減小PCB的阻抗,減小共模EMI。但建議盡量不要多加電源層來隔離,這樣可能造成不必要的噪聲干擾。4)系統(tǒng)中的高速信號應(yīng)該在內(nèi)層且在兩個(gè)

2016-05-17 22:04:05

和地層之間應(yīng)該緊密耦合)在設(shè)計(jì)時(shí)需要首先得到滿足,另外如果電路中需要傳輸高速信號,那么設(shè)計(jì)原則 3(電路中的高速信號傳輸層應(yīng)該是信號中間層,并且夾在兩個(gè)內(nèi)電層之間)就必須得到滿足。10層板PCB典型10層

2016-08-24 17:28:39

的放置位置以及如何在這些層上分布不同的信號。這就是多層PCB層疊結(jié)構(gòu)的選擇問題。 層疊結(jié)構(gòu)是影響PCB板EMC性能的一個(gè)重要因素,也是抑制電磁干擾的一個(gè)重要手段。本文介紹多層PCB板層疊結(jié)構(gòu)的相關(guān)內(nèi)容

2018-09-17 17:41:10

打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時(shí),應(yīng)加大收發(fā)信號之間的布線距離。

針對以上高速信號還有如下方面的要求:

一、BGA焊盤區(qū)域挖

2023-08-01 18:02:03

線路板層數(shù)可分為單面板、雙面板、四層板、六層板以及其他多層線路板。PCB電路板生產(chǎn)過程中需要經(jīng)過打孔的工序,現(xiàn)有的PCB電路板打孔裝置打孔時(shí)直接作用于電路板,會(huì)對PCB電路板造成一定損傷,導(dǎo)致打孔

2020-09-16 11:35:07

PCB經(jīng)驗(yàn)淺談

2012-08-04 09:33:39

protel99se繪制pcb過程中用+-換層之前可以使用,現(xiàn)在不知道怎么設(shè)置了一下換不了了。各位高人請指教怎么設(shè)置回來?謝謝

2012-07-31 11:13:33

夠預(yù)測到你的設(shè)計(jì)質(zhì)量會(huì)怎么樣,而且一樣的設(shè)計(jì)放在不同的板子也會(huì)千差萬別。而且最重要的是并不是包了地就一定會(huì)帶來信號質(zhì)量的改善,很多情況下你辛辛苦苦包完了,結(jié)果只換來“事倍功半”這幾個(gè)字。好了,說了

2019-05-30 07:22:08

PCB設(shè)計(jì)電源審查電源審查出發(fā)點(diǎn):1.通流(電源平面及換層過孔)2.反饋信號3.濾波電容細(xì)則:檢查電源通流是否滿足,綜合考慮通流/壓降/紋波是否滿足設(shè)計(jì)要求。多層板特別注意換層過孔的個(gè)數(shù),避免出現(xiàn)換

2021-12-28 06:58:48

線都要有(保持對稱性),信號線換層后參考層也要在靠近信號線的過孔處打孔換層。 MIPI差分走線的設(shè)計(jì)中最重要的規(guī)則就是匹配線長,其它的規(guī)則都可以根據(jù)設(shè)計(jì)要求和實(shí)際應(yīng)用靈活處理。 各類信號布線

2023-04-12 15:08:27

信號層提供屏蔽。(2)內(nèi)部電源層和地層之間應(yīng)該緊密耦合,也就是說,內(nèi)部電源層和地層之間的介質(zhì)厚度應(yīng)該取較小的值,以提高電源層和地層之間的電容,增大諧振頻率。(3)電路中的高速信號傳輸層應(yīng)該是信號中間層

2015-02-11 16:25:13

在一般的非高速PCB設(shè)計(jì)中,我們都是認(rèn)為電信號在導(dǎo)線上的傳播是不需要時(shí)間的,就是一根理想的導(dǎo)線,這種情況在低速的情況下是成立的,但是在高速的情況下,我們就不能簡單的認(rèn)為其是一根理想的導(dǎo)線了,電信號

2019-05-30 06:59:24

淺談三層架構(gòu)原理

2022-01-16 09:14:46

的放置位置以及如何在這些層上分布不同的信號。這就是多層PCB層疊結(jié)構(gòu)的選擇問題。 層疊結(jié)構(gòu)是影響PCB板EMC性能的一個(gè)重要因素,也是抑制電磁干擾的一個(gè)重要手段。本文介紹多層PCB板層疊結(jié)構(gòu)的相關(guān)內(nèi)容

2018-08-24 06:48:42

淺談射頻PCB設(shè)計(jì)

2019-03-20 15:07:57

淺談電子三防漆對PCB板的作用有哪些?

2023-04-14 14:36:27

多層PCB通常用于高速、高性能的系統(tǒng),其中一些層用于電源或地參考平面,這些平面通常是沒有分割的實(shí)體平面。無論這些層做什么用途,電壓為多少,它們將作為與之相鄰的信號走線的電流返回路徑。構(gòu)造一個(gè)好

2018-11-27 15:14:59

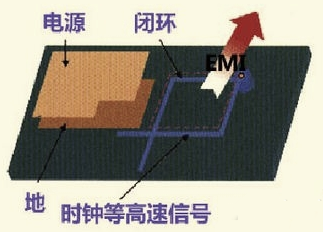

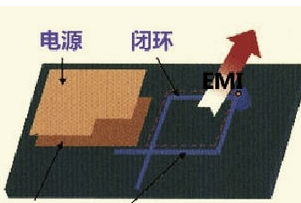

屏蔽了部分,都是會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。規(guī)則二、高速信號的走線閉環(huán)規(guī)則 由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現(xiàn)這種失誤

2022-04-18 15:22:08

,每1000mil,打孔接地。規(guī)則二、高速信號的走線閉環(huán)規(guī)則由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現(xiàn)這種失誤,如下圖所示:由于PCB板的密度越來越高,很多

2021-03-31 06:00:00

=D2+0.416.在信號換層的過孔附近放置一些接地過孔,以便為信號提供短距離回路。總的來說,在PCB設(shè)計(jì)時(shí)不僅要靈活多變,還要均衡考慮過孔減小帶來的成本增加以及PCB 廠家后期加工和工藝技術(shù)的限制。

2016-12-20 15:51:03

1.在top和bottom的覆銅區(qū)域上每隔1/20波長的距離打孔接地。2.減小傳輸線分布電感,增加分布電容。即減少Z0。3.當(dāng)信號換層時(shí),如果參考平面是GND1和GND2,那么在信號過孔的旁邊多打

2015-03-06 10:20:26

高速PCB設(shè)計(jì)的疊層問題

2009-05-16 20:51:30

本期講解PCB設(shè)計(jì)中高速信號關(guān)鍵信號的布線要求。一、時(shí)鐘信號布線要求在數(shù)字電路設(shè)計(jì)中,時(shí)鐘信號是一種在高態(tài)與低態(tài)之間振蕩的信號,決定著電路的性能。時(shí)鐘電路在數(shù)字電路中點(diǎn)有重要地位,同時(shí)又是產(chǎn)生

2017-10-19 14:25:36

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地

2016-01-19 22:50:31

內(nèi)層有地、信號線、電源,下面通過1.6mm板厚幾個(gè)疊層結(jié)構(gòu),分析哪種結(jié)構(gòu)最合適。 首先,介紹一下PCB線路板廠采用較多的六層板的普通結(jié)構(gòu),此結(jié)構(gòu)使用于普通無高速信號的PCB板。(華秋電路現(xiàn)六層板免費(fèi)打

2019-10-16 18:03:20

結(jié)構(gòu)設(shè)計(jì)時(shí),會(huì)出現(xiàn)以下幾種情況:1、電源層與地層相鄰:電源層與地層相鄰可以很好的實(shí)現(xiàn)電源與地之間的耦合,減小電源平面與地平面見的阻抗。2、信號層與地層相鄰:以完整的地層作為參考平面,信號回流路徑最好。3

2020-12-21 09:23:34

問:使用高速轉(zhuǎn)換器時(shí),有哪些重要的PCB布局布線規(guī)則? 答:本RAQ的第一部分討論了為什么AGND和DGND接地層未必一定分離,除非設(shè)計(jì)的具體情況要求您必須這么做。第二部分討論印刷電路板(PCB

2018-09-12 15:05:36

1、單個(gè)元件換層 選中需要換層的元件,英文輸入下按 “L”2、批量把一些元件從頂層換到底層 把要換到底層的元件全部選中,然后在pcb inspector 中l(wèi)ayer 欄中的top

2015-01-27 10:12:05

、高速信號走線屏蔽規(guī)則如上圖所示:在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,則需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。2...

2021-12-31 06:22:08

,過孔會(huì)造成線路阻抗的不連續(xù),在每次打孔換層的地方加一對回流地過孔,用于信號回流換層,如圖3所示。圖3 差分打孔換層處添加GND孔⑥若USB兩邊定位柱接的是保護(hù)地,分割的時(shí)候保證與GND的距離是2MM,并在保護(hù)地區(qū)域多打孔,保證充分連接,并用磁珠與GND進(jìn)行跨接,如圖4。?圖4 USB保護(hù)地的隔離`

2019-03-07 14:18:56

畫表面粘式的,上下兩層是信號層,中間兩層一層是電源層一層是接地層。以前從沒畫過表面粘的。。。急死了。。畫多層表面粘的PCB需要注意哪些?在這里向各位PROTEL達(dá)人請教。有認(rèn)識(shí)PROTEL DXP

2008-10-15 11:21:37

打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時(shí),應(yīng)加大收發(fā)信號之間的布線距離。

針對以上高速信號還有如下方面的要求:

01

BGA焊盤區(qū)域挖

2023-08-03 18:18:07

本文主要介紹多層PCB設(shè)計(jì)疊層的基礎(chǔ)知識(shí),包括疊層結(jié)構(gòu)的排布一般原則,常用的疊層結(jié)構(gòu),疊層結(jié)構(gòu)的改善案例分析。回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:06:58

`兩層pcb器件換層是不是雙擊該器件然后把頂層改為底層就OK啦該器件會(huì)變成暗色`

2011-08-31 13:58:58

帶來的影響越來越嚴(yán)重,其傳輸性能逐漸被帶狀線超過。板材的DF值越低,微帶線落后就越大。在實(shí)際的高速PCB設(shè)計(jì)中,綠油帶來的損耗不可忽視,在已選用高速板材的情況下,通常建議長距離傳輸?shù)?b class="flag-6" style="color: red">高速信號走在

2020-03-09 10:57:00

降低,故將損害質(zhì)量。 使用偶數(shù)層PCB 當(dāng)設(shè)計(jì)中出現(xiàn)奇數(shù)層PCB時(shí),用以下幾種方法可以達(dá)到平衡層疊、降低PCB制作成本、避免PCB彎曲。以下幾種方法按優(yōu)選級排列。 1.一層信號層并利用。如果設(shè)計(jì)PCB

2018-08-23 15:34:37

:較優(yōu)的層疊 除了上面所提到的幾種利用多層板提升PCB信號傳輸可靠性的方法外,還有一部分權(quán)威資料顯示,同種材料時(shí)四層板要比雙面板的噪聲低20dB。引線彎折越少越好,最好采用全直線,需要轉(zhuǎn)折,可用45度

2023-04-19 16:05:28

本文主要分析一下在高速PCB設(shè)計(jì)中,高速信號與高速PCB設(shè)計(jì)存在一些理解誤區(qū)。誤區(qū)一:GHz 速率以上的信號才算高速信號? 提到“高速信號”,就需要先明確什么是“高速”,MHz 速率級別的信號算高速

2022-04-28 16:21:41

止信號在媒質(zhì)終端發(fā)生反射,同時(shí)應(yīng)減少電磁干擾以保證信號的完整性。在PCB布線時(shí)需要注意的一些問題如下。(1)采用多層板結(jié)構(gòu)形式,由于LVDS信號屬于高速信號,故與其相鄰的層應(yīng)為地層,且應(yīng)對LVDS信號

2017-07-18 10:57:28

通用的高速信號PCB設(shè)計(jì)處理原則有:(1)層面的選擇:處理高速信號優(yōu)先選擇兩邊是GND的層面處理(2)處理時(shí)要優(yōu)先考慮高速信號的總長(3)高速信號Via數(shù)量的限制:高速信號允許換一次層,換層時(shí)加

2017-02-07 09:40:04

之間、與信號之間的干擾,避免幾種信號平行布線,必要時(shí)采用GND屏蔽層包裹隔離,不同時(shí)鐘或信號之間間距 30mil以上,可放在GND和VCC層之間 (3)時(shí)鐘信號盡量不采用跨界分割平面 (4)若時(shí)鐘線有過

2019-05-21 09:34:14

在高速PCB設(shè)計(jì)中,信號層的空白區(qū)域可以敷銅,而多個(gè)信號層的敷銅在接地和接電源上應(yīng)如何分配?

2009-09-06 08:39:35

請教各位在布板時(shí)PCB上過大電流的銅箔上,大伙都是如何進(jìn)行處理的 是密集打孔 進(jìn)行散熱,均勻分布電流 還是少打孔, 只是讓電流過TOP層與BOTTOM層,盡量保持銅箔的完整性呢 還有一個(gè)問題就是有關(guān)

2019-04-08 15:48:50

解決高速PCB設(shè)計(jì)信號問題的全新方法

2021-04-25 07:56:35

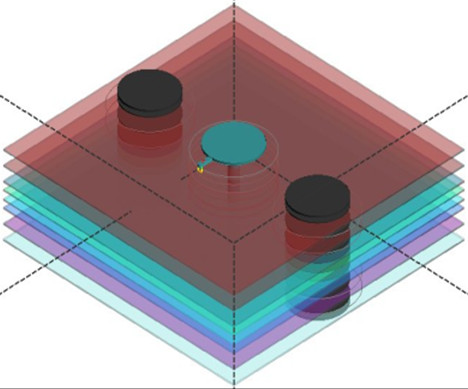

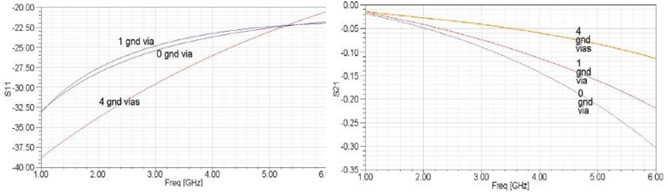

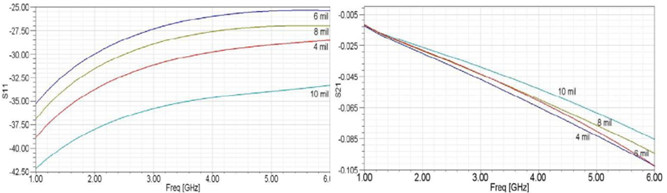

作者:一博科技高速先生自媒體成員 黃剛PCB工程師:“沒有層走了,這幾對10G信號要多換幾次層,要打4次過孔才能走過去啊!”SI工程師:“……”不知道粉絲里面做PCB設(shè)計(jì)的朋友們有沒有上面所說的困難

2021-10-22 11:44:57

1、表層走線長度不能太長,很多板要求不能大于500mil。圖12、在打孔換層的地方要加一對gnd孔,高速孔到回流孔間距是40mil,在平面層要做反焊盤,串的小電容和BGA內(nèi)要在對應(yīng)的2層做反焊盤

2016-11-07 16:22:26

參考平面時(shí),由于本身及過孔的寄生電感存在,仍然會(huì)產(chǎn)生一定的電磁輻射和信號衰減,所以設(shè)計(jì)者頭腦里要有一個(gè)正確的指導(dǎo)思想:盡量少換層走線,換層后盡量保持信號靠近同一(或者同屬性)的參考平面。 PCB板上器件

2019-05-20 08:30:00

最近要搞告訴信號的東西,但是從來沒有布過高速信號的PCB,求大神指教

2013-08-30 14:10:03

。高速打孔機(jī)系統(tǒng)用途:高速打孔機(jī)機(jī),廣泛運(yùn)用于印刷包裝、電子印刷、銘牌標(biāo)牌等行業(yè)印后對位孔沖孔!高速打孔機(jī)使用領(lǐng)域:PCB線路板、FPC軟板、IMD/IML、菲林,重氮片,手機(jī)面板,手機(jī)按鍵,不干膠

2021-04-23 10:27:34

回流用的,而信號是用電感的方式回流,所以參考層只要在電源回路里就OK,與是 GND 還是PWR無關(guān)。參考層是信號回流用的,參考電位是用來讀取信號值的,一般會(huì)選 GND,不能把參考層和參考電位混淆。3、如果在芯片內(nèi)部信號參考的是電源,那么在PCB上參考電源會(huì)比較好,但多數(shù)芯片設(shè)計(jì)中高速信...

2021-12-27 07:10:09

網(wǎng)絡(luò),在多層的PCB走線的時(shí)候一旦產(chǎn)生了開環(huán)的結(jié)果,將產(chǎn)生線形天線,增加EMI的輻射強(qiáng)度。 圖3 開環(huán)規(guī)則 規(guī)則四:高速信號的特性阻抗連續(xù)規(guī)則 高速信號,在層與層之間切換的時(shí)候必須保證特性阻抗

2018-09-20 10:38:01

實(shí)現(xiàn),在向里的2-3圈Pin需要就地打孔扇出,走線基本上要走L3或L4或Bottom層。4、對此運(yùn)行400MHz的高速數(shù)字電路系統(tǒng)多層板,應(yīng)不應(yīng)當(dāng)進(jìn)行信號完整性分析及如何分析。5、PCB的疊層順序。6

2011-10-21 09:48:17

的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。規(guī)則二:高速信號的走線閉環(huán)規(guī)則由于PCB板的密度越來越高

2017-11-02 12:11:12

請問一下在拖動(dòng)Pcb器件的時(shí)候?qū)崿F(xiàn)快速換層的快捷鍵是什么啊?

2019-05-16 07:35:10

走多根線換層能同時(shí)打孔嗎?差分走線換層能同時(shí)過孔嗎?

2019-05-30 05:35:36

需要傳輸高速信號,那么設(shè)計(jì)原則 3(電路中的高速信號傳輸層應(yīng)該是信號中間層,并且夾在兩個(gè)內(nèi)電層之間)就必須得到滿足。 10層板 PCB典型10層板設(shè)計(jì) 一般通用的布線順序是TOP--GND---

2016-08-23 10:02:30

1.2mm,這需要考慮機(jī)械結(jié)構(gòu)的要求,一般情況下無法實(shí)現(xiàn)。其實(shí),明眼人會(huì)說上面的所有方案都是有局限性的:信號較雜亂,必須要4個(gè)布線層才能完成布線有高密的BGA,無法走較寬的線速率較高,DDR3/4,高速串行總線,控其他阻抗擔(dān)心有風(fēng)險(xiǎn)

2019-05-30 07:20:55

1.2mm,這需要考慮機(jī)械結(jié)構(gòu)的要求,一般情況下無法實(shí)現(xiàn)。其實(shí),明眼人會(huì)說上面的所有方案都是有局限性的:信號較雜亂,必須要4個(gè)布線層才能完成布線有高密的BGA,無法走較寬的線速率較高,DDR3/4,高速串行總線,控其他阻抗擔(dān)心有風(fēng)險(xiǎn)

2022-03-07 16:04:23

需要考慮機(jī)械結(jié)構(gòu)的要求,一般情況下無法實(shí)現(xiàn)。其實(shí),明眼人會(huì)說上面的所有方案都是有局限性的:信號較雜亂,必須要4個(gè)布線層才能完成布線有高密的BGA,無法走較寬的線速率較高,DDR3/4,高速串行總線

2019-05-29 07:26:53

化處理加工工藝對信號質(zhì)量有影響PCB 加工過程中,為了提高 PCB 銅皮層與介質(zhì)層的結(jié)合強(qiáng)度,降低 PCB 分層風(fēng)險(xiǎn),都會(huì)有粗化 / 棕化處理工藝,就是通過打磨或者腐蝕的方式使銅皮表面變得粗糙。在高速

2020-11-30 09:51:58

針對Spartan-3E FT256 BGA封裝的四層和六層高速PCB設(shè)計(jì)本應(yīng)用指南針對 FT256 1 mm BGA 封裝的 Spartan?-3E FPGA,討論了低成本、四至六層、大批量

2009-10-10 13:06:48

隨著高頻高速電子產(chǎn)品的快速發(fā)展,信號傳輸過程更容易出現(xiàn)反射、串?dāng)_等信號完整性問題,且頻率越高、傳輸速率越快,信號損耗越嚴(yán)重,如何降低信號在傳輸過程中的損耗、保證信號完整性是高頻高速PCB發(fā)展中的巨大

2023-05-26 11:30:36

在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2017-08-25 15:35:24 1869

1869

描述了高速PCB電路板信號完整性設(shè)計(jì)方法。 介紹了信號完整性基本理論, 重點(diǎn)討論了如何采用高速PCB設(shè)計(jì)方法保證高速數(shù)采模塊的信號完整性

2017-11-08 16:55:13 0

0 規(guī)則一 規(guī)則 圖1 如圖1所示,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或者只屏蔽了部分,都會(huì)造成EMI泄漏。建議屏蔽線,每1000mil,打孔接地。 規(guī)則二、高速信號的走線閉環(huán)

2018-09-12 09:10:01 1157

1157 在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 GHz速率級別的信號算高速? 傳統(tǒng)的SI理論對于高速信號有經(jīng)典的定義。 SI:Signal Integrity ,即信號完整性。 SI理論對于PCB互連線路的信號傳輸行為理解,信號邊沿速率幾乎完全決定了信號中的最大頻率成分,通常當(dāng)信號邊沿時(shí)間小于4~6倍的互連傳輸延時(shí)的情況

2019-11-05 11:27:17 10310

10310

規(guī)則一:高速信號走線屏蔽規(guī)則 如上圖所示: 在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會(huì)造成EMI的泄漏。 建議屏蔽線,每1000mil,打孔

2020-02-14 11:53:40 11779

11779 如上圖所示:在PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2

2020-06-05 10:54:04 2839

2839 電子發(fā)燒友網(wǎng)為你提供PCB EMC問題:信號打孔換層的幾種情況資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-30 08:40:04 9

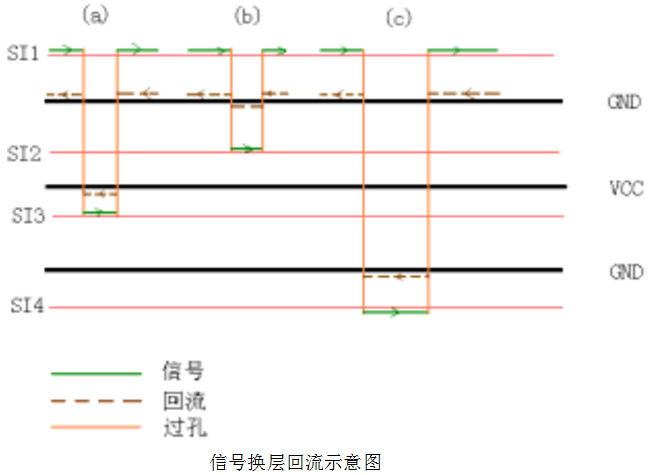

9 換層處過孔不能將信號回路連通起來,將引起信號回路面積增大,從而導(dǎo)致EMC問題。 如下圖所示,描述了信號打孔換層的幾種情況: a、信號線換層,回流路徑也從GND換到VCC上去了; b、信號線換層,但參考面沒改變,回流路徑?jīng)]有換層; c、

2021-05-29 14:32:12 5967

5967

我們都知道,信號打孔換層會(huì)改變信號的回流路徑,如果信號換層,回流路徑也跟著換層,但是在信號換層處過孔不能將信號回路連通起來,將引起信號回路面積增大,從而導(dǎo)致EMC問題。

2022-12-02 09:42:50 1216

1216 信號打孔換層會(huì)改變信號的回流路徑,如果信號換層,回流路徑也跟著換層,但是在信號換層處過孔不能將信號回路連通起來,將引起信號回路面積增大,從而導(dǎo)致EMC問題。

2022-12-02 09:47:21 657

657 解決。 高速信號走線屏蔽規(guī)則 如上圖所示:在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,則需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會(huì)造成EMI的泄漏。 建議屏蔽線每1000mil打孔接地 。 高速信號的走線閉環(huán)規(guī)則 由于PCB板的密度越來越高,很多PCB

2023-05-22 09:15:58 834

834

會(huì)更嚴(yán)格,在“PCBlayout 通用布線規(guī)范”的基礎(chǔ)上,還需要根據(jù)本章節(jié)的要求來進(jìn)行PCB布線設(shè)計(jì)。 表1-1 RK3588 8Gbps及以上差分信號 高速信號布線時(shí)盡量少打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時(shí),應(yīng)加大收發(fā)信號之間的

2023-08-02 07:35:01 423

423

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進(jìn)行PCB布線設(shè)計(jì)。高速信號布線時(shí)盡量少打孔

2023-08-03 17:31:07 662

662

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設(shè)計(jì)要求會(huì)更嚴(yán)格,在前幾篇關(guān)于PCB布線內(nèi)容的基礎(chǔ)上,還需要根據(jù)本篇內(nèi)容的要求來進(jìn)行PCB布線設(shè)計(jì)。 高速信號布線時(shí)盡量

2023-08-03 18:15:02 486

486 PCB高速信號在當(dāng)今的一個(gè)pcb設(shè)計(jì)中顯然已成為主流,一名優(yōu)秀的PCB工程師,除了在實(shí)戰(zhàn)項(xiàng)目慢慢積累設(shè)計(jì)PCB高速信號的經(jīng)驗(yàn)外,還需通過不斷學(xué)習(xí)來提升自己的知識(shí)儲(chǔ)存和專業(yè)技能。本文捷多邦小編就給大家科普一下PCB高速信號的一些相關(guān)布線知識(shí)。

2023-09-15 10:19:18 720

720 對于高速信號,pcb的設(shè)計(jì)要求會(huì)更多,因?yàn)?b class="flag-6" style="color: red">高速信號很容易收到其他外在因素的干擾,導(dǎo)致實(shí)際設(shè)計(jì)出來的東西和原本預(yù)期的效果相差很多。 所以在高速信號pcb設(shè)計(jì)中,需要提前考慮好整體的布局布線,良好的布局

2023-11-06 10:04:04 340

340

在AD中將PCB板打孔是實(shí)現(xiàn)自定義電路布局的一個(gè)重要步驟。本文將為您詳盡、詳實(shí)、細(xì)致地介紹在AD軟件中如何進(jìn)行PCB板打孔的操作,并提供一些實(shí)用的技巧和注意事項(xiàng)。本文將從以下幾個(gè)方面進(jìn)行介紹

2023-12-18 16:54:58 1776

1776 PCB設(shè)計(jì)中,BGA焊盤上可以打孔嗎? 在PCB(印刷電路板)設(shè)計(jì)中,BGA(球柵陣列)焊盤上是可以打孔的。然而,在決定是否將BGA焊盤打孔時(shí)需要考慮一些因素,這些因素包括BGA焊盤的結(jié)構(gòu)、信號

2024-01-18 11:21:48 459

459

電子發(fā)燒友App

電子發(fā)燒友App

評論