天線最終的目的是要將射頻信號輻射到自由空間,這時天線的設計就顯得非常重要,但是天線設計很大程度上依賴于所安裝平臺的特性,另外天線對周圍環境很敏感,這些原因導致很多情況下,天線對每個平臺都是獨一無二的設計。

2016-10-24 11:33:12 81945

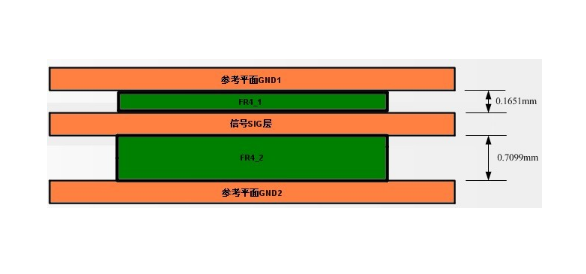

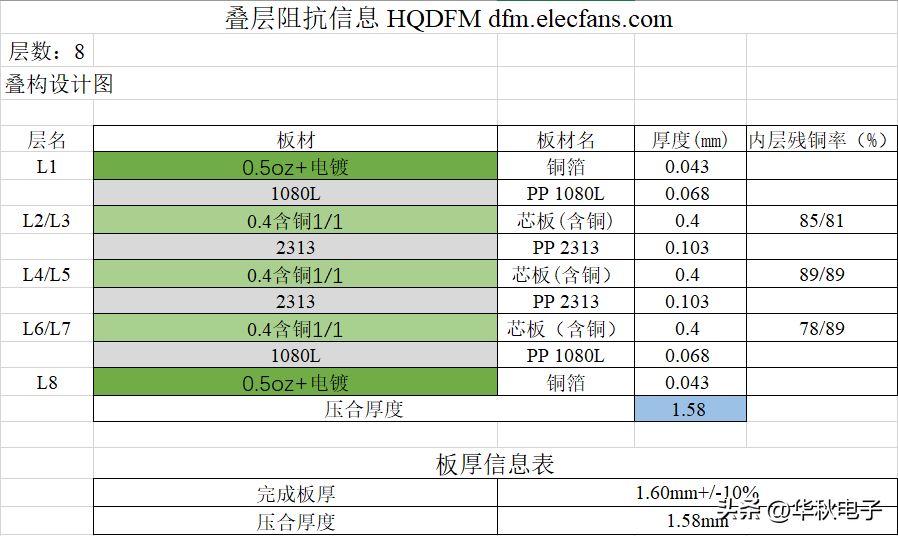

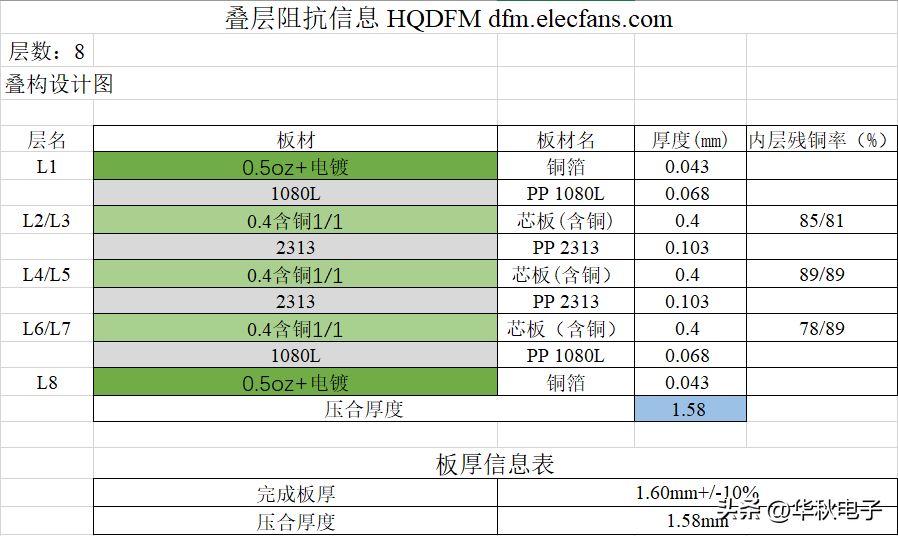

81945 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。

2023-07-18 09:22:31 875

875

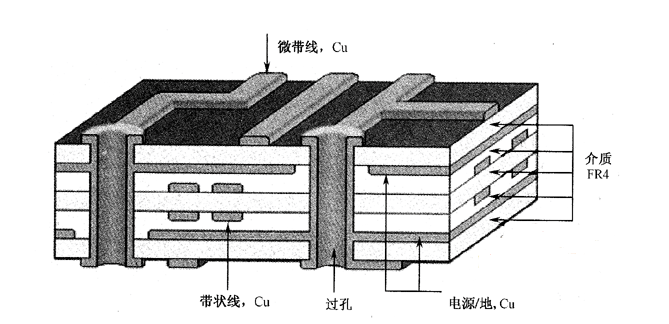

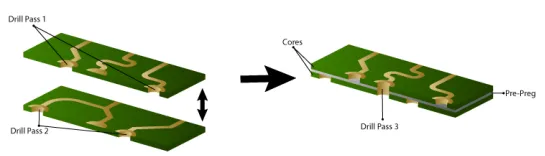

作者:蔣修國 過孔的應用場景非常多,過孔的結構也是相當復雜,在寫《ADS信號完整性仿真與實戰》一書時,用了一整章介紹了過孔。如下是過孔的一張簡化結構圖: 其中就包括了過孔的殘樁Stub。 通常

2021-03-12 11:17:20 2715

2715 決于選擇的PCB疊層結構。由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分

2023-07-31 10:18:02 684

684

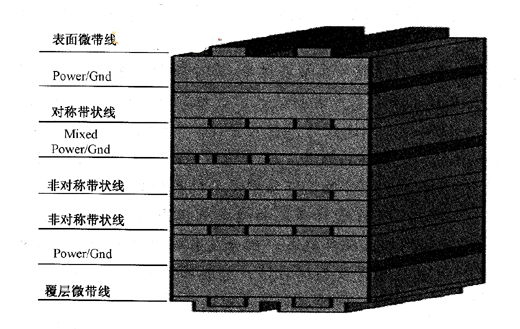

層疊結構是影響PCB板EMC性能的一個重要因素,也是抑制電磁干擾的一個重要手段。本文介紹多層PCB板層疊結構的相關內容。對于電源、地的層數以及信號層數確定后,它們之間的相對排布位置是每一個PCB工程師都不能回避的話題;

2016-08-04 11:27:07 6502

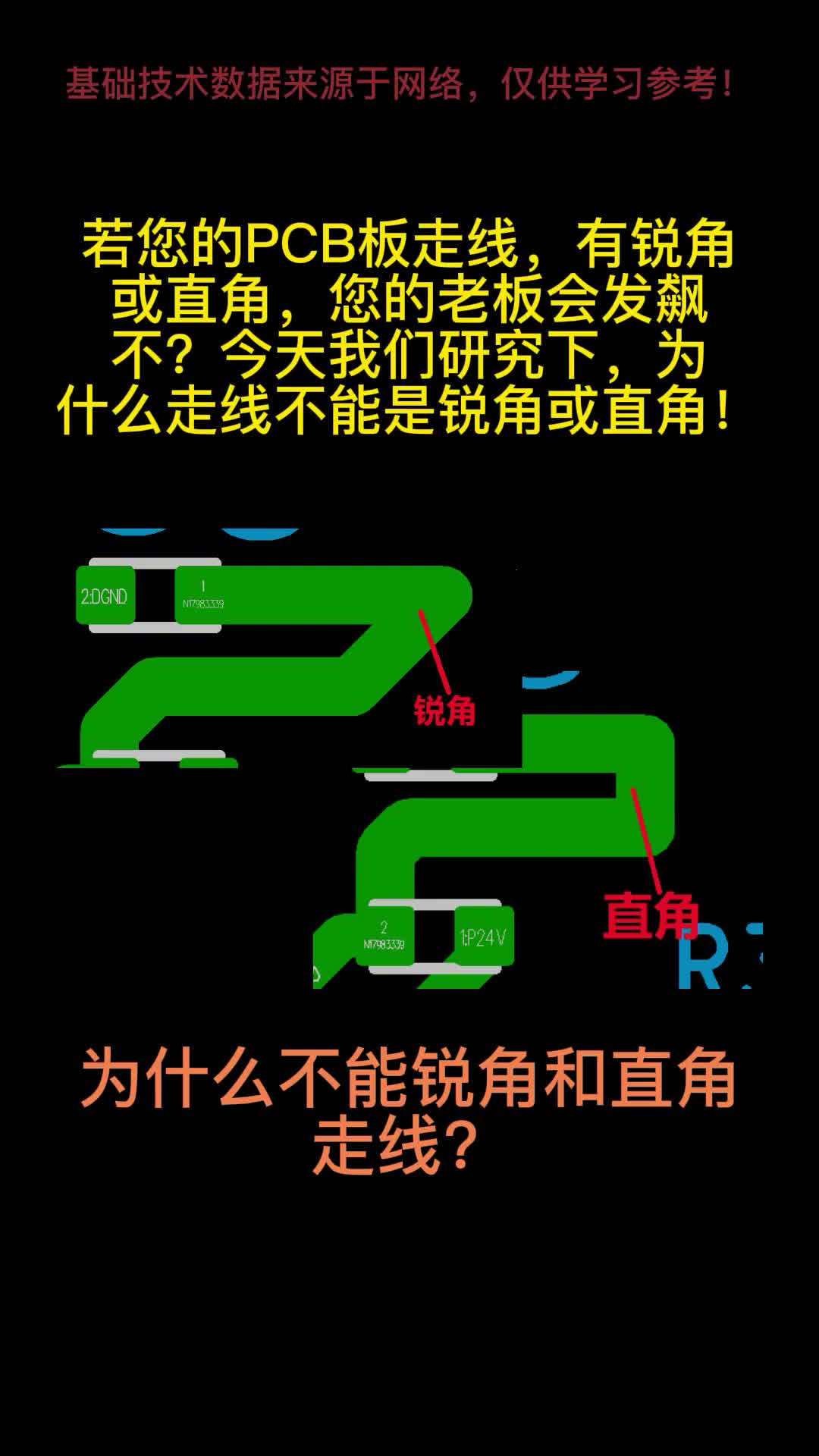

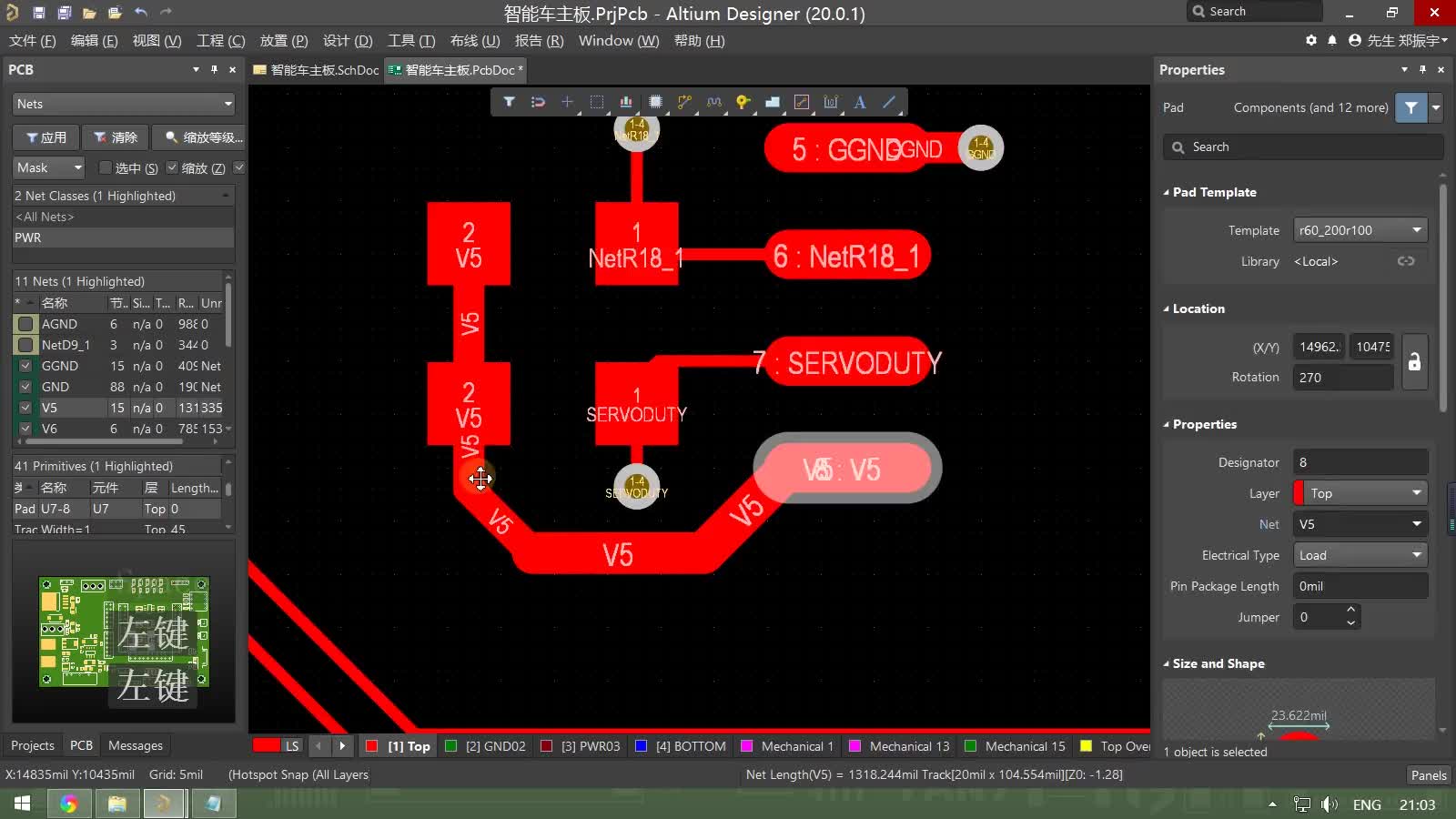

6502 下面從直角走線、差分走線、蛇形線三個方面來闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

本帖最后由 maskmyself 于 2017-7-10 10:08 編輯

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速

2017-07-07 11:45:56

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2014-08-13 15:44:05

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB設計中

2019-08-05 06:40:24

新人,求PCB布局走線資料,謝謝!

2014-08-02 19:19:40

PCB中走線有幾種這幾種分別有什么作用?哪種對信號的影響最好?

2012-11-13 15:49:21

pcb走線時,會影響到已經布完的線。之前正在布的線不會對已經布完的線產生影響,現在不知道怎么恢復。

2019-09-25 03:58:46

好的圖像質量的保證。 PCB走線如果可能的話,信號走線使用6mil, 走線間距使用6mil. 放置0.1uF的退耦電容在對應的DSP電源腳上,并盡可能的靠近。它的走線盡可能的粗。電源正極的走線最少要

2023-04-13 16:09:54

求高手貢獻PCB設計走線經驗!及相關技術

2013-01-11 20:02:07

1.PCB走線線寬的重要性 PCB載流能力的計算一直缺乏權威的技術方法、公式,經驗豐富CAD工程師依靠個人經驗能作出較準確的判斷。但是對于CAD新手,不可謂遇上一道難題。 對于大電流電源走線

2023-04-12 16:02:23

`為什么下圖中PCB走線正反面不同。孔與孔之間為直接通路。為什么背面的走線環繞迂回。小白菜提問,求高手詳解。謝謝`

2018-10-29 08:46:46

`用altium 畫PCB 對稱電路時走線沒有走對稱,看起來有點別扭。像這種對稱電路走線一般要怎么處理比較好呢?像我這樣畫對電器想能有沒有什么影響?要怎么畫才比較合理?希望大家指點指點`

2017-01-07 11:20:13

經常聽說“PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾”,這就是3W原則,信號線之間的干擾被稱為串擾。那么,你知道串擾是怎么形成的嗎?當兩條走線很近時,一條信號線上的信號可能會在另一

2022-12-27 20:33:40

在pcb的設計過程中,元器件的布局和走線的調整是非常重要的一個步驟。恰當的布局可以簡化布線的難度,更重要的是可以提高PCB的電氣性能,減少EMC,EMI。 下面是同一個原理圖對應的兩種不同的布局和走

2019-10-17 04:37:54

PCB板蛇形走線有什么作用PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,麥|斯|艾|姆|P|CB樣板貼片,麥1斯1艾1姆1科1技全國1首家P|CB樣板打板蛇形走線的主要作用

2013-08-29 15:43:30

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關"信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是時鐘

2017-11-22 20:04:14

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關”信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是

2018-08-30 10:14:44

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關”信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是

2020-07-14 18:02:17

PCB上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關"信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處?;最典型的就是

2018-09-20 11:05:23

PCB電容引腳之間可以走線嗎?

2023-04-13 16:25:48

1.1 PCB板上預劃分數字、模擬、DAA信號布線區域。1.2 數字、模擬元器件及相應走線盡量分開并放置於各自的布線區域內。1.3 高速數字信號走線盡量短。1.4 敏感模擬信號走線盡量短。1.5

2019-05-30 06:58:19

PCB設計走線的寬度與最大允許電流有何關系?PCB設計走線的寬度與銅厚有何關系?

2021-10-11 09:49:14

PCB設計走線的規則是什么

2021-03-17 06:36:28

PCB能不能以銳角走線pcb layout能不能以90°走線

2021-02-26 08:14:21

1. 一般規則1.1 PCB板上預劃分數字、模擬、DAA信號布線區域。1.2 數字、模擬元器件及相應走線盡量分開并放置於各自的布線區域內。1.3 高速數字信號走線盡量短。1.4 敏感模擬信號走線盡量

2014-03-14 17:44:44

pcb布局,走線方面,有什么建議嗎,該怎么怎么走,怎么提高效率

2016-10-15 14:51:34

;=2倍的線寬。PCI板上的蛇行線就是為了適應PCI 33MHzClock的線長要求。若在一般普通PCB板中,是一個分布參數的 LC濾波器,還可作為收音機天線的電感線圈,短而窄的蛇形走線可做保險絲等等

2019-05-22 02:48:05

PCB Layout中的走線策略布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見

2009-08-20 20:58:49

,盡量不要走蛇形線,尤其不能在小范圍內蜿蜒走線。5. 可以經常采用任意角度的蛇形走線,如圖1-8-20中的C結構,能有效的減少相互間的耦合。6. 高速PCB 設計中,蛇形線沒有所謂濾波或抗干擾的能力,只

2018-07-08 13:28:36

cadence PCB 怎么取消走線?***用過,取消很容易,cadence沒發現這個功能!

2016-01-25 22:57:46

的平面是導體,這就夠了。信號路徑是表層走線,所以下面的平面就是參考路徑。對于PCB上這一特殊結構,參考路徑是以平面的形式出現的,所以也叫參考平面。從電流回路的角度來說,參考平面承載著信號的返回

2014-11-17 10:07:29

作用,這種結構在高頻的(10G以上)IC封裝PCB設計中經常會用采用,被稱為CPW結構,可以保證嚴格的差分阻抗控制(2Z0),如圖1-8-19。差分走線也可以走在不同的信號層中,但一般不建議這種走法

2019-03-18 21:38:12

為什么PCB走線中不能出現銳角和直角?而且走線也不能和IC的PIN腳垂直?會影響到什么?

2023-04-11 16:31:28

介電常數受橫截面的幾何結構影響比較大;而串擾,其有效介電常數受奇偶模式的影響較大;不同繞線方式有效介電常數受其繞線方式的影響。3.仿真分析過程 3.1 微帶線和帶狀線傳輸時延PCB中微帶線是指走線只有一

2014-10-21 09:54:56

AD里PCB多根走線時怎么改變線寬

2019-09-12 04:20:46

怎樣計算PCB布線中走線允許的最大長度?走線太長了都有哪些影響呢?

2023-04-10 17:10:25

寬,距電源/地越近,或隔離層的介電常數越高,特征阻抗就越小。 11、PCB板上的走線可等效為串聯和并聯的電容、電阻和電感結構。串聯電阻的典型值0.25-0.55 ohms/英尺。并聯電阻阻值通常很高

2014-12-16 09:47:09

做一網絡通信,發現網口直線有點問題,直接從網絡變壓器的輸出端子接信號(我還用的排線)傳輸速度能達幾MB/S,但是如果通過PCB直線,發現傳輸速度只有幾KB/S,差別太大了,有什么挽救辦法沒有?由于結構原因,接口離網絡變壓器有7~8CM的距離走線,還經過了兩個連接器!

2012-10-17 21:01:53

PCB走線線間距能不能走5mil?

2019-09-26 05:35:53

PCB長距離走線和短距離加個過孔走線哪種走線更合理?

2019-09-25 22:11:32

AD18 ,PCB,走線,任意走線,在哪里設置?

2019-03-07 01:36:59

全球領先的全套互連產品供應商Molex公司推出2.4mm精密壓接安裝測試連接器產品,這是業界唯一的工作于50 GHz的高速垂直PCB裝接結構。與傳統的末端裝接連接器(end-launch connector)相比,

2012-07-10 09:30:49 971

971

2012-10-12 12:55:09 0

0 2013-12-16 14:10:04 0

0 電源平面和地平面要滿足20H規則;當電源層、底層數及信號的走線層數確定后,為使PCB具有良好的EMC性能它們之間的相對排布位置基本要求...

2018-03-30 16:05:45 17029

17029

在設計多層 PCB 電路板之前,設計者需要首先根據電路的規模、電路板的尺寸和電磁兼容(EMC)的要求來確定所采用的電路板結構,也就是決定采用 4 層,6 層,還是更多層數的電路板。 確定層數之后, 再確定內電層的放置位置以及如何在這些層上分布不同的信號。

2018-08-01 08:00:00 0

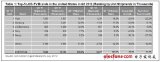

0 尋找PCB行業結構性成長機會。在2000年以前,全球PCB產值70%分布在歐洲、美洲、日本等三個地區。

2018-08-03 16:34:06 5018

5018 PCB產品結構復雜,產品種類根據終端需求不斷演進:終端電子產品向輕薄、短小、多功能的需求變化,促使電子元器件的產品性能和集成度迅速提升。

2018-09-07 17:07:26 13570

13570 我國PCB產業結構仍有改善空間,IC載板占比低于國際水平。從PCB產業結構來看, Prismark數據顯示,全球PCB市場中,IC載板占比始終高于10%,而我國PCB產業IC載板占比始終保持在較低

2019-01-18 16:51:07 7036

7036

這種精度對低頻電路沒有一點問題,但RF電路一般需要50Ω的走線才能正常運行。部件體積越來越小,但物理定律不會改變。因此, 今天0.062英寸厚原型板上的一根微帶走線尺寸為0.11英寸寬,而30年前也是0.11英寸。但很多SMT(表面組裝技術)元件都要比其前代元件小得多,因此,用于RF原型的低成本雙面板似乎不適合于今天的小型SMT元件。

2019-02-26 14:36:05 3118

3118 機械層是定義整個PCB板的外觀的,其實我們在說機械層的時候就是指整個PCB板的外形結構。

2020-01-16 12:11:00 3613

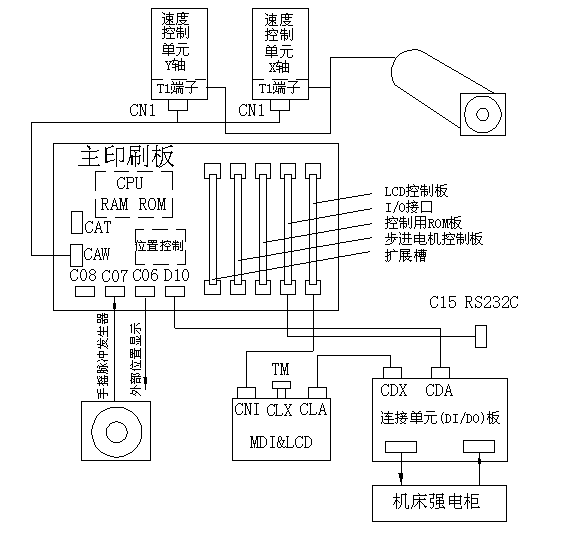

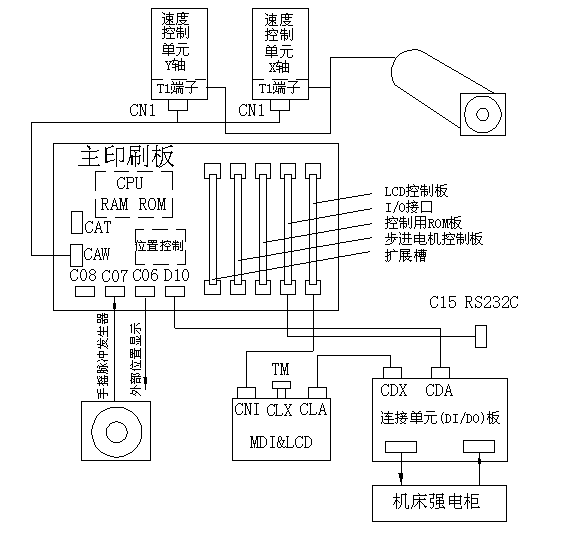

3613 數控裝置是整個數控系統的核心,其硬件結構按CNC裝置中各PCB電路板的插接方式可以分為大板式結構和功能模塊式結構。

2019-11-12 17:36:30 1596

1596

近年我國的印制電路行業走過了艱辛的歷程,外資大量涌入,內資體制調整,價格競爭激烈,成本不斷上漲,兼并重組使中國的PCB產業結構發生了巨大變化。

2019-11-09 11:21:29 805

805 機械層是定義整個PCB板的外觀的,其實我們在說機械層的時候就是指整個PCB板的外形結構。

2019-09-05 16:07:25 3045

3045 隨著市場競爭的加劇,硬件設備正以集成化的方向發展。天線也由外置進化內置再進化到嵌入式,我們先來介紹這類應用的天線種類:

2019-09-09 10:49:00 0

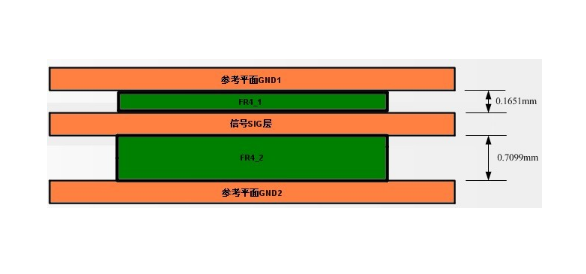

0 確定多層PCB板的層疊結構需要考慮較多的因素。從布線方面來說,層數越多越利于布線,但是制板成本和難度也會隨之增加。對于生產廠家來說,層疊結構對稱與否是PCB板制造時需要關注的焦點,所以層數的選擇需要考慮各方面的需求,以達到最佳的平衡。

2019-10-04 17:10:00 8395

8395

確定多層 PCB 板的層疊結構需要考慮較多的因素。從布線方面來說,層數越多越利于布線,但是制板成本和難度也會隨之增加。對于生產廠家來說,層疊結構對稱與否是 PCB 板制造時需要關注的焦點,所以層數的選擇需要考慮各方面的需求,以達到最佳的平衡。

2019-10-15 14:31:36 4960

4960

在PCBA業務領域,隨著南通數通二期的投產,無錫深南PCB產品結構得到進一步優化,從而使無錫深南 PCB 業務的生產效率及產出得到提升,盈利能力增強;無錫深南的PCBA業務在上半年也有一定的增長。

2020-09-25 10:59:16 2338

2338 晶體盡量靠近主控放置,晶體的負載電容靠近管腳放置;晶體走線盡量短且走在表層,避免打孔換層。

2021-02-19 15:47:27 4242

4242

選擇板層、板厚、內層銅厚、阻抗層、參考層并輸入阻抗值、線距(差分阻抗)、線到銅的距離(共面阻抗),點計算,可自動計算出線寬及疊構方案。

2022-09-16 09:23:08 2206

2206 關鍵信號優先選TOP層,因為在TOP層下面是GND層。射頻和高速信號,走線需要為50ohm,所以疊層厚度需要考慮阻抗控制。

2022-10-09 16:15:39 1849

1849 雖然PCB技術有了進步,但PCB的基本結構沒有改變,例如材料特性、使用的層疊層數、幾何結構和鉆孔技術(允許孔只穿透堆疊的一部分)。通過PCB技術形成的結構被抽象為一組物理/電氣結構:走線、平面(或電源層)、通孔和焊盤。

2022-10-20 11:15:03 540

540 在PCB設計時我們在處理DDR部分的時候都會進行一個拓撲的選擇,一般DDR有T點和Fly-by兩種拓撲結構,那么這兩種拓撲結構的應用場景和區別有哪些呢? T點拓撲結構: CPU出來的信號線經過

2022-11-27 07:40:01 999

999 PCB板層層疊結構介紹

2023-02-18 17:47:09 2582

2582

該基站的雙工器似乎是虹膜耦合腔濾波器,與一些腔間耦合。輸入和輸出的耦合是T,是諧振器上的一個連接部分,而不是耦合回路。頻率由電容帽調節。濾波器是寬信號的帶通。

2023-03-04 16:03:51 353

353 和正片設計相反,負片設計默認是有銅的,走線和鋪銅的地方意味著這里的銅被清除,沒有走線和鋪銅的地方銅被保留。見下圖。其成本相對正片來說極低,且流程短,但存在極大的“壞孔”隱患。

2023-03-19 11:36:43 948

948 ?精進成為一個很厲害的工程師。 同樣是硬件工程師,有的三四年年收入增長了三倍,有的只漲了3000,甚至于還有降薪了,這些都是身邊朋友同事的真實案例。當然不排除運氣的因素,但是持續的充電學習,迅速提高自己的設計能力和專業素養,是你獲得專業技能提升與漲薪的不二法門。 ? ? ?? 硬件工程師是需要“廣”而“博”的設計知識的。 ? ? ?如果你想在此行業有更好的發展,不僅僅要懂得基本數字硬件設計知識,還需要 模擬電路的設計知識

2023-07-04 12:15:04 269

269

決于選擇的PCB疊層結構。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。 PCB疊層設計 “ ?層的定義設計原則? 1、主芯片相臨層

2023-07-19 07:45:02 543

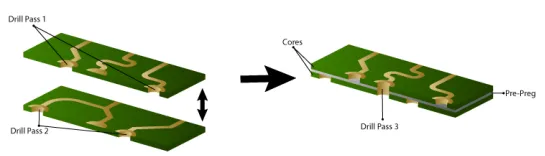

543 在設計2層PCB時,實際上不需要考慮PCB在工廠的結構問題。但是,當電路板上的層數為四層或更多時,PCB的堆疊是一個重要因素。

2023-07-19 16:19:13 2030

2030

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。

2023-07-20 09:20:21 510

510

決于選擇的PCB疊層結構。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。 PCB疊層設計 “ ?層的定義設計原則? 1、主芯片相臨層

2023-07-27 18:15:06 341

341

決于選擇的PCB疊層結構。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。 PCB疊層設計 “ 層的定義設計原則 1、主芯片相臨層為地

2023-07-31 10:15:02 434

434

決于選擇的PCB疊層結構。由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。 一、PCB疊層設計 層的定義設計原則: 1)主芯片相臨層

2023-08-01 07:45:01 1760

1760

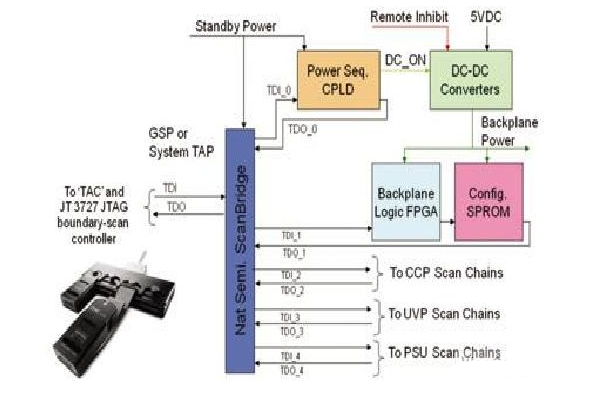

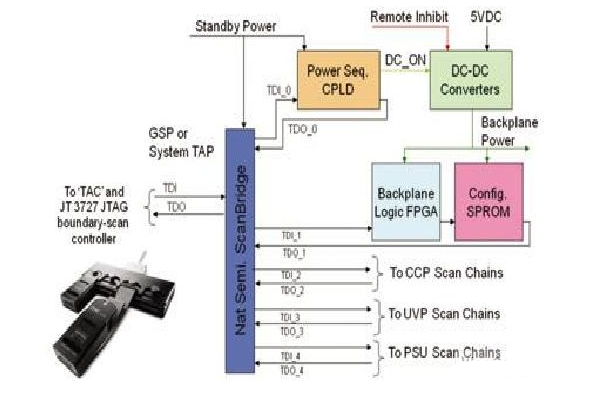

在測試系統中,NI PCI-6533用作位于每個SRI(商店可替換品)上EMId(電子模塊標識)設備的接口。它們帶有元件編號和序列號數據等等,還包括近故障檢測日志。PCI-DIO-96 被作為一個使用CPLD、有160 個管腳的DIO,CPLD 將來自測試控制器PC 的I/O 板卡的輸出和輸入進行多路復用。

2023-10-17 14:53:08 192

192

該基站的雙工器似乎是虹膜耦合腔濾波器,與一些腔間耦合。輸入和輸出的耦合是T,是諧振器上的一個連接部分,而不是耦合回路。頻率由電容帽調節,濾波器是寬信號的帶通,如果能看到該過濾器的響應速度,那就更好了。

2023-10-27 10:45:36 325

325

如何設計出低成本和快速PCB工藝的CPWG結構?網上可以找到很多CPWG計算器,但當地層間距小于約走線寬度的30%?50%時,這些計算器就會失效,因為電路板上銅箔走線的高度成為了一個顯著因素。

2023-11-08 14:57:40 89

89 確定多層 PCB 板的層疊結構需要考慮較多的因素。從布線方面來說,層數越多越利于布線 但是制層數越多越利于布線,但是制層數越多越利于布線 板成本和難度也會隨之增加。

2023-11-13 15:33:05 156

156 切片分析切片分析就是通過取樣、鑲嵌、切片、拋磨、腐蝕、觀察等一系列手段和步驟獲得 PCB 橫截面結構的過程。

2023-11-16 16:31:56 156

156 確定多層PCB板的層疊結構需要考慮較多的因素。從布線方面來說,層數越多越利于布線,但是制板成本和難度也會隨之增加。對于生產廠家來說,層疊結構對稱與否是PCB板制造時需要關注的焦點,所以層數的選擇需要考慮各方面的需求,以達到的平衡。

2023-11-22 15:29:56 270

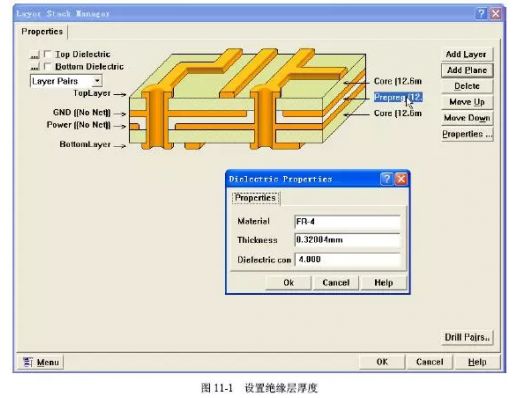

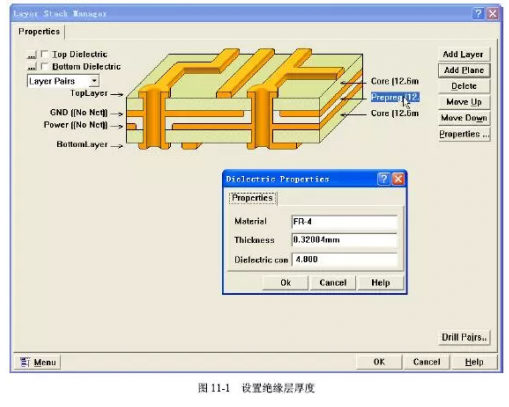

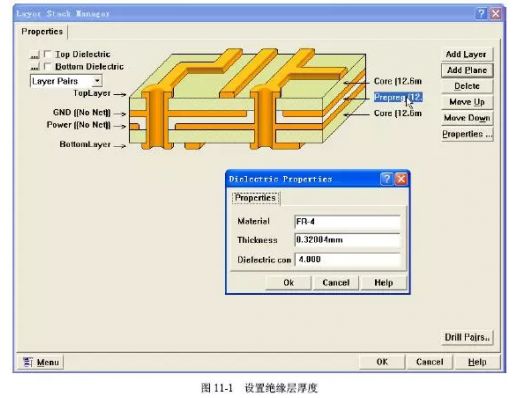

270 1.PCB疊層結構與阻抗計算1.1.Core和PPPCB由Core和Prepreg(半固化片)組成。Core是覆銅板(通常是FR4—玻璃纖維&環氧基樹脂),Core的上下表面之間填充的是固態

2024-01-25 17:15:52 1177

1177

電子發燒友App

電子發燒友App

評論