說到PCB板,很多朋友會想到它在我們周圍隨處可見,從一切的家用電器,電腦內的各種配件,到各種數(shù)碼產品,只要是電子產品幾乎都會用到PCB板,那么到底什么是PCB板呢?PCB板就是PrintedCircuitBlock,即印制電路板,供電子組件安插,有線路的基版。通過使用印刷方式將鍍銅的基版印上防蝕線路,并加以蝕刻沖洗出線路。

PCB板可以分為單層板、雙層板和多層板。各種電子元件都是被集成在PCB板上的,在基本的單層PCB上,零件都集中在一面,導線則都集中在另一面。這么一來我們就需要在板子上打洞,這樣接腳才能穿過板子到另一面,所以零件的接腳是焊在另一面上的。因為如此,這樣的PCB的正反面分別被稱為零件面(ComponentSide)與焊接面(SolderSide)。

雙層板可以看作把兩個單層板相對粘合在一起組成,板的兩面都有電子元件和走線。有時候需要把一面的單線連接到板的另一面,這就要通過導孔(via)。導孔是在PCB上,充滿或涂上金屬的小洞,它可以與兩面的導線相連接。現(xiàn)在很多電腦主板都在用4層甚至6層PCB板,而顯卡一般都在用了6層PCB板,很多高端顯卡像nVIDIAGeForce4Ti系列就采用了8層PCB板,這就是所謂的多層PCB板。

在多層PCB板上也會遇到連接各個層之間線路的問題,也可以通過導孔來實現(xiàn)。由于是多層PCB板,所以有時候導孔不需要穿透整個PCB板,這樣的導孔叫做埋孔(Buriedvias)和盲孔(Blindvias),因為它們只穿透其中幾層。盲孔是將幾層內部PCB與表面PCB連接,不須穿透整個板子。

埋孔則只連接內部的PCB,所以光是從表面是看不出來的。在多層板PCB中,整層都直接連接上地線與電源。所以我們將各層分類為信號層(Signal),電源層(Power)或是地線層(Ground)。如果PCB上的零件需要不同的電源供應,通常這類PCB會有兩層以上的電源與電線層。采用的PCB板層數(shù)越多,成本也就越高。當然,采用更多層的PCB板對提供信號的穩(wěn)定性很有幫助。

的PCB板制作過程相當復雜,拿4層PCB板為例。主板的PCB大都是4層的。制造的時候是先將中間兩層各自碾壓、裁剪、蝕刻、氧化電鍍后,這4層分別是元器件面、電源層、地層和焊錫壓層。再將這4層放在一起碾壓成一塊主板的PCB。接著打孔、做過孔。

洗凈之后,將外面兩層的線路印上、敷銅、蝕刻、測試、阻焊層、絲印。將整版PCB(含許多塊主板)沖壓成一塊塊主板的PCB,再通過測試后進行真空包裝。如果PCB制作過程中銅皮敷著得不好,會有粘貼不牢現(xiàn)象,容易隱含短路或電容效應(容易產生干擾)。PCB上的過孔也是必須注意的。

如果孔打得不是在正中間,而是偏向一邊,就會產生不均勻匹配,或者容易與中間的電源層或地層接觸,從而產生潛在短路或接地不良因素。

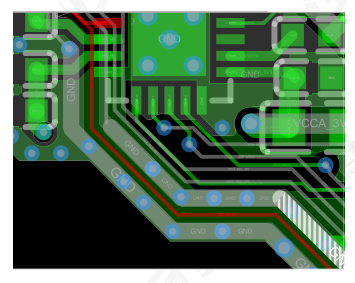

銅線布線過程

制作的步是建立出零件間聯(lián)機的布線。我們采用負片轉印方式將工作底片表現(xiàn)在金屬導體上。這項技巧是將整個表面鋪上一層薄薄的銅箔,并且把多余的部份給消除。追加式轉印是另一種比較少人使用的方式,這是只在需要的地方敷上銅線的方法,不過我們在這里就不多談了。正光阻劑是由感光劑制成的,它在照明下會溶解。有很多方式可以處理銅表面的光阻劑,不過普遍的方式,是將它加熱,并在含有光阻劑的表面上滾動。它也可以用液態(tài)的方式噴在上頭,不過干膜式提供比較高的分辨率,也可以制作出比較細的導線。遮光罩只是一個制造中PCB層的模板。在PCB板上的光阻劑經過UV光曝光之前,覆蓋在上面的遮光罩可以防止部份區(qū)域的光阻劑不被曝光。這些被光阻劑蓋住的地方,將會變成布線。在光阻劑顯影之后,要蝕刻的其它的裸銅部份。蝕刻過程可以將板子浸到蝕刻溶劑中,或是將溶劑噴在板子上。一般用作蝕刻溶劑使用三氯化鐵等。蝕刻結束后將剩下的光阻劑去除掉。

1.布線寬度和電流

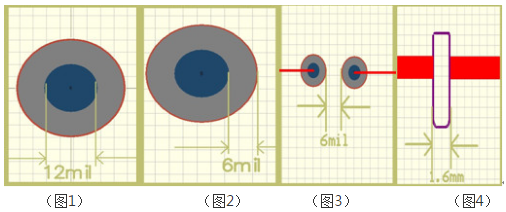

一般寬度不宜小于0.2mm(8mil)

在高密度高的PCB上,間距和線寬一般0.3mm(12mil)。

當銅箔的厚度在50um左右時,導線寬度1~1.5mm (60mil) = 2A

公共地一般80mil,對于有微處理器的應用更要注意。

2.到底多高的頻率才算高速板?

當信號的上升/下降沿時間《 3~6倍信號傳輸時間時,即認為是高速信號。

對于數(shù)字電路,關鍵是看信號的邊沿陡峭程度,即信號的上升、下降時間,

按照一本非常經典的書《High Speed Digtal Design》的理論,信號從10%上升到90%的時間小于6倍導線延時,就是高速信號!------即!即使8KHz的方波信號,只要邊沿足夠陡峭,一樣是高速信號,在布線時需要使用傳輸線路論

3.PCB板的堆疊與分層

四層板有以下幾種疊層順序。下面分別把各種不同的疊層優(yōu)劣作說明:

第一種情況

GND

S1+POWER

S2+POWER

GND

第二種情況

SIG1

GND

POWER

SIG2

第三種情況

GND

S1

S2

POWER

注:S1 信號布線一層,S2 信號布線二層;GND 地層 POWER 電源層

種情況,應當是四層板中的一種情況。因為外層是地層,對EMI有屏蔽作用,同時電源層同地層也可靠得很近,使得電源內阻較小,取得郊果。但種情況不能用于當本板密度比較大的情況。因為這樣一來,就不能保證層地的完整性,這樣第二層信號會變得更差。另外,此種結構也不能用于全板功耗比較大的情況。

第二種情況,是我們平時常用的一種方式。從板的結構上,也不適用于高速數(shù)字電路設計。因為在這種結構中,不易保持低電源阻抗。以一個板2毫米為例:要求Z0=50ohm. 以線寬為8mil.銅箔厚為35цm。這樣信號一層與地層中間是0.14mm。而地層與電源層為1.58mm。這樣就大大的增加了電源的內阻。在此種結構中,由于輻射是向空間的,需加屏蔽板,才能減少EMI。

第三種情況,S1層上信號線質量。S2次之。對EMI有屏蔽作用。但電源阻抗較大。此板能用于全板功耗大而該板是干擾源或者說緊臨著干擾源的情況下。

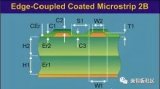

4.阻抗匹配

反射電壓信號的幅值由源端反射系數(shù)ρs和負載反射系數(shù)ρL 決定

ρL = (RL - Z0) / (RL + Z0) 和 ρS = (RS - Z0) / (RS + Z0)

在上式中,若RL=Z0則負載反射系數(shù)ρL=0。若 RS=Z0源端反射系數(shù)ρS=0。

由于普通的傳輸線阻抗Z0通常應滿足50Ω的要求50Ω左右,而負載阻抗通常在幾千歐姆到幾十千歐姆。因此,在負載端實現(xiàn)阻抗匹配比較困難。然而,由于信號源端(輸出)阻抗通常比較小,大致為十幾歐姆。因此在源端實現(xiàn)阻抗匹配要容易的多。如果在負載端并接電阻,電阻會吸收部分信號對傳輸不利(我的理解)。當選擇TTL/CMOS標準 24mA驅動電流時,其輸出阻抗大致為13Ω。若傳輸線阻抗Z0=50Ω,那么應該加一個33Ω的源端匹配電阻。13Ω+33Ω=46Ω (近似于50Ω,弱的欠阻尼有助于信號的setup時間)

當選擇其他傳輸標準和驅動電流時,匹配阻抗會有差異。在高速的邏輯和電路設計時,對一些關鍵的信號,如時鐘、控制信號等,我們建議一定要加源端匹配電阻。

這樣接了信號還會從負載端反射回來,因為源端阻抗匹配,反射回來的信號不會再反射回去。

電子發(fā)燒友App

電子發(fā)燒友App

評論