業(yè)界領(lǐng)先的全新 1.8V 版 VersaClock? 3S 可編程時鐘發(fā)生器,為消耗品和計算系統(tǒng)創(chuàng)造具有競爭力的性能、能耗和靈活性。

2017-09-28 10:15:46 8178

8178 的時鐘發(fā)生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發(fā)生器。然而,如果不慎重考慮時鐘發(fā)生器、相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器、動態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。本文將詳細(xì)討論

2018-10-18 11:29:03

概述:AD9577是一款既提供一個多路輸出時鐘發(fā)生器功能,又帶有兩個片上鎖相環(huán)內(nèi)核PLL1和PLL2,專門針對網(wǎng)絡(luò)時鐘應(yīng)用而優(yōu)化。PLL設(shè)計基于ADI公司成熟的高性能、低抖動頻率合成器產(chǎn)品系列,確保實(shí)現(xiàn)最高的網(wǎng)

2021-04-06 06:49:57

系統(tǒng)設(shè)計師通常側(cè)重于為應(yīng)用選擇最合適的數(shù)據(jù)轉(zhuǎn)換器,在向數(shù)據(jù)轉(zhuǎn)換器提供輸入的時鐘發(fā)生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發(fā)生器的相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器動態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。

2019-07-30 07:57:42

輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內(nèi)集成鎖相環(huán)(PLL)和電壓控制振蕩器(VCO)。 產(chǎn)品名稱:時鐘發(fā)生器 AD9520-3BCPZ特征低相位噪聲、鎖相環(huán)(PLL)片內(nèi)VCO的調(diào)諧頻率范圍為

2019-07-09 11:50:41

(LVDS工作模式) AD9571ACPZPEC產(chǎn)品詳情AD9571具有多路輸出時鐘發(fā)生器功能,內(nèi)置專用PLL內(nèi)核,針對以太網(wǎng)線路卡應(yīng)用進(jìn)行了優(yōu)化。整數(shù)N PLL設(shè)計基于ADI公司成熟的高性能、低抖動

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140??A可編程多時鐘發(fā)生器評估板。評估抖動性能和功能很容易

2020-07-27 15:01:46

SI5324-EVB,SI5324評估板,0.002至710 MHz時鐘發(fā)生器。 SI5324-EVB為評估SI5316任意速率精度時鐘提供平臺。 SI5316直接使用器件上的配置引腳進(jìn)行控制

2019-02-22 09:30:51

概述:MAX3625B是MAXIM公司生產(chǎn)的一款提供三路輸出的低抖動,高精度時鐘發(fā)生器。該MAX3625B是為網(wǎng)絡(luò)應(yīng)用而優(yōu)化的低抖動,高精度時鐘發(fā)生器。該器件集成一個晶體振蕩器和鎖相環(huán)(PLL)時鐘

2021-05-18 07:39:05

供應(yīng) 現(xiàn)貨 CG635 斯坦福 時鐘發(fā)生器 歐陽R:*** QQ:1226365851溫馨提示:如果您找不到聯(lián)系方式,請在瀏覽器上搜索一下,旺貿(mào)通儀器儀回收工廠或個人、庫存閑置、二手儀器及附件。長期

2020-08-18 09:08:58

可編程音頻時鐘發(fā)生器MAX9485資料下載內(nèi)容主要介紹了:MAX9485引腳功能MAX9485功能和特性MAX9485應(yīng)用范圍MAX9485內(nèi)部方框圖MAX9485極限參數(shù)MAX9485典型應(yīng)用電路

2021-04-02 06:21:48

我要做畢業(yè)設(shè)計 叫 基于lmk03806的高性能可編程時鐘發(fā)生器的設(shè)計與fpga實(shí)現(xiàn),需要有protel 99se畫 lmk03806的原理圖和fpga的配置電路,用vhdl編程仿真,用fpga來配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

我正在使用planahead 14.4在VC707上添加7系列MIG(IP版本1.07a)。當(dāng)我使用第一個具有200MHz振蕩器輸入的時鐘發(fā)生器驅(qū)動MIG時,我的設(shè)計可以完全路由,我嘗試

2020-08-11 10:07:25

在我們的設(shè)計中,其中一個模塊從外部可配置

時鐘發(fā)生器芯片接收其

時鐘信號。現(xiàn)在在我們的ML507上使用這個

時鐘發(fā)生器芯片IDT5V9885就在那里任何跳線設(shè)置?我們問這個是因?yàn)樵谖覀兊纳暾堉熊浖覀?/div>

2019-09-02 08:12:30

擴(kuò)頻時鐘發(fā)生器MAX31C80資料下載內(nèi)容包括:MAX31C80引腳功能MAX31C80功能和特性MAX31C80應(yīng)用范圍MAX31C80內(nèi)部方框圖MAX31C80電壓范圍MAX31C80典型應(yīng)用電路

2021-04-02 06:29:55

的恒溫晶振,但是在某些特殊的測試場景,我們會非常關(guān)注信號發(fā)生器的絕對頻率精度,或者隨時間和溫度的漂移導(dǎo)致的穩(wěn)定度,這個時候只需要單獨(dú)采購一個高精度的恒溫晶振選件,作為信號發(fā)生器的外部參考,就可以有效地

2020-09-03 11:20:10

斯坦福 CG635 供應(yīng) CG635 時鐘發(fā)生器 歐陽R:*** QQ:1226365851回收工廠或個人、庫存閑置、二手儀器及附件。長期 專業(yè)銷售、維修、回收 高頻 二手儀器。溫馨提示:如果您

2019-06-16 12:07:43

熱賣現(xiàn)貨 CG635 斯坦福 時鐘發(fā)生器 歐陽R:*** QQ:1226365851溫馨提示:如果您找不到聯(lián)系方式,請在瀏覽器上搜索一下,旺貿(mào)通儀器儀回收工廠或個人、庫存閑置、二手儀器及附件。長期

2020-12-03 08:39:05

AD9525 / PCBZ,用于AD9525時鐘發(fā)生器的評估板。 AD9525旨在支持長期演進(jìn)(LTE)和多載波GSM基站設(shè)計的轉(zhuǎn)換器時鐘要求。 AD9525提供低功耗,多輸出,時鐘分配功能和低抖動

2019-02-25 08:38:34

AD9576 / PCBZ,AD9576評估板提供多輸出時鐘發(fā)生器功能,包括兩個專用鎖相環(huán)(PLL)內(nèi)核,具有靈活的頻率轉(zhuǎn)換功能,經(jīng)過優(yōu)化,可作為整個系統(tǒng)的強(qiáng)大異步時鐘源,提供擴(kuò)展功能通過監(jiān)控和冗余

2019-02-25 09:40:01

SI52147-EVB,用于PoE無線接入點(diǎn)的時鐘發(fā)生器評估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標(biāo)準(zhǔn)的9端口PCIe時鐘發(fā)生器

2020-08-27 14:27:11

?疑問3:是不是使用PLL類型的時鐘發(fā)生器芯片帶來的抖動誤差會比較大?針對14位的ADC輸入差分時鐘有此類型的參考嗎? 模擬輸入部分:疑問1:參考文檔中使用AD8138差分驅(qū)動芯片,計劃采用5v單電源模式

2018-11-07 09:35:54

的范圍在100fs至300fs之間。這個12kHz-20MHz的標(biāo)準(zhǔn)相位噪聲集成范圍包括鎖相環(huán) (PLL) 頻帶內(nèi)和頻帶外 (VCO) 噪聲的影響。基準(zhǔn)時鐘發(fā)生器的相位噪聲性能需要在PLL環(huán)路帶寬內(nèi)

2018-09-05 16:07:30

描述TIDA-00597 可為時鐘發(fā)生器提供噪聲非常低的輸出電源。主要特色低噪聲,適用于時鐘發(fā)生器輸出電流高達(dá) 800mA低相位噪聲輸出功率啟用和禁用

2018-08-22 07:43:40

AC1571時鐘發(fā)生器一款基于PLL的、適用于5G基站應(yīng)用的時鐘發(fā)生器。采用數(shù)字鎖相環(huán)技術(shù),以實(shí)現(xiàn)最佳的高頻低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技術(shù),管腳兼容843N571,可以

2022-08-11 16:26:33

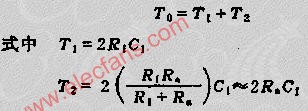

本文介紹了74HC4046的工作原理以及采用—74HC4046鎖相環(huán)芯片組成的圖象數(shù)字化電路中的行鎖相象素時鐘發(fā)生器,該發(fā)生器的過渡過程快,捕獲時間短,跟蹤精度高,本文給出了實(shí)用電路.

2009-04-28 14:05:37 15

15 具有音頻時鐘的 3G/高清/標(biāo)清視頻時鐘發(fā)生器 Function Clock generator Number of outputs 4 Output frequency

2022-12-02 13:47:21

AC1571 是用于 5G 基站應(yīng)用的基于 PLL的時鐘發(fā)生器,該芯片采用全數(shù)字鎖相環(huán)技術(shù),以實(shí)現(xiàn)最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應(yīng)用場景:· 無線基站·

2023-12-12 14:25:17

時鐘發(fā)生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術(shù),以實(shí)現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實(shí)現(xiàn)小于0.3ps RMS的相位抖動性能

2023-12-29 09:29:50

時鐘發(fā)生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術(shù),以實(shí)現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實(shí)現(xiàn)小于0.3ps RMS的相位抖動性能

2024-02-04 11:41:14

MAX9489/MAX9471多輸出時鐘發(fā)生器構(gòu)建集成時鐘源

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發(fā)生器有許多優(yōu)勢。本文探討了集中時鐘發(fā)生器(如

2008-10-04 20:43:25 922

922

MAX9471, MAX9472 多輸出時鐘發(fā)生器,提供雙PLL和OTP

MAX9471/MAX9472器件輸出一組消費(fèi)類產(chǎn)品中最

2008-10-04 20:47:43 693

693

Si5338 業(yè)界首個任意頻率、任意輸出的時鐘發(fā)生器

高性能模擬與混合信號領(lǐng)導(dǎo)廠商Silicon Laboratories日前發(fā)表全新的時鐘發(fā)生器和緩沖器系列,可為業(yè)

2008-11-10 09:39:44 1763

1763

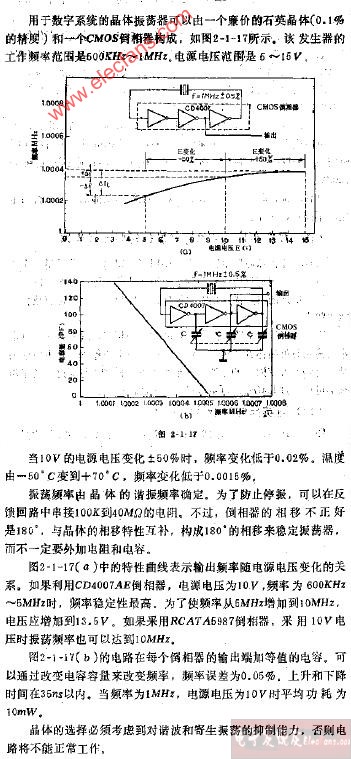

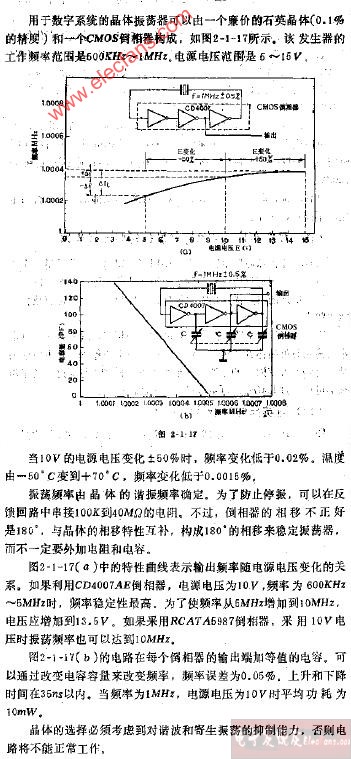

高精度石英晶體鐘脈沖發(fā)生器

2009-03-21 09:13:07 578

578

精密時鐘發(fā)生器電路圖

2009-03-25 09:35:22 1054

1054

振蕩器時鐘發(fā)生器電路圖

2009-04-13 08:54:22 720

720

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發(fā)生器有許多優(yōu)勢。本文探討了集中時鐘發(fā)生器(如MAX9489和MAX9471)的優(yōu)點(diǎn),如:降低系統(tǒng)成本、良好的信號完整性、抑制干

2009-04-22 10:11:53 407

407

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發(fā)生器有許多優(yōu)勢。本文探討了集中時鐘發(fā)生器(如MAX9489和MAX9471)的優(yōu)點(diǎn),如:降低系統(tǒng)成本、良好的信號完整性、抑制干

2009-05-03 11:07:05 652

652

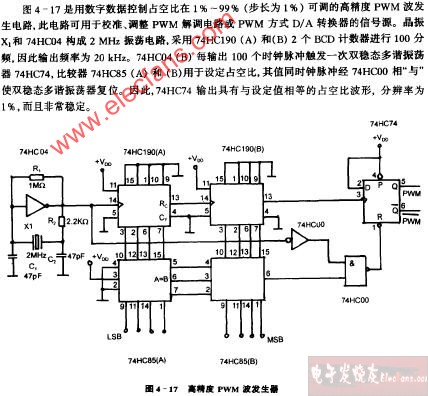

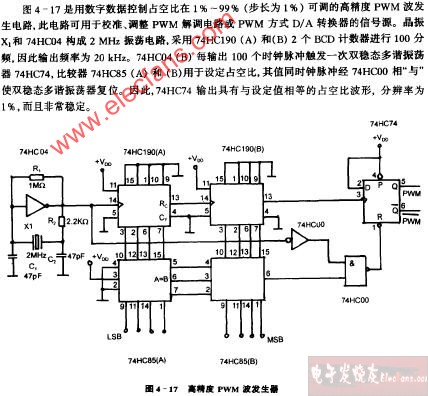

高精度PWM波發(fā)生器電路圖

2009-07-15 16:52:29 1261

1261

MAX3625A 低抖動、精密時鐘發(fā)生器,提供三路輸出

2009-08-13 13:01:27 828

828

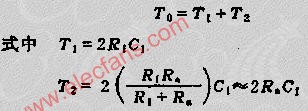

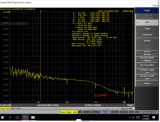

評估低抖動PLL時鐘發(fā)生器的電源噪聲抑制性能

本文介紹了電源噪聲對基于PLL的時鐘發(fā)生器的干擾,并討論了幾種用于評估確定性抖動(DJ)的技術(shù)方案。推導(dǎo)出的關(guān)系式提

2009-09-18 08:46:32 1461

1461

MAX3624 低抖動、精密時鐘發(fā)生器,提供四路輸出

概述

MAX3624是一款低抖動精密

2009-09-18 08:56:41 682

682

Maxim推出高性能、三路輸出時鐘發(fā)生器MAX3625B

Maxim近日推出高性能、三路輸出時鐘發(fā)生器MAX3625B,適用于以太網(wǎng)和光纖通道網(wǎng)絡(luò)設(shè)備。器件采用低噪聲VCO和PLL架構(gòu),能夠

2009-12-14 17:25:04 1040

1040 MAX3625B 抖動僅為0.36ps的PLL時鐘發(fā)生器

概述

MAX3625B是一款低抖動、精密時鐘發(fā)生器,優(yōu)化用于網(wǎng)絡(luò)設(shè)備。器件內(nèi)置晶體振蕩器和鎖相環(huán)(PLL)

2010-03-01 08:56:18 1345

1345

MAX3679A高性能四路輸出時鐘發(fā)生器(Maxim)

Maxim推出用于以太網(wǎng)設(shè)備的高性能、四路輸出時鐘發(fā)生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 778

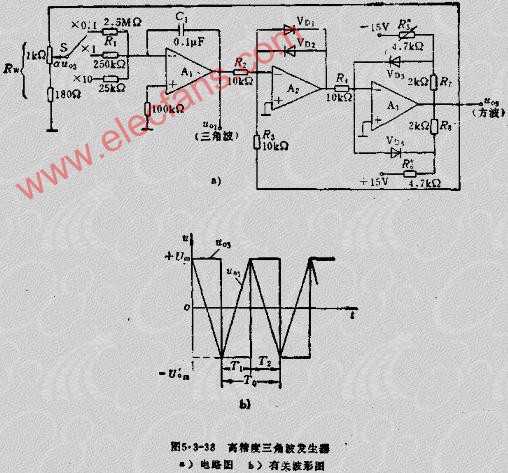

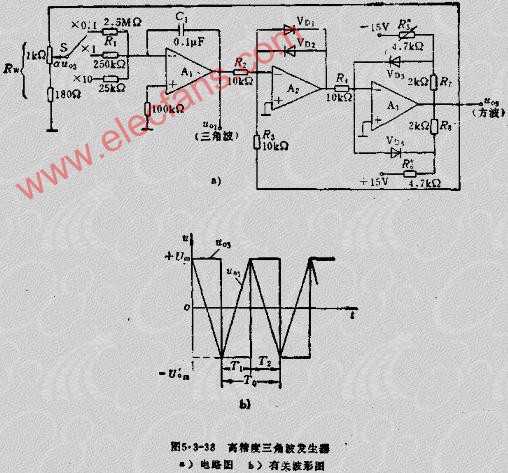

778 高精度三角波發(fā)生器

高精度三角波發(fā)生器如圖5.3-38A是由三只集成運(yùn)放組成的高精度三角波、方波產(chǎn)生電路。A1為積分電路,用來將方波轉(zhuǎn)換成三角波;A2為比

2010-04-22 14:45:56 9167

9167

實(shí)用高精度鋸齒發(fā)生器

實(shí)用高精度鋸齒發(fā)生器如圖5.3-40所示。

圖5.3-40A

2010-04-22 14:59:17 648

648

如何利用GPS OEM來進(jìn)行二次開發(fā),產(chǎn)生高精度時鐘發(fā)生器是一個研究的熱點(diǎn)問題。在電力系統(tǒng)、CDMA2000、DVB、DMB等系統(tǒng)中,高精度的GPS

2010-07-24 15:45:26 780

780 在電力系統(tǒng)、CDMA2000、DVB、DMB等系統(tǒng)中,高精度的GPS時鐘發(fā)生器(GPS同步時鐘)對維持系統(tǒng)正常運(yùn)轉(zhuǎn)有至關(guān)重要的意義。

那如何利用GPS OEM來進(jìn)行二次開發(fā),產(chǎn)生高精度時鐘發(fā)生

2010-09-17 22:02:44 1273

1273 DS1091L是一款低成本的時鐘發(fā)生器,輸出頻率由工廠預(yù)置到130kHz至66.6MHz,標(biāo)稱精度為±0.25%。器件可產(chǎn)生中心抖動或降頻抖動擴(kuò)頻輸出,具有引腳可選的抖動幅度和抖動速率。

2011-03-16 10:57:41 1036

1036

MAX3636是一個高度靈活,高精度鎖相環(huán)(PLL)時鐘發(fā)生器為下一代網(wǎng)絡(luò)設(shè)備的要求低抖動時鐘發(fā)生器和強(qiáng)大的高速數(shù)據(jù)傳輸?shù)姆植歼M(jìn)行了優(yōu)化。

2011-10-11 11:15:22 1329

1329

Silicon Laboratories (芯科實(shí)驗(yàn)室有限公司)日前宣布擴(kuò)展其PCI Express(PCIe)時鐘發(fā)生器和時鐘緩沖器產(chǎn)品組合。

2012-02-02 09:31:56 1395

1395 DS1088C是一種低成本的時鐘發(fā)生器,無需外部定時元件產(chǎn)生的方波輸出。是在工廠校準(zhǔn)的頻率為133MHz的固定頻率振蕩器。該設(shè)備具有掉電引腳為功耗敏感的應(yīng)用。

2012-03-30 17:13:43 944

944

10GHz擴(kuò)頻時鐘發(fā)生器的設(shè)計_胡帥帥

2017-01-07 21:28:58 1

1 系統(tǒng)設(shè)計師通常側(cè)重于為應(yīng)用選擇最合適的數(shù)據(jù)轉(zhuǎn)換器,在向數(shù)據(jù)轉(zhuǎn)換器提供輸入的時鐘發(fā)生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發(fā)生器、相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器、動態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。

2017-11-17 02:00:58 752

752

Microchip基于MEMS的時鐘發(fā)生器

2018-06-07 13:46:00 4534

4534

Microchip基于MEMS的時鐘發(fā)生器

2018-07-08 01:23:00 3933

3933 據(jù)麥姆斯咨詢報道,Microchip推出了業(yè)界尺寸最小的MEMS時鐘發(fā)生器DSC613。這款新器件可在電路板上最多替換掉三個晶振和振蕩器,從而減少高達(dá)80%的時鐘元件布板空間。

2018-11-15 16:38:26 3910

3910 AD9523:14路LVPECL/LVDS/HSTL輸出 或29路LVCMOS輸出 低抖動時鐘發(fā)生器

2019-07-04 06:18:00 3603

3603 TI推出超低抖動時鐘發(fā)生器,以實(shí)現(xiàn)更可靠的電信基礎(chǔ)設(shè)施設(shè)備,設(shè)計人員可以優(yōu)化系統(tǒng)性能,簡化設(shè)備配置并減少設(shè)計周期時間。

2019-08-09 15:10:28 1652

1652 系統(tǒng)設(shè)計師通常側(cè)重于為應(yīng)用選擇最合適的數(shù)據(jù)轉(zhuǎn)換器,在向數(shù)據(jù)轉(zhuǎn)換器提供輸入的時鐘發(fā)生器件的選擇上往往少有考慮。

2019-08-07 17:51:43 6011

6011

系統(tǒng)設(shè)計師通常側(cè)重于為應(yīng)用選擇最合適的數(shù)據(jù)轉(zhuǎn)換器,在向數(shù)據(jù)轉(zhuǎn)換器提供輸入的時鐘發(fā)生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發(fā)生器的相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器動態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。

2020-11-22 11:34:38 2666

2666

AD9525: 8路LVPECL輸出低抖動時鐘發(fā)生器

2021-03-21 15:00:20 0

0 AD9518-1:6輸出時鐘發(fā)生器,集成2.5 GHz壓控振蕩器數(shù)據(jù)表

2021-03-22 19:55:03 1

1 AD9540:655 MHz低抖動時鐘發(fā)生器數(shù)據(jù)表

2021-03-22 19:57:57 0

0 本文設(shè)計了一款應(yīng)用于高精度ADC片上測試的高精度高線性度模擬三角波信號發(fā)生器,可為高達(dá)14 b的ADC靜態(tài)參數(shù)片上測

2021-04-05 08:21:00 2291

2291

AD9517-2:12輸出時鐘發(fā)生器,集成2.2 GHz壓控振蕩器數(shù)據(jù)表

2021-04-13 11:57:48 0

0 AD9517-1:12輸出時鐘發(fā)生器,集成2.5 GHz壓控振蕩器數(shù)據(jù)表

2021-04-13 12:02:55 1

1 AD9517-0:12輸出時鐘發(fā)生器,集成2.8 GHz壓控振蕩器數(shù)據(jù)表

2021-04-13 12:10:21 0

0 ADF4360-9:集成壓控振蕩器數(shù)據(jù)表的時鐘發(fā)生器PLL

2021-04-14 14:10:44 0

0 AD9571:以太網(wǎng)時鐘發(fā)生器,10個時鐘輸出

2021-04-16 10:21:56 3

3 HMC1031:0.1 MHz至500 MHz時鐘發(fā)生器,帶整數(shù)N PLL數(shù)據(jù)表

2021-04-23 20:15:29 6

6 AD9520-5:12 LVPECL/24 CMOS輸出時鐘發(fā)生器數(shù)據(jù)表

2021-04-27 21:31:55 2

2 AD9516-5:14-輸出時鐘發(fā)生器數(shù)據(jù)表

2021-04-27 21:41:19 5

5 AD9551:多業(yè)務(wù)時鐘發(fā)生器數(shù)據(jù)表

2021-04-28 10:30:52 0

0 AD9517-4:12輸出時鐘發(fā)生器,集成1.6 GHz壓控振蕩器數(shù)據(jù)表

2021-04-30 15:51:42 10

10 AD9575:網(wǎng)絡(luò)時鐘發(fā)生器,雙輸出數(shù)據(jù)表

2021-05-09 11:06:44 1

1 AD9531:3通道時鐘發(fā)生器,24輸出數(shù)據(jù)表

2021-05-15 15:24:07 11

11 AD9516-3:14輸出時鐘發(fā)生器,集成2.0 GHz壓控振蕩器數(shù)據(jù)表

2021-05-25 12:00:10 2

2 AD9517-0 12輸出時鐘發(fā)生器,集成2.8 GHz壓控振蕩器數(shù)據(jù)表

2021-06-16 12:14:49 4

4 集成2.2 GHz壓控振蕩器數(shù)據(jù)表的AD9517-2 12輸出時鐘發(fā)生器

2021-06-17 12:31:30 3

3 集成2.5 GHz壓控振蕩器數(shù)據(jù)表的AD9517-1 12輸出時鐘發(fā)生器

2021-06-17 15:57:38 6

6 時鐘發(fā)生器AD9516-0技術(shù)手冊

2022-01-25 15:59:42 7

7 。Cypress時鐘發(fā)生器兼容大量增值性能,如VCXO,擴(kuò)頻和輸出相位校準(zhǔn),及其兼容流行接口標(biāo)準(zhǔn)的參考時鐘/3.0,如PCIe1.0/2.0/3.0、10GbE、SATA1.0/2.0和USB1.0

2022-04-22 09:02:09 806

806 這是帶有板上芯片(COB)的1Hz時鐘發(fā)生器電路。通常,為數(shù)字時鐘和計數(shù)器電路應(yīng)用產(chǎn)生1Hz時鐘的電路將IC與晶體和微調(diào)電容器等結(jié)合使用。

2022-06-07 10:43:50 1886

1886

超低抖動時鐘發(fā)生器如何優(yōu)化串行鏈路系統(tǒng)性能

2022-11-04 09:50:15 0

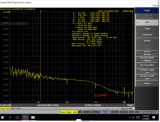

0 采用PLL的時鐘發(fā)生器廣泛用于網(wǎng)絡(luò)設(shè)備中,用于生成高精度和低抖動參考時鐘或保持同步網(wǎng)絡(luò)操作。大多數(shù)時鐘振蕩器使用理想、干凈的電源給出其抖動或相位噪聲規(guī)格。然而,在實(shí)際的系統(tǒng)環(huán)境中,電源可能會因板載開關(guān)電源或嘈雜的數(shù)字ASIC而受到干擾。為了在系統(tǒng)設(shè)計中實(shí)現(xiàn)最佳性能,了解這種干擾的影響非常重要。

2023-03-08 15:33:00 895

895

9ZXL1951D PCIe 時鐘發(fā)生器評估板用戶指南

2023-03-21 19:21:13 0

0 本文討論電源噪聲干擾對基于PLL的時鐘發(fā)生器的影響,并介紹幾種用于評估由此產(chǎn)生的確定性抖動(DJ)的測量技術(shù)。派生關(guān)系顯示了如何使用頻域雜散測量來評估時序抖動行為。實(shí)驗(yàn)室臺架測試結(jié)果用于比較測量技術(shù),并演示如何可靠地評估參考時鐘發(fā)生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 811

811

極景微發(fā)布超小封裝PCIe5.0時鐘發(fā)生器日前,極景微(UltraSilicon)宣布,推出兩款支持PCIe5.0接口標(biāo)準(zhǔn)的1輸出及2輸出時鐘發(fā)生器,分別為US6D101和US6D102。該芯片具有

2023-02-02 15:25:54 999

999

時鐘發(fā)生器由哪些部分組成?鎖相環(huán)pll的特點(diǎn)是什么?如何用硬件配置pll? 時鐘發(fā)生器是指通過特定的電路設(shè)計產(chǎn)生適合各種電子設(shè)備使用的時鐘信號的器件。時鐘發(fā)生器由多個部分組成,其中最核心的是鎖相環(huán)

2023-10-13 17:39:50 443

443 時鐘合成器和時鐘發(fā)生器是兩種用于產(chǎn)生時鐘信號的電子器件,它們在功能和應(yīng)用上有一些區(qū)別。

2023-11-09 10:26:56 298

298 的時鐘發(fā)生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發(fā)生器。然而,如果不慎重考慮時鐘發(fā)生器、相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器、動態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。...

2023-11-28 14:33:57 0

0 “核芯互聯(lián)CLG440是一顆專為高性能服務(wù)器、計算中心應(yīng)用推出的支持PCIe 6.0、符合CK440Q標(biāo)準(zhǔn)的高性能時鐘發(fā)生器。

2024-01-16 15:57:40 279

279

電子發(fā)燒友App

電子發(fā)燒友App

評論