Buck變換器的EMC分析

摘要:通過對Buck變換器電路的EMC分析,說明了電磁兼容中濾波、接地、緩沖以及合理的PCB設(shè)計(jì)等技術(shù)在開關(guān)電源中的應(yīng)用。

關(guān)鍵詞:開關(guān)電源;電磁兼容;電磁騷擾;電磁干擾;耦合通道

0??? 引言

??? 開關(guān)電源通過改變開關(guān)器件的導(dǎo)通比來有效地控制輸出電壓和電流的大小。通常它在幾十kHz以上的開關(guān)頻率下工作,當(dāng)開關(guān)導(dǎo)通時(shí),它將流過浪涌電流Cdv/dt;當(dāng)開關(guān)斷開時(shí),其兩端將會(huì)產(chǎn)生浪涌電壓Ldi/dt,形成較強(qiáng)的電磁騷擾源。隨著半導(dǎo)體開關(guān)器件的不斷發(fā)展,開關(guān)頻率將提高到MHz數(shù)量級(jí),使電磁騷擾更加嚴(yán)重。因此,必須采用相應(yīng)的措施,加強(qiáng)開關(guān)電源的電磁兼容性(EMC)。

??? 電磁兼容性是指在不損失有用信號(hào)所包含信息的條件下,信息和干擾共存的能力。電力電子裝置在其使用環(huán)境下,承受來自外部電磁干擾的同時(shí)也向周圍環(huán)境釋放干擾。在設(shè)計(jì)制造電力電子裝置時(shí),應(yīng)考慮到電力電子裝置在工作時(shí)所產(chǎn)生的電磁騷擾不對在同一環(huán)境中工作的其它電子設(shè)備的運(yùn)行產(chǎn)生不良影響,同時(shí)來自外部環(huán)境的電磁干擾又不會(huì)影響電力電子裝置的工作。

1??? Buck系統(tǒng)的電磁干擾

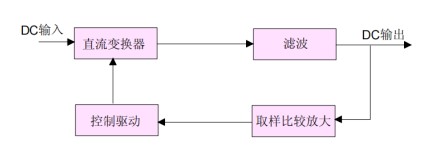

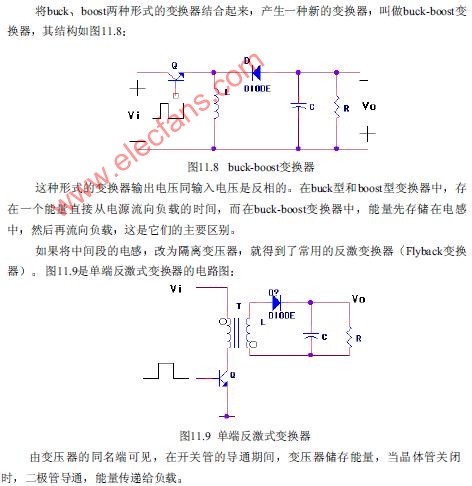

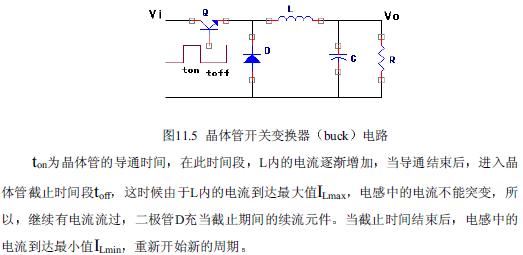

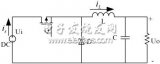

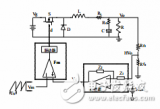

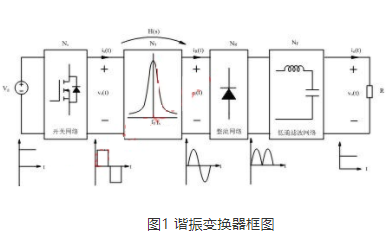

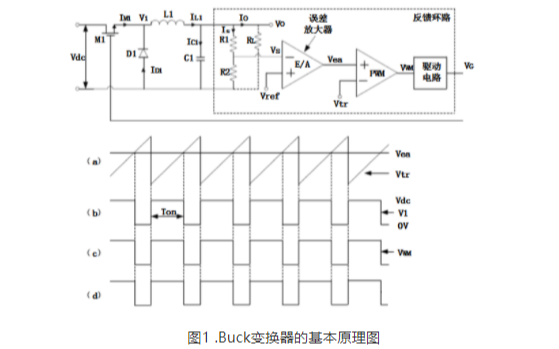

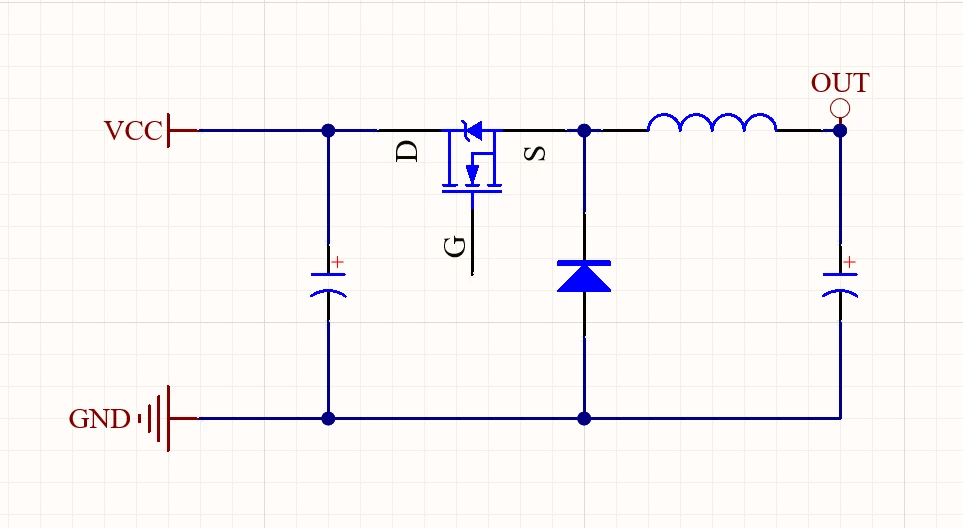

??? 以下結(jié)合Buck變換器來具體討論電磁干擾產(chǎn)生的原因和條件,從而找出抑制和消除的方法。圖1是Buck變換器的原理結(jié)構(gòu)圖。

圖1??? Buck原理結(jié)構(gòu)圖

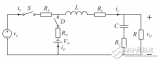

??? 主電路主要由功率開關(guān)管S、肖特基二極管D、濾波電容C、電感L、阻性負(fù)載Ro以及無感采樣電阻RL組成。此電路的基本參數(shù)是輸入端為36V鉛酸蓄電池,輸出要求為10A恒流,開關(guān)頻率為50kHz。控制芯片采用SG3525,驅(qū)動(dòng)芯片采用TLP250。輔助電源采用反激。主電路選擇合適的閉環(huán)參數(shù)是重要的一步,合適的閉環(huán)參數(shù)可以使電路穩(wěn)定,產(chǎn)生較小的EMD。

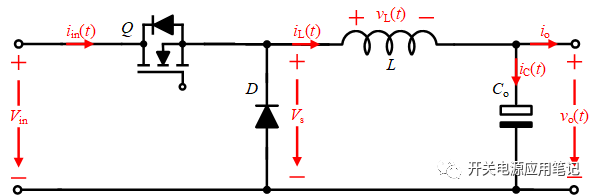

??? 圖2是該系統(tǒng)的電磁兼容性示意圖,結(jié)合此圖分析系統(tǒng)所處的電磁環(huán)境及其相互作用的情況。顯然,電磁干擾既可發(fā)生在系統(tǒng)內(nèi)部,又有可能發(fā)生在系統(tǒng)之間。

圖2??? 系統(tǒng)的電磁兼容性示意圖

??? 從圖2中可以看出,任何一種EMI均由三部分組成:騷擾源、耦合路徑和受擾體。騷擾源產(chǎn)生的干擾經(jīng)耦合途徑進(jìn)入受擾體,若干擾水平超出受擾體的敏感程度就會(huì)影響其正常工作而構(gòu)成干擾。與數(shù)字電路相比,由于開關(guān)電源功率開關(guān)管的高速開關(guān)動(dòng)作,它產(chǎn)生的干擾強(qiáng)度較大;騷擾源主要集中在功率開關(guān)器件以及與之相連的高頻變壓器上;開關(guān)頻率不高,主要干擾形式是傳導(dǎo)干擾和近場干擾。一般解決EMD針對3方面:抑制騷擾源、切斷干擾途徑和提高受擾體的抗干擾能力。

??? 由此可知Buck的主要騷擾源是開關(guān)管和功率二極管。由于開關(guān)頻率較高,傳輸?shù)哪芰坑执螅试陂_關(guān)過程中會(huì)產(chǎn)生很高的毛刺。

??? 由于設(shè)計(jì)的開關(guān)電源的幾何尺寸遠(yuǎn)小于30MHz電磁場對應(yīng)的波長,因此,電磁干擾主要考慮的是傳導(dǎo)干擾。MOSFET在開關(guān)過程中產(chǎn)生的電壓尖峰和振蕩主要通過導(dǎo)線寄生電感和寄生電容干擾受擾體,開關(guān)過程越快,尖峰越高,振蕩越明顯,干擾越強(qiáng)。

2??? 電磁干擾的抑制措施

??? 主要從濾波、接地、吸收、PCB布板幾個(gè)方面進(jìn)行分析和設(shè)計(jì)。

2.1??? 濾波

??? 由于電池存在一定的內(nèi)阻抗,再加上入端引線上的寄生電感和內(nèi)阻,將在輸入端引起一系列的高頻紋波。為了使輸入端成為滿足要求的恒壓源,需在電路進(jìn)線端加上EMI濾波器,既抑制了外界對電路的干擾,也阻止了電路對電池的干擾。通常,在入端并聯(lián)電解電容和濾高頻紋波的電容。電解電容主要濾低頻紋波,濾高頻紋波的電容采用CBB電容。

??? 由于輸出端對電流波形的要求,必須減小輸出紋波的大小,因此,也需要在輸出端并聯(lián)大容量的電解電容和較大容量的濾高頻紋波的CBB電容。

??? 另外,需要對集成芯片的去耦濾波電容進(jìn)行科學(xué)的配置。每塊集成芯片都接有去耦濾波電容器,在每次開關(guān)過程中都重新充電,以便為芯片供電,去耦電容器的取值一般在470pF~1000pF,采用瓷片或者是CBB電容,用于濾除高次紋波。去耦濾波電容器必須緊靠集成電路安裝,力求最短的電容器引線和最小的瞬態(tài)電流回路面積。同時(shí)要在整個(gè)集成芯片的PCB板上放置總體去耦電容器,由電源來對它充電,并應(yīng)安裝在電源母線進(jìn)入PCB板的地方。

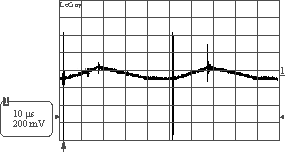

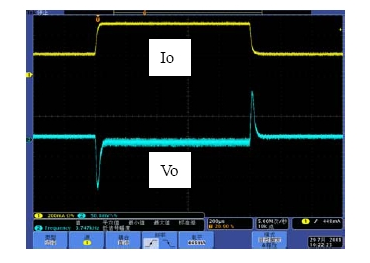

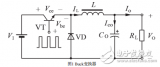

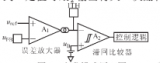

??? 系統(tǒng)中最易受干擾的是電流采樣電阻,而采樣電流的精度將直接影響電路的輸出指標(biāo)。采樣電流的波形如圖3所示。由于采樣電阻受到開關(guān)管導(dǎo)通和關(guān)斷的干擾,所以,需要對采樣電阻上的信號(hào)進(jìn)行濾波,此電路中利用的RC二階無源濾波,電路如下圖4所示。

圖3??? 采樣電流波形

圖4??? 二階RC無源濾波電路

2.2??? 接地

??? 一個(gè)系統(tǒng)的接地主要有安全地、信號(hào)地、機(jī)殼地和屏蔽地。這里只討論本系統(tǒng)的公共地的連接方法。

??? 1)接地系統(tǒng)須具有很低的公共阻抗,使系統(tǒng)中各路電流,通過該公共阻抗產(chǎn)生的直接傳導(dǎo)噪聲電壓最小。

??? 2)在高頻電流的場合,保證“信號(hào)地”對“大地”有較低的共模電壓,使通過“信號(hào)地”產(chǎn)生的輻射噪音最低。

??? 3)保證地線與信號(hào)線構(gòu)成的電流回路具有最小的面積,避免由地線構(gòu)成“地回路”,使外界干擾磁場穿過該回路產(chǎn)生的差模干擾電壓最小,同時(shí),也避免由地電位差通過地回路引起過大的地電流,造成傳導(dǎo)干擾。

??? 本系統(tǒng)中采用混合接地和浮空接地方式。主功率采用浮地方式,以便減小公共阻抗和大電流的通過。控制系統(tǒng)內(nèi)部先串聯(lián)接地,然后再單點(diǎn)與主功率地連接。驅(qū)動(dòng)電路則采用光耦隔離技術(shù)來驅(qū)動(dòng)開關(guān)管的導(dǎo)通和關(guān)斷。

2.3??? 緩沖

??? 在采用了以上措施后,發(fā)現(xiàn)MOSFET的開關(guān)過程中毛刺仍然較高,這是由于電路中流過的電流比較大,很小的寄生電感也能引起很大的毛刺。

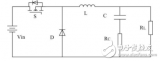

??? 緩沖電路的目的是對開關(guān)管產(chǎn)生的瞬態(tài)噪聲進(jìn)行抑制。采用的是在開關(guān)管兩端并上R—C—D網(wǎng)絡(luò)進(jìn)行抑制,它可以減緩開關(guān)管的漏極和源極之間的電壓上升率,如圖5所示。

圖5??? R—C—D吸收電路

??? 通過給開關(guān)管加緩沖電路后,可以得到比較理想的開關(guān)波形,如圖6所示。

圖6??? 開關(guān)管vDS波形

??? 在關(guān)斷過程中由于功率二極管會(huì)有反向恢復(fù),這是一個(gè)重要的騷擾源。

??? RC緩沖電路是解決功率二極管反向恢復(fù)問題的常用方法。在高頻下工作的功率二極管,要考慮寄生參數(shù)。圖7(a)為電路模型,其中D0為理想二極管,Lp為引線電感,Cp為結(jié)電容,Rp為并聯(lián)電阻(高阻值),Rs為引線電阻。如圖7(b)所示,將電容C和電阻R串聯(lián)后并聯(lián)到功率二極管D上。二極管反向關(guān)斷時(shí),寄生電感中的能量對寄生電容充電,同時(shí)還通過緩沖電阻R對緩沖電容C充電。在同樣能量的情況下,緩沖電容越大,其上的電壓就越小;當(dāng)二極管正向?qū)〞r(shí),C通過R放電,能量絕大部分在R上消耗。

(a)等效模型??? (b)RC緩沖電路

圖7??? 功率二極管等效模型及RC緩沖電路

??? 通過在功率二極管上并R—C緩沖電路后,可以得到比較理想的開通和反向關(guān)斷波形,如圖8所示。

圖8??? 功率二極管上的波形

2.4??? PCB布板

??? 印刷電路板上元器件的放置和布線設(shè)計(jì)對開關(guān)電源EMC性能有極大的影響,在高頻開關(guān)電源中,由于印刷板上既有低電平的小信號(hào)控制線,又有高壓大電流電源線,同時(shí)還有一些高頻功率開關(guān)、磁性元件。如何在印刷板有限的空間內(nèi)合理地安排元器件位置,以及合理地布線將直接影響到電路中各元器件自身的抗干擾性和電路工作的可靠性。

??? 通過分析印刷導(dǎo)線的特性阻抗,合理地選取布線的放置方式、長度、寬度以及總體布局。單根導(dǎo)線的特性阻抗由直流電阻R和自感L組成。

??? Z=R+jωL(1)

??? L=2lln(2)

式中:l為印刷導(dǎo)線的長度;

????? b為印刷導(dǎo)線的寬度。

??? 可以看出印刷線l越短,直流電阻R越小,自感L也就越小;同時(shí)增加印刷線的寬度也可以降低直流電阻R和自感L。

??? 多根印刷線的特性阻抗除了直流電阻R和自感L以外,還有互感M。

??? M=2l(3)

式中:s為兩線之間的距離。

??? 由以上分析可知,在設(shè)計(jì)印刷電路板時(shí),應(yīng)盡量降低電源線和地線的阻抗。因電源線、地線和其它印刷線都有電感,當(dāng)電源電流變化較大時(shí),會(huì)產(chǎn)生較大壓降,而地線壓降是形成公共阻抗干擾的重要因素,所以應(yīng)盡量縮短地線,盡量加寬電源線和地線。

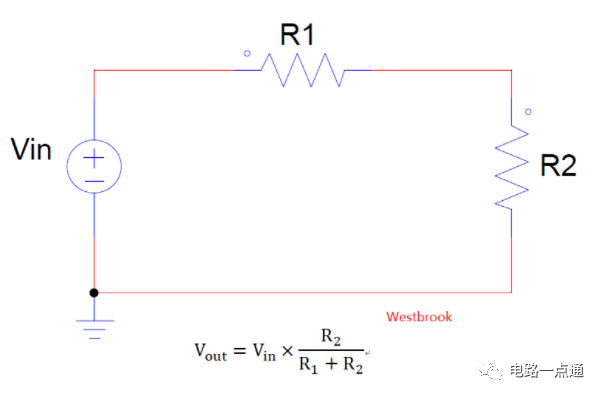

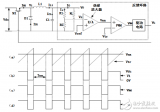

??? 直流供電系統(tǒng)的實(shí)際等效電路如圖9所示。

圖9??? 直流供電系統(tǒng)等效電路

??? 直流供電電路中產(chǎn)生的瞬態(tài)噪聲電壓,起源于電源負(fù)載電流的突變?chǔ)L。該電流變化是瞬時(shí)的,則因之產(chǎn)生的瞬變電壓的幅值ΔuL是電源供電傳輸線特征阻抗Z0的函數(shù)。

??? Z0=(4)

??????? ΔuL=ΔiLZ0(5)

??? 為了減小ΔuL,必須使得Z0盡量低,由式(4)可知,要求Lt盡量小,Ct盡量大。為了減小Lt和增大Ct,供電母線應(yīng)用矩形截面的導(dǎo)線,并使兩條母線盡量靠近,用兩條盡量寬的扁平印刷線。由于使用的是雙面印刷板,電源線和地線平行布線,使兩條功率線流過的電流方向相反,可以有效地減小感應(yīng)磁通。同時(shí)也將其它正、負(fù)信號(hào)線分別布在印刷板的兩面,設(shè)法使兩個(gè)載流體導(dǎo)線彼此間保持平行,因?yàn)槠叫芯o靠的正、負(fù)載流體導(dǎo)體所產(chǎn)生的外部磁場是趨向于相互抵消的。

??? 對于元器件的放置,由于開關(guān)電源的輻射干擾(E)與電流通路中電流(I)的大小,通路的環(huán)路面積(A),以及電流頻率(f)的平方等三者的乘積成正比,即E=I·A·f2。運(yùn)用這一關(guān)系的前提是通路尺寸遠(yuǎn)小于頻率的波長(此電路符合條件)。

??? 利用上述關(guān)系式,減小通路面積是減小輻射干擾的關(guān)鍵。在此Buck電路中,應(yīng)該使輸入端電容、開關(guān)管、功率二極管彼此緊靠,且布線緊湊;同時(shí)使輸出端功率二極管、電感、輸出電容、采樣電阻彼此緊靠。

??? 另外,在布線時(shí)使開關(guān)管的漏極連線盡量短、粗,以減小導(dǎo)線的寄生電感。選擇合適的濾高頻電容(樣機(jī)中使用了CBB電容),并使其盡量靠近MOSFET的漏極,電容引線盡量短,以減小導(dǎo)線電感。

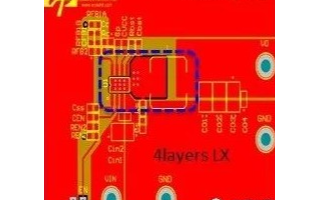

??? 根據(jù)以上的分析所得出的原則,實(shí)際設(shè)計(jì)的樣機(jī)主功率PCB板如圖10所示。

圖10??? Buck電路的PCB板

3??? 結(jié)語

??? 開關(guān)電源電磁兼容設(shè)計(jì)的目的,就是使所設(shè)計(jì)的產(chǎn)品不但能在一定的電磁干擾環(huán)境中正常工作,而且也使產(chǎn)品自身所產(chǎn)生的電磁騷擾不影響其它設(shè)備的工作。本文通過各個(gè)方面的分析,總結(jié)出設(shè)計(jì)Buck電路電磁兼容的原則,并依此原則制造出試驗(yàn)樣機(jī),從而在實(shí)踐的基礎(chǔ)上說明了這些原則的可行性和正確性,為以后開關(guān)電源的電磁兼容設(shè)計(jì)提供了很好的經(jīng)驗(yàn)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論