|

現(xiàn)場可編程門陣列的結(jié)構(gòu)與設(shè)計?? 摘要:現(xiàn)場可編程門陣列(FPGA——Field Programmable Gate Array)是上世紀(jì)80年代末發(fā)展起來的新型大規(guī)模集成邏輯器件。它采用高級計算機(jī)輔助設(shè)計技術(shù)進(jìn)行器件的開發(fā)與設(shè)計,其優(yōu)越性大大超過普通TTL集成門。重點介紹了FPGA的基本組成原理及設(shè)計方法。 關(guān)鍵詞:現(xiàn)場可編程門陣列;可配置邏輯塊;專用集成電路

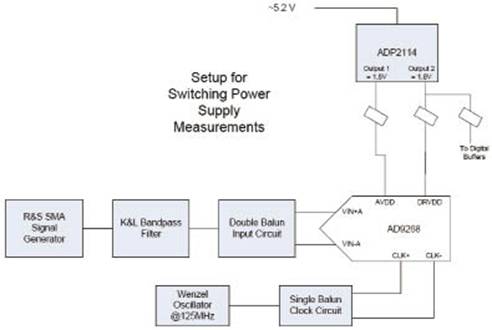

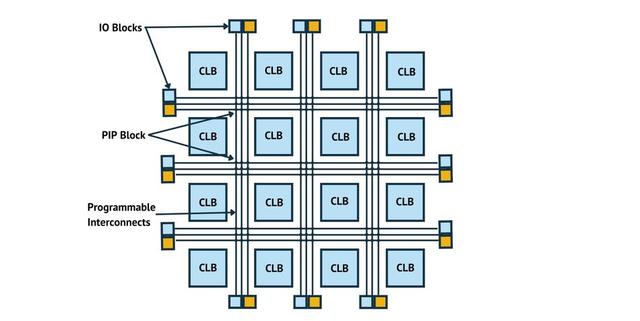

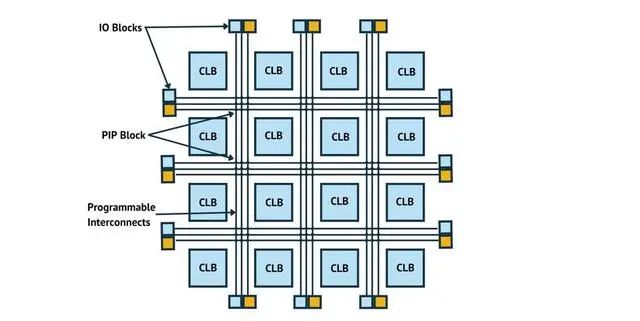

1??? 引言 ??? FPGA是上世紀(jì)80年代末開始使用的大規(guī)模可編程數(shù)字集成電路器件。它充分利用計算機(jī)輔助設(shè)計技術(shù)進(jìn)行器件的開發(fā)與應(yīng)用。用戶借助于計算機(jī)不僅能自行設(shè)計專用集成電路芯片,還可在計算機(jī)上進(jìn)行功能仿真和實時仿真,及時發(fā)現(xiàn)問題,調(diào)整電路,改進(jìn)設(shè)計方案。這樣,設(shè)計者不必動手搭接電路、調(diào)試驗證,只須在計算機(jī)上操作很短的時間,即可設(shè)計出與實際系統(tǒng)相差無幾的理想電路。而且,F(xiàn)PGA器件采用標(biāo)準(zhǔn)化結(jié)構(gòu),體積小、集成度高、功耗低、速度快,可無限次反復(fù)編程,因此,成為科研產(chǎn)品開發(fā)及其小型化的首選器件,其應(yīng)用極為廣泛。 2??? FPGA的基本組成原理 ??? FPGA的基本組成與生產(chǎn)廠家有關(guān),不同廠家的器件其結(jié)構(gòu)、工藝技術(shù)和編程方法各不相同。目前國內(nèi)廣泛使用Xilinx公司生產(chǎn)的FPGA器件。XilinxFPGA采用邏輯單元陣列(Logic Cell Array—簡稱LCA)結(jié)構(gòu),其示意圖如圖1所示。 圖1??? Xilinx公司FPGA結(jié)構(gòu)圖 ??? 由圖1可知,XilinxFPGA由3個可編程基本單元陣列組成:輸入/輸出塊(I/OBlock—簡稱I/OB)陣列,可配置邏輯塊(Configurable LogicB lock—簡稱CLB)陣列及可編程互連網(wǎng)絡(luò)(Programmable Interconnect—簡稱PI)。其中輸入/輸出塊排列在芯片周圍,它是可配置邏輯塊與外部引腳的接口。可配置邏輯塊是FPGA的核心,它以矩陣形式排列在芯片中心。每個CLB均可實現(xiàn)一個邏輯功能小單元。各CLB之間通過互連網(wǎng)絡(luò)編程連接,以實現(xiàn)復(fù)雜的邏輯功能。 3??? FPGA的開發(fā)過程 ??? FPGA的開發(fā)過程依賴于它的軟件開發(fā)系統(tǒng),其設(shè)計流程如圖2所示。 ??? 由圖2可知,F(xiàn)PGA的基本設(shè)計流程分為3部分:設(shè)計輸入,設(shè)計實現(xiàn)及設(shè)計驗證。 圖2FPGA的基本設(shè)計流程 3.1??? 設(shè)計輸入 ??? 設(shè)計輸入是將要實現(xiàn)的邏輯關(guān)系以開發(fā)系統(tǒng)所支持的方式輸入計算機(jī),這是設(shè)計FPGA的開始。有多種方法實現(xiàn)設(shè)計輸入,最常用的是原理圖編輯器。它允許用2種方式進(jìn)行設(shè)計輸入: ??? 1)圖形輸入這種輸入方式允許使用元件庫中提供的各種常規(guī)門電路及邏輯部件(宏單元)設(shè)計電路,并以原理圖的方式輸入; ??? 2)文本輸入這種輸入方式允許使用高級可編程邏輯設(shè)計語言,如VHDL,ABEL、CUPL語言等編寫輸入文件,也允許直接用布爾方程進(jìn)行輸入。 ??? 設(shè)計輸入的目的是要產(chǎn)生一個XNF(Xilinx Netlist Format)文件,這是設(shè)計實現(xiàn)和設(shè)計驗證的輸入文件。如果同時采用圖形輸入和文本輸入,則還需要進(jìn)行歸并(XNFMERGE)處理,以產(chǎn)生一個完整的XNF文件。 3.2??? 設(shè)計實現(xiàn) ??? 設(shè)計實現(xiàn)是設(shè)計開發(fā)過程的核心,其主要任務(wù)是對歸并后的XNF文件進(jìn)行分割、布局和布線。分割是把XNF文件中的邏輯設(shè)計經(jīng)過化簡,分割成為以CLB及I/OB為基本單元的邏輯設(shè)計。布局是把分割后的邏輯設(shè)計分配到FPGA的相應(yīng)CLB及I/OB位置。布線是對已布局好的CLB,I/OB進(jìn)行連線。Xilinx開發(fā)軟件具有自動布局、布線功能,它能在布局、布線過程中采用一系列優(yōu)化程序,找出最佳布局、布線方案。設(shè)計實現(xiàn)的最終目的是產(chǎn)生符合設(shè)計要求的比特流文件。這是用來為FPGA芯片裝載的二進(jìn)制文件。 3.3??? 設(shè)計驗證 ??? 設(shè)計驗證主要是對電路進(jìn)行仿真測試。仿真測試包括功能仿真和實時仿真。功能仿真假設(shè)信號通過每個邏輯門產(chǎn)生同樣的延遲時間(0.1ns),而通過路徑?jīng)]有延時。這種仿真可測試系統(tǒng)功能是否滿足設(shè)計要求。實時仿真是在布局布線后進(jìn)行,它能按照所選器件的實際延遲時間進(jìn)行模擬,主要用來驗證系統(tǒng)的時序關(guān)系。 ??? 設(shè)計輸入、設(shè)計實現(xiàn)和設(shè)計驗證三個部分交替進(jìn)行,最后得到完全滿足設(shè)計要求的二進(jìn)制文件。用該文件通過加載電纜或編程EPROM對FPGA加載,即可得到用戶需要的專用集成電路芯片。 4??? FPGA設(shè)計方法 4.1??? 時鐘信號分配技術(shù) ??? 時鐘分配網(wǎng)絡(luò)是FPGA芯片中的特殊布線資源,由特定的引腳和特定的驅(qū)動器驅(qū)動,只能驅(qū)動芯片上觸發(fā)器的時鐘輸入端或除了時鐘輸入端外有限的一些負(fù)載,其反相功能一般可在可編程邏輯塊(CLB)或可編程輸入輸出塊(I/OB)內(nèi)部實現(xiàn),其目的是為設(shè)計提供小延遲偏差的時鐘信號。因此,F(xiàn)PGA特別適合于同步電路設(shè)計技術(shù),盡可能減少使用的時鐘信號種類。而在TTL電路設(shè)計中經(jīng)常采用的由組合邏輯生成多個時鐘,然后分別驅(qū)動多個觸發(fā)器以裝入和保持?jǐn)?shù)據(jù)的設(shè)計方法,對FPGA設(shè)計是不適用的。因為,這樣做會使得時鐘種類很多,不能利用專用的時鐘驅(qū)動器和專用的時鐘布線資源,時鐘信號只能由通用的布線資源拼湊而成,各個負(fù)載點上的時鐘延遲偏差很大,會引起數(shù)據(jù)保持時間問題,降低工作速度。 ??? 對FPGA設(shè)計而言,更有效的方法是使用一個時鐘信號,而由組合邏輯生成多個時鐘使能信號,分別驅(qū)動觸發(fā)器的時鐘使能端,所有觸發(fā)器的數(shù)據(jù)裝入都由同一個時鐘控制,但只有時鐘使能信號有效的觸發(fā)器才會裝入數(shù)據(jù),時鐘使能信號無效的觸發(fā)器則保持?jǐn)?shù)據(jù)。這種方法充分發(fā)揮了FPGA器件體系結(jié)構(gòu)的優(yōu)勢,是設(shè)計者應(yīng)該盡量使用的設(shè)計技巧。 4.2??? 人工干預(yù)自動布局布線 ??? 經(jīng)過FPGA生產(chǎn)廠家的不斷努力,F(xiàn)PGA自動設(shè)計工具逐漸趨于完善,可以獲得較高的布通率和芯片資源利用率。對一般應(yīng)用,使用自動設(shè)計工具往往就可以了。但對于一些性能要求較高或者邏輯功能比較復(fù)雜的設(shè)計來說,F(xiàn)PGA自動設(shè)計工具的自動布局、布線結(jié)果往往不能滿足要求,此時比較有效的方法就是在原理圖一級手工干預(yù)邏輯分割和布局布線,以及使用強(qiáng)迫文件(CST文件)干預(yù)自動布局布線。對于XC200,XC300系列FPGA設(shè)計,用戶可使用CLBMAP機(jī)制控制邏輯分割,將某些功能映射到特定的可編程邏輯塊(CLB)中;對于XC400系列的FPGA設(shè)計,可使用FMAP和HMAP機(jī)制實現(xiàn)邏輯分割。此外,可以通過元件符號定位機(jī)制(LOC=)控制觸發(fā)器、三態(tài)驅(qū)動器、可編程邏輯塊等在芯片中的指定位置。一般來說,使用三態(tài)驅(qū)動器構(gòu)成內(nèi)部三態(tài)總線和使用XC4000系列的硬宏單元時人工指定位置,否則自動布局布線的結(jié)果往往很差。

??? 重復(fù)設(shè)置相同的電路單元以盡可能地減輕信號負(fù)載和縮短互連延遲,是FPGA設(shè)計中獲取高性能的一種常用方法。同時,在使用多片F(xiàn)PGA芯片時,重復(fù)設(shè)置相同的電路單元,可以減少對FPGA芯片引腳數(shù)量的需求。因為,隨著FPGA芯片引腳數(shù)的增加,其成本也大幅度增加。在設(shè)計中采用此項技術(shù),對降低成本取得了較好的效果。 5??? 結(jié)語 ??? FPGA是一種非常有前途的新技術(shù),很適合于科研工作中的樣機(jī)、新產(chǎn)品及一些生產(chǎn)量不是特別大的產(chǎn)品。對于批量較大產(chǎn)品可以通過板圖優(yōu)化制成ASIC以降低成本。本文主要是針對XILINX公司的XC300,XC400系列FPGA及其開發(fā)工具來進(jìn)行討論的。正確使用FPGA的資源及其設(shè)計工具,使之適合FPGA體系結(jié)構(gòu)的特點,對設(shè)計結(jié)果的影響非常大。 |

現(xiàn)場可編程門陣列的結(jié)構(gòu)與設(shè)計

- 可編程(39058)

相關(guān)推薦

五大優(yōu)勢凸顯 可編程邏輯或?qū)⒊尸F(xiàn)快速增長

可編程邏輯器件的兩種類型是現(xiàn)場可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。在這兩類可編程邏輯器件中,F(xiàn)PGA是在PAL、GAL、EPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。

2016-01-04 17:55:08 1404

1404

1404

1404如何使用可編程邏輯為按鈕輸入消抖:一個有效的消抖邏輯電路

可編程邏輯具有傳統(tǒng)分立 IC 無法提供的靈活性。 借助現(xiàn)成的開發(fā)工具,可輕松使用現(xiàn)場可編程門陣列和復(fù)雜可編程邏輯器件創(chuàng)建應(yīng)用特定型功能。 按鈕開關(guān)輸入消抖便是此類功能的一個例子

2017-09-06 16:15:51 9262

9262

9262

9262

用于下一代汽車專用集成電路(ASIC)的嵌入式現(xiàn)場可編程邏輯門陣列(eFPGA)

用于下一代汽車專用集成電路(ASIC)的嵌入式現(xiàn)場可編程邏輯門陣列(eFPGA)

2020-07-24 11:26:52 1234

1234

1234

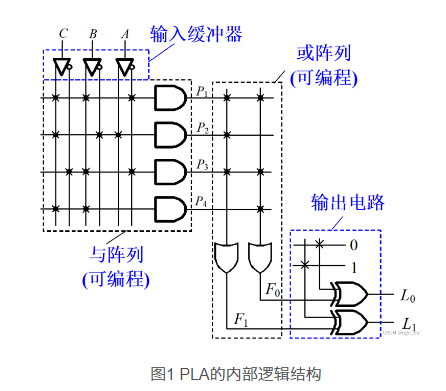

1234可編程邏輯陣列PLA內(nèi)部邏輯結(jié)構(gòu)示意

可編程邏輯陣列(Programmable Logic Array,PLA)和可編程陣列邏輯(Programmable Array Logic,PAL)都是數(shù)字邏輯電路中常見的可編程邏輯設(shè)備,但它們有一些根本上的區(qū)別。

2024-02-02 11:41:30 350

350

350

350

10M04SCM153C8G現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列MAX? 10包裝托盤零件狀態(tài)在售電壓 - 供電2.85V ~ 3.465V安裝類型表面貼裝型工作溫度0°C

2021-04-28 15:40:58

10M40DAF484C8G現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列MAX? 10包裝托盤零件狀態(tài)在售電壓 - 供電1.15V ~ 1.25V安裝類型表面貼裝型工作溫度0°C ~ 85

2021-04-28 15:37:46

5AGXFA7H4F35I5G現(xiàn)場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現(xiàn)場可編程門陣列)制造商Intel系列Arria V GX包裝托盤零件狀態(tài)在售電壓 - 供電1.07V ~ 1.13V安裝類型表面貼裝型工作溫度-40°C

2021-04-28 15:32:26

可編程技術(shù)的引爆點

25年前,賽靈思(Xilinx)公司發(fā)明了FPGA(現(xiàn)場可編程門陣列)。如今,以FPGA為代表的可編程芯片應(yīng)用已經(jīng)成為勢不可擋的發(fā)展趨勢,尤其在ASSP和傳統(tǒng)ASIC之間出現(xiàn)的市場缺口上,F(xiàn)PGA將開辟出新的領(lǐng)域,而目前席卷全球的金融危機(jī)更是成為FPGA迅速發(fā)展的催化劑。

2019-07-25 08:05:19

可編程模擬的各種架構(gòu)

是今天FPGA(現(xiàn)場可編程門陣列)流的混合信號版。可配置模擬IC已經(jīng)出現(xiàn)了多年,表面看來對市場的影響不及其數(shù)字同胞FPGA(現(xiàn)場可編程門陣列)。不過,當(dāng)前的經(jīng)濟(jì)形勢卻使可編程模擬標(biāo)準(zhǔn)產(chǎn)品的概念突然顯現(xiàn)出

2019-07-05 07:51:19

可編程邏輯器件

完成乘法,實現(xiàn)3×4,只要通過寫程序讓3連續(xù)加4次就可以完成了。而可編程邏輯器件的兩種主要類型是現(xiàn)場可編程門陣列(FPGA)和復(fù)雜可編程邏輯器件(CPLD)。 在這兩類可編程邏輯器件中,F(xiàn)PGA提供了

2014-04-15 10:02:54

可編程邏輯器件和ASIC,兩者有什么不同區(qū)別?

ASIC。PLD的種類較多,目前廣泛使用的PLD器件主要是復(fù)雜可編程邏輯器件CPLD(Complex Programmable Logic Device)和現(xiàn)場可編程門陣列FPGA(Field

2021-07-13 08:00:00

電子發(fā)燒友App

電子發(fā)燒友App

評論