|

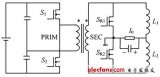

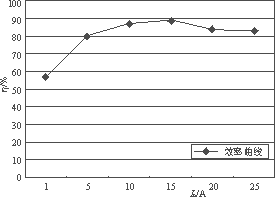

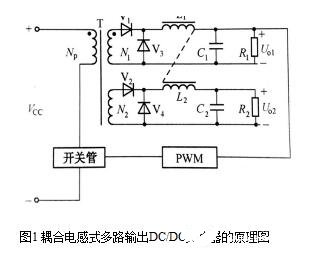

隔離式低壓/大電流輸出DC/DC變換器中幾種副邊整流電路的比較 1引言 隨著計算機(jī)通信設(shè)備及新的網(wǎng)絡(luò)產(chǎn)品市場需求的迅速增長,未來的電源市場是非常樂觀的。市場對小功率變換器的需求更是呈現(xiàn)迅速上升趨勢。據(jù)專家預(yù)測[1?2],在今后五年內(nèi),小功率DC/DC變換器的發(fā)展趨勢是:適應(yīng)超高頻CPU芯片的迅速發(fā)展,DC/DC變換器將向低輸出電壓(最低可低到1.2V)、高輸出電流、低成本、高頻化(400~500kHz)、高功率密度、高可靠性(MTBF≥106h)、高效率的方向發(fā)展。 整流電路作為DC/DC變換器的重要組成部分,對整機(jī)性能的影響很大。傳統(tǒng)的整流電路采用功率二極管,由于二極管的通態(tài)壓降較高(典型值有0.4V~0.6V),因此整流損耗較大。而為了滿足各種數(shù)據(jù)處理集成電路對更快速、更低功耗和更高集成度的要求,集成芯片工作電壓將進(jìn)一步降低到1V~3V(現(xiàn)今的典型值為2.8V~3.3V)。在DC/DC變換器輸出如此低的電壓時,整流部分的功耗占輸出功率的比重將更大,致使整機(jī)效率更低,成為電源小型化、模塊化的障礙。應(yīng)用同步整流技術(shù),用低導(dǎo)通電阻MOSFET代替常規(guī)整流二極管,可以大大降低整流部分的功耗,提高變換器的性能,實現(xiàn)電源的高效率,高功率密度[3?4]。 考慮到DC/DC變換器副邊整流電路的多樣化,本文針對低壓/大電流輸出DC/DC變換器,對幾種常用的副邊整流電路進(jìn)行分析比較,對倍流整流拓?fù)溥M(jìn)行了較詳細(xì)的闡述,希望能對電源設(shè)計有所幫助。 2副邊整流電路的回顧 2.1幾種常見的副邊整流電路 如圖1、圖2(a)、圖3(a)、圖4(a)所示,分別為全橋整流、半波整流、全波整流和倍流整流拓?fù)洹H珮蛘鞅绕渌N整流方式多用兩個整流管,使導(dǎo)通損耗大大增加,因而不太適合用于低壓/大電流輸出場合。故在下文中,未把全橋整流方式作為比較的對象。 基于半波整流和全波整流方式比較常用,這里不

圖1全橋整流

圖2半波整流拓?fù)浼捌湓聿ㄐ?a)二極管半波整流(b)MOSFET半波整流(SR)(c)原理波形

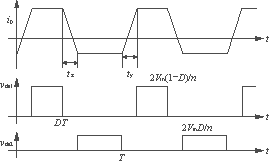

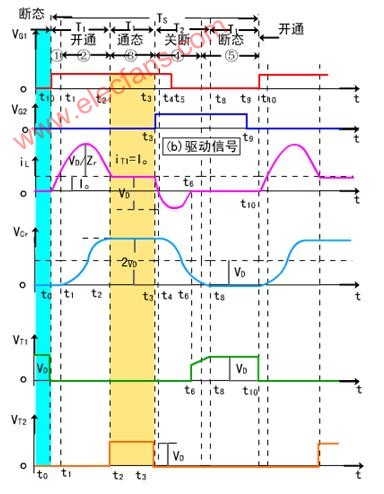

圖3全波整流拓?fù)浼捌湓聿ㄐ? (a)二極管全波整流(b)MOSFET全波整流(c)原理波形 再作原理贅述,而著重對最近幾年比較熱門的“新型”整流拓?fù)洹读髡鞣绞竭M(jìn)行較詳細(xì)的原理分析。 2.2倍流整流電路的原理分析 早在1919年,“倍流整流”思想[5]在汞弧管整流電路中就有人提出,但沒有受到重視。隨著最近幾年低壓/大電流輸出DC/DC變換器的研究熱潮,這種整流思想又重新得到了重視。它是從全橋整流方式演化而來,即用兩只獨(dú)立的,數(shù)值相同的電感代替全橋整流拓?fù)渲械囊唤M整流管,仍保持“全橋整流”的形式,經(jīng)過適當(dāng)變形,即得到圖4所示的拓?fù)湫问健D5給出全橋整流—倍流整流這一演化過程的示意簡圖。 如圖4所示,VSEC是變壓器副邊繞組電壓波形。下面對一個周期TS中,電路的工作情況進(jìn)行簡要分析[6]。 (1)t0—t1:變壓器副邊繞組上為正壓,SR2(D2)處于導(dǎo)通狀態(tài),SR1(D1)處于關(guān)斷狀態(tài)(SR1與D1,SR2與D2的開關(guān)狀態(tài)分別對應(yīng)一致,下文以SR管說明工作原理),電感L1上電流上升,L2上電流下降。對應(yīng)如下關(guān)系式:VL1=V2-V0=L1(1)VL2=-V0=L2(2)

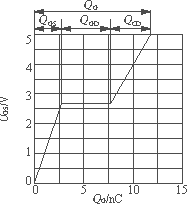

圖4倍流整流拓?fù)浼捌湓聿ㄐ? (a)二極管倍流整流(b)MOSFET倍流整流(c)原理波形 (2)t1—t2:變壓器副邊繞組電壓為零,整流管SR1、 SR2都導(dǎo)通。通過電感L1、L2的電流都在減小,處于續(xù)流狀態(tài)。對應(yīng)關(guān)系式為:VL1=-V0=L1(3)VL2=-V0=L2(4) (3)t2—t3:變壓器副邊繞組上為負(fù)壓,功率管SR1 處于導(dǎo)通狀態(tài),SR2處于關(guān)斷態(tài),電感L1上電流下降,L2上電流上升。對應(yīng)關(guān)系式為:VL1=-V0=L1(5)VL2=V2-V0=L2(6) (4)t3—t4:變壓器副邊繞組電壓為零,整流管SR1、SR2都導(dǎo)通。通過電感L1、L2的電流都在減小,處于續(xù)流狀態(tài)。對應(yīng)電路方程與t1—t2時段相同。 在一個完整的開關(guān)周期Ts中,通過電感L1、L2的電流,都是在各自的0~DTs時間段內(nèi)增加;在(1-D)Ts時間段內(nèi)減小,且兩段時間內(nèi)電流增加量與減小量相等。對應(yīng)如下關(guān)系式:L=V2-V0,L=V0,Δi(+)=Δi(-) 整理后可得: V0=DV2(7) 式中:D=tON/Ts 倍流整流,其實質(zhì)就是兩個電感的交錯并聯(lián)。電感L1與L2上的電壓和流過電流相位相差180°,在變壓器副邊繞組電壓非零時,流過L1、L2的電流一增一減,實現(xiàn)了iL1、iL2的紋波電流互消,從而使總的負(fù)載電流(i0=iL1+iL2)紋波大大減小。在輸出電壓紋波要求相同的情況下,這種倍流整流方式使得L1、L2顯著減小,加快了功率級的動態(tài)響應(yīng)。 電感L1、L2電流波形相差180°,其合成電流(i0=iL1+iL2)紋波峰峰值與iL1、iL2紋波峰峰值的關(guān)系,用電流互消比例K12表示,K12與占空比D有關(guān),關(guān)系式如下:K12=2-(D≤0.5)(8) 其對應(yīng)的關(guān)系如圖6所示。從圖6可以直觀地看出,當(dāng)D=0.5,即V2=2V0時,才有完全的紋波互消作用(輸出電流實現(xiàn)零紋波),D偏離0.5越遠(yuǎn),紋波互消作用越差。當(dāng)D=0.25時,紋波互消比例只有67%。因此,在倍流整流拓?fù)渲校瑸榱死闷浼y波互消作用,希望D在0.5附近。 3幾種整流電路的比較 為了充分認(rèn)識半波整流、全波整流和倍流整流拓?fù)涞膬?yōu)缺點,便于優(yōu)化選擇,下面從整流管導(dǎo)通損耗,磁性元件尺寸,大電流繞組連接點數(shù),SR驅(qū)動方式,原邊適用拓?fù)涞榷鄠€方面對三種整流方式逐一進(jìn)行比較。比較基于相同條件下進(jìn)行,即變換器功率等級,開關(guān)頻率fs,副邊電壓Vsec的幅值V2,各拓?fù)鋵?yīng)定義的占空比D,輸出電壓VO及其紋波ΔVO要求,輸出濾波電容C相同。

圖5全橋整流—倍流整流演化過程簡圖

圖6電感電流紋波互消作用示意 3.1整流管導(dǎo)通損耗 (1)半波整流拓?fù)鋞ON時段內(nèi),負(fù)載電流IO流過SR1;在tOFF時段內(nèi),IO流過SR2。因此在一個開關(guān)周期Ts中,兩整流管總的導(dǎo)通損耗,相當(dāng)于負(fù)載電流流經(jīng)一個整流管的導(dǎo)通損耗(損耗計算公式用MOSFET)。基本關(guān)系式為: Phw=m·IO2Rds(on)(9) 式中:m為用作SR1或SR2的MOSFET的并聯(lián)個數(shù)(SR1、SR2并聯(lián)個數(shù)一般相等); Rds(on)為MOSFET導(dǎo)通電阻。 (2)中心抽頭全波整流tON時段內(nèi),負(fù)載電流IO流過SR1或SR2;tOFF時段內(nèi),負(fù)載電流在兩個整流管上平分,從而減小了tOFF時段內(nèi)整流管的導(dǎo)通損耗,當(dāng)用肖特基二極管作為整流管時,因肖特基伏安特性為指數(shù)關(guān)系,損耗降低量并不太明顯。當(dāng)采用MOSFET作為同步整流管,其電壓電流近似呈線性關(guān)系,損耗降低得非常明顯,一個周期內(nèi)整流管總的導(dǎo)通損耗近似為:Pfw=m··IO2Rds(on) D<1(10) (3)倍流整流拓?fù)銼R1、SR2中的電流流通情況與全波整流相似。一個周期內(nèi)整流管總的導(dǎo)通損耗近似為:Pcd=m··IO2Rds(on) D<0.5(11) 三種整流方式整流管的導(dǎo)通損耗(基準(zhǔn)值取為m·IO2Rds(on))與D的對應(yīng)關(guān)系示于圖7。由圖7可知,D越小,全波整流和倍流整流拓?fù)渲姓鞴艿膶?dǎo)通損耗與半波整流相比越小。從損耗角度考慮,當(dāng)工作在Dmax(全波整流:Dmax=1;倍流整流:Dmax=0.5)附近時,后兩種整流拓?fù)渑c半波整流相比,并無多大優(yōu)勢。 3.2磁性元件 (1)濾波電感 ①半波整流拓?fù)潆姼猩想妷侯l率與開關(guān)頻率fs相同,滿足規(guī)定紋波要求的電感量[7]為:Lhw=(12) ②中心抽頭全波整流拓?fù)潆姼猩想妷侯l率為 開關(guān)頻率的兩倍,滿足規(guī)定紋波要求的電感量為:Lfw=(13)

圖7三種整流拓?fù)湔鞴軐?dǎo)通損耗的比較 ③倍流整流拓?fù)潆m然獨(dú)立電感L1、L2上電壓 的頻率與開關(guān)頻率fs相等,但由前面分析可知,拓?fù)渲写嬖趦蓚€獨(dú)立電感電流的紋波互消作用,而且兩電感合成電流的頻率為開關(guān)頻率fs的兩倍,在D靠近0.5時,紋波互消作用非常顯著,因而可以大大減小所需濾波電感值。滿足規(guī)定紋波要求的電感量為:L1=L2=··(14)可見,在相同條件下為滿足相同的輸出電壓紋波要求,后兩種整流拓?fù)渌璧臑V波電感值比前者顯著減小,若半波整流輸出濾波電感為參照值L,則采用全波整流只需·L,采用倍流整流只需·L,從而減輕了輸出濾波電容器的紋波設(shè)計壓力,減小了電感尺寸。當(dāng)然這里給出的公式只能作為粗略的對比,并未考慮實際電容器的ESR和ESL的影響。 (2)變壓器 假定輸出濾波電感很大,可以忽略電感電流紋波,有iL=IO,iL1=iL2=IO/2。①半波整流拓?fù)湓赟R1導(dǎo)通的tON時段內(nèi),負(fù)載電流IO流過變壓器副邊繞組,在SR2導(dǎo)通的tOFF時段內(nèi),變壓器副邊繞組電流為零。變壓器副邊電流有效值近似為:ISEC=IO·。②中心抽頭全波整流拓?fù)湓赟R1、SR2分別導(dǎo)通的tON時段內(nèi),負(fù)載電流IO分別流過變壓器副邊中心抽頭繞組中的一只繞組;在SR1、SR2一起導(dǎo)通的tOFF時段內(nèi),負(fù)載電流在兩只整流管上平分,中心抽頭的兩只繞組中,均流過一半的負(fù)載電流(IO/2)。變壓器副邊電流有效值近似為:ISEC=IO·(兩個繞組均等于Isec)。③倍流整流拓?fù)湓赟R1、SR2分別導(dǎo)通的tON時段內(nèi),一半的負(fù)載電流(假定IL1=IL2=IO/2)流過變壓器副邊繞組;在SR1、SR2一起導(dǎo)通的tOFF時段內(nèi),負(fù)載電流通過兩個電感和兩個整流管形成放電回路,并不流過變壓器副邊繞組(變壓器繞組中只會流過很小的磁化電流,可忽略),也即在tOFF時段內(nèi),可以認(rèn)為變壓器副邊繞組電流為零。副邊電流有效值近似為:ISEC=IO·。 圖8給出三種整流方式中變壓器副邊電流有效值(基準(zhǔn)值為IO)與D的對應(yīng)關(guān)系。可見,在D相等時,倍流整流與半波整流拓?fù)渥儔浩鞲边吚@組Irms相當(dāng)。而這兩個拓?fù)渥儔浩鞲边吚@組Irms與全波整流拓?fù)涓边匢rms的大小則與占空比D大小有關(guān):當(dāng)D<0.33時,前者比后者小;D>0.33時,前者比后者大。要注意的是中心抽頭全波整流副邊為兩只繞組,而其它兩種整流方式只有一只繞組。 特別需要指出的是,倍流整流拓?fù)溥@一電路形式特別適合于應(yīng)用磁集成技術(shù)[8]。一般可采用兩種集成思路:兩只電感集成在一只磁芯上,以及兩只電感和變壓器集成在一只磁芯上。在倍流整流拓?fù)渲校m然由電感電流交錯合成后的電流紋波較小,但分別流過分立電感L1、L2上的電流紋波卻較大,因此在采用分立電感元件時,對應(yīng)每只電感的磁通脈動量較大,引起較大的磁芯損耗,影響整機(jī)效率;把電感L1、L2集成在一只磁芯上(如EE或EI型),電感繞組分別繞制在兩只外腿上,對應(yīng)的磁通在中心柱上交疊,可以實現(xiàn)磁通脈動量的互消作用,從而大大減小中心柱的磁芯損耗和磁芯體積。對應(yīng)的示意圖如圖9所示[9]。 更進(jìn)一步,可把三個分立磁性元件集成在一只磁芯上[10],如圖10所示,同時實現(xiàn)了磁芯和繞組的集成,從而大大減小了磁性元件所占的總體積,簡化了布局及封裝設(shè)計,與半波、全波整流相比,具有顯著的優(yōu)越性。 3.3大電流繞組連接點及布局設(shè)計 考慮到幾種整流電路應(yīng)用于大電流輸出場合,因此對大電流繞組數(shù)和繞組連接點數(shù)進(jìn)行了比較。 (1)半波整流拓?fù)溆?只大電流繞組,4個大電流繞組連接點。 (2)全波整流拓?fù)溆?只大電流繞組,5個大電流繞組連接點(假定中心抽頭結(jié)構(gòu)中,副邊兩只繞組的中間連接在繞組內(nèi)部完成)。 (3)倍流整流拓?fù)溆?只大電流繞組,6個大電流連接點;考慮兩電感和變壓器的集成后,只有2只大電流繞組,3個大電流繞組連接點。可見,應(yīng)用磁集成技術(shù)后的倍流整流拓?fù)渑c前兩個整流拓?fù)湎啾龋箅娏骼@組數(shù)、大電流繞組連接點數(shù)都較少,因此副邊的布局大大簡化,與布局相關(guān)的損耗也得以進(jìn)一步降低,使得整機(jī)封裝設(shè)計變得容易。

圖8三種整流拓?fù)渥儔浩鞲边吚@組電流有效值對照圖

圖9兩電感集成 (a)兩電感磁芯集成示意(b)磁通脈動互消作用示意

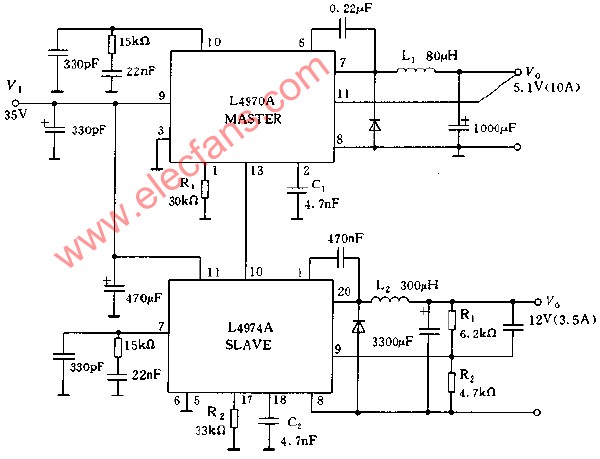

圖10三個分立磁性元件的集成 3.4同步整流管(低壓功率MOSFET)的驅(qū)動方式及原邊拓?fù)涞目紤] (1)同步整流管的驅(qū)動方式 同步整流管的驅(qū)動方式一般可分為兩類: ——外加控制驅(qū)動(ExternalControl):通過附加的邏輯控制和驅(qū)動電路,產(chǎn)生出隨主變壓器副邊電壓作相應(yīng)時序變化的驅(qū)動信號,驅(qū)動同步整流管。這種驅(qū)動方式的驅(qū)動信號電壓幅值恒定,不隨副邊電壓幅值變化,驅(qū)動波形好,但需要一套復(fù)雜的控制驅(qū)動電路,增加了成本,也延長了研發(fā)時間。 ——自驅(qū)動同步整流(Self-drivenSynchronousRectification):即從電路中的某一點,直接獲取電壓驅(qū)動信號,驅(qū)動同步整流管,比較常用的是從主變壓器的繞組上直接獲取驅(qū)動電壓。這種驅(qū)動方案簡單、經(jīng)濟(jì)、可靠,但驅(qū)動波形質(zhì)量不如外加控制驅(qū)動電路理想[11]。 ①半波整流拓?fù)淙鐖D2所示連接,可以直接從變壓器副邊獲取電壓,驅(qū)動SR工作,這在5V及3.3V等標(biāo)準(zhǔn)電壓輸出的DC/DC變換器中,已經(jīng)得到廣泛的應(yīng)用。在輸出電壓更低時,可在主變壓器上加繞輔助繞組,獲得幅值足夠驅(qū)動同步整流管的驅(qū)動電壓。 ②全波整流拓?fù)渑c倍流整流拓?fù)湟驗橹髯儔浩鞲边呺妷捍嬖谳^長的為零時段(tOFF),如果采用直接從變壓器副邊獲取電壓的自驅(qū)動SR方法,在這些tOFF時段,SR1、SR2均關(guān)斷,電感電流將流過SR1、SR2的體二極管,致使整流部分的功耗增大,失去采用同步整流管的優(yōu)勢。相關(guān)文獻(xiàn)[6]提出一種混合驅(qū)動方式,采用對稱半橋倍流整流拓?fù)洌秒娐返募纳?a target="_blank">參數(shù),使得tOFF時段內(nèi)SR1、SR2都能導(dǎo)通,雖然不失為一種思路,但無法保證在所有的負(fù)載范圍內(nèi),對應(yīng)tOFF時段SR1、SR2都能有效開通,而且SR1、SR2的正確開關(guān)工作受變壓器漏感的影響很大,而在變壓器制造中,很難保證漏感的一致性,因此實用價值并不明顯。對于這種副邊電壓存在較大tOFF時段的拓?fù)洌^多的采用外加控制驅(qū)動,保證了開關(guān)時序的準(zhǔn)確性,從而確保了電路工作的可靠性及性能。 (2)原邊拓?fù)涞目紤] ①半波整流拓?fù)湓呁負(fù)漭^多的采用正激電路,因而選擇何種磁復(fù)位方法非常關(guān)鍵,它將決定主變壓器的工作方式[12]。區(qū)別于其它磁復(fù)位方法,采用圖11(a)所示的有源鉗位正激電路可使主變壓器雙向磁化,從而減小主變壓器的體積。 ②全波整流拓?fù)渫ǔEc圖11(b)、(c)、(d)對隔離式低壓/大電流輸出DC/DC變換器中幾種副邊整流電路的比較備注:m:作為同步整流管使用的MOSFET并聯(lián)數(shù)目;Rds(on):MOSFET導(dǎo)通電阻; *:根據(jù)不同的復(fù)位方法,有些拓?fù)淇梢怨ぷ髟贒>0.5,但一般折衷優(yōu)化考慮D<0.5; **:假定所有的副邊繞組均為單匝,括號內(nèi)數(shù)為采用磁集成技術(shù)后的數(shù)量; ***:假定全波整流拓?fù)渲校瑑蓚€副邊繞組的中間連接在繞組內(nèi)部完成,括號內(nèi)的數(shù)為采用磁集成技術(shù)后的數(shù)量;

圖11幾種原邊拓?fù)? (a)有源鉗位(b)對稱半橋(c)推挽(d)全橋 ****:副邊應(yīng)用同步整流的半波整流方式可以與采用不同復(fù)位方法的正激拓?fù)浣Y(jié)合使用,如RCD復(fù)位、諧振式復(fù)位等。

應(yīng)的推挽、對稱半橋、全橋拓?fù)湎嘟Y(jié)合,從而獲得正負(fù)對稱的副邊電壓。 ③倍流整流拓?fù)湮墨I(xiàn)[13]給出正激拓?fù)渑c倍流整流拓?fù)浣Y(jié)合使用的拓?fù)湫问健醇る娐罚@種電路在原邊主管關(guān)斷,輔管處于通態(tài)時,變壓器作為能量源,磁化電流高達(dá)IO/2反映到原邊值(IO代表負(fù)載電流),增加了原邊開關(guān)的電流應(yīng)力和損耗,變壓器設(shè)計也相對復(fù)雜。基于以上考慮,本篇未對這一拓?fù)溥M(jìn)行對比選擇。 在低壓/大電流輸出場合,推挽、對稱半橋、全橋這些對稱的原邊拓?fù)洌容^適合與倍流整流拓?fù)浣Y(jié)合使用。 在這三種拓?fù)渲校葪l件下,全橋原邊功率管的電流應(yīng)力和電壓應(yīng)力最低;半橋拓?fù)湓吂β使艿碾娏鲬?yīng)力是全橋的兩倍,電壓應(yīng)力與全橋相等;推挽拓?fù)湓吂β使艿碾妷簯?yīng)力是全橋的兩倍(推挽常因存在漏感問題,使得實際電壓應(yīng)力高于兩倍輸入電壓),電流應(yīng)力與全橋相等。所以可以推知:今后低壓/大電流輸出DC/DC變換器,對于12V和48V的推薦總線電壓,推挽拓?fù)涓m合于12V總線輸入;而半橋更適合于48V總線輸入;全橋拓?fù)浼嬗泄β使茈娏鲬?yīng)力低和電壓應(yīng)力低的優(yōu)點,但全橋拓?fù)淦骷?shù)量相對較多,因而從器件數(shù)和整體的簡單性這一角度出發(fā),全橋并非最好的選擇。但隨著高頻化的發(fā)展趨勢,為提高變換效率,必然要求實現(xiàn)原邊功率管的軟開關(guān),而全橋移相PWMDC/DC變換器則很容易實現(xiàn)主管ZVS的要求,因此在高頻、低壓/大電流輸出DC/DC變換器中,全橋拓?fù)淙圆皇檩^好的選擇。 以上對三種整流電路進(jìn)行了詳細(xì)的比較,這里把相關(guān)內(nèi)容作一小結(jié),如表1所列。 4結(jié)語 本文針對隔離式低壓/大電流輸出DC/DC變換器的應(yīng)用場合,對副邊半波整流、全波整流、倍流整流三種整流方式進(jìn)行了詳盡的分析比較,指出各自的優(yōu)缺點和應(yīng)用指導(dǎo),并得出結(jié)論:結(jié)合磁集成技術(shù)和同步整流技術(shù)的倍流整流拓?fù)洌貏e適用于隔離式低

|

電子發(fā)燒友App

電子發(fā)燒友App

q

q

評論