|

基于柔性鎖相環路的動態電壓恢復器控制方案的研究?? 摘要:動態電壓恢復器(DVR)是一種新型電能質量調節裝置,它能有效抑制電網電壓波動對敏感負載的影響。介紹了應用于DVR的一種新型的鎖相技術—柔性鎖相環路〔soft phase locked loop(SPLL)〕和以此為基礎的控制方案。 關鍵詞:動態電壓恢復器;鎖相技術;電壓跌落 1??? 概述 ??? 動態電壓恢復器(dynamic voltage restorers簡稱DVR)是一種保證電網供電質量的新型電力電子設備,主要用于補償供電電網產生的電壓跌落,閃變和諧波等。它的基本結構和在電網中的接入方式如圖1所示。DVR本身相當于一個受控電壓源[1],它可在電源和敏感負載之間插入一個任意幅值和相位的電壓。當電源電壓畸變時,通過改變DVR的電壓,達到穩定敏感負載電壓的目的。

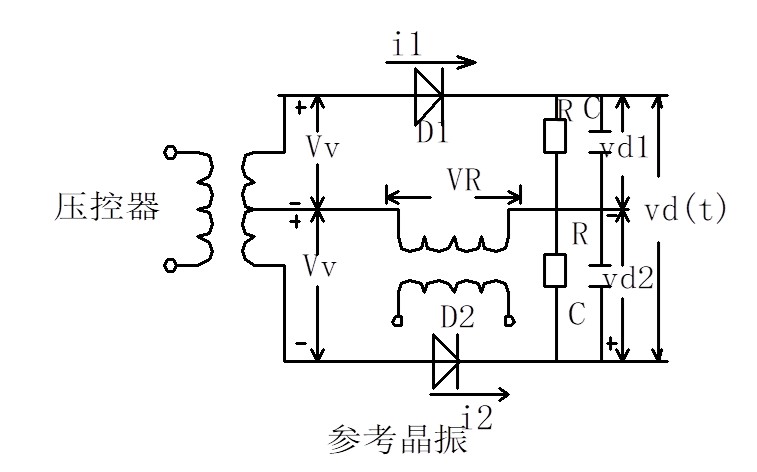

圖1??? 動態電壓恢復器的結構和連接圖 ??? DVR的主要補償對象是電網電壓的跌落,閃變和諧波,因此,要求其控制系統應具有足夠的響應速度,同時,對畸變的輸入電壓應具有很強的抑制作用。本文提出的基于瞬時無功理論[3]的柔性鎖相環路(SPLL)[4]和以此為基礎的控制方案能夠很好地達到這一要求。 2??? 柔性鎖相環路 ??? 為實現以DVR補償電源側畸變電壓的目的,則獲得電源側電壓的相位是首要的任務。獲得相位信息的方法有過零比較,最小二乘法,小波分析等多種方法。過零比較結構簡單,實現較為容易,但動態響應速度慢,對畸變電壓的抑制較差;最小二乘法動態響應速度快,能準確地鎖定正序電壓的相位,但輸入電壓存在諧波時性能較差;小波分析性能較好,但結構復雜,實現起來較為困難。 ??? 本文介紹的SPLL結構比較簡單,動態響應速度快,對畸變輸入電壓有很強的抑制作用。 ??? SPLL的基本結構如圖2所示。把三相輸入電壓采樣后做32變換,即把電壓轉換到αβ坐標系中。再經pq變換得到uq,變換所使用的角度是鎖相的輸出θ*,uq的值代表輸入電壓a相相位和鎖相輸出相位θ*的差,然后利用一個PI環節將該差調整到零,從而達到相位捕獲的目的。下面對原理做詳細闡述。

圖2??? SPLL的控制流程圖 ??? 如果輸入三相電源電壓中僅含三相基波正序,則設輸入三相電壓為 ??? ua= ??? ub= ??? uc= 式中:ω1為角頻率; ??????????? φ為相位。 ??? 經過C32變換由三相變至兩相,有 ??? ??? 如果,此時鎖相環輸出的角頻率為ω,相位為0,則利用鎖相環輸出的角度進行pq變換,有 ??? ??? 頻率沒有鎖定時,uq是一個交流分量,在頻率鎖定,相位沒有鎖定時,它是一個直流分量,其大小代表鎖相輸入與輸出之間的相位差信息。在頻率,相位完全捕獲的情況下,有ω1=ω,φ=0,此時uq=0,它是恒定的直流分量,而且它并不隨電源電壓幅值的變化而變化。可以看出,只有頻率和相位完全捕獲的情況下才有uq=0,所以通過把uq調節為0,就可以達到鎖相的目的,該結構利用PI環節達到這一目的。同時,因在數字系統中正弦和余弦的值靠查表得到,所以θ*的值不能太大,故每隔一個工頻周期復位一次。 ??? 假設三相輸入電源電壓畸變即電壓中含有零序、負序和諧波分量。對于零序,做C32變換后其值為0,對結果沒有影響,所以不予考慮。此時的三相電壓為 ??? ua= ??? ub= ??? uc= 式中:下標為1的表示正序,下標為2的表示負序; ????? n表示諧波次數(當n等于1時表示基波); ????? U表示電壓有效值; ??????????? φ表示初相角; ??????????? ω為電網電壓角頻率。 ??? 從而可以得到 ??? uq= 由式(5)可以看出,僅有基波正序轉換為直流分量,其他分量經過轉換都是頻率較高的分量。經過濾波,將這些高頻分量濾除,則SPLL的輸出就不受負序、零序和諧波的影響。這就保證了在畸變輸入電壓的情況下,SPLL能夠正確地鎖定輸入電壓的基波正序。關于濾波,因系統中存在兩個積分環節,對高頻分量有較強的抑制作用,所以,一般不需要額外的濾波環節。但是當在三相輸入電壓嚴重不平衡時,負序分量很大,若要將其完全濾除,所需時間較長,從而影響系統的動態響應時間。為此,可在pq后加入一個濾波環節來加速負序分量的濾除,如圖3所示,從而在保證濾除負序分量的情況下,系統有較短的動態響應時間。

圖3??? 改進的SPLL結構框圖 3??? 以SPLL為基礎的控制方案 ??? 由式(3)可知,uq代表輸入電壓的相位信息,up代表輸入電壓的幅值信息。在相位鎖定的情況下,前者為零,后者是一僅和幅值有關的直流分量。利用uq構建SPLL達到鎖相的目的,而利用up可將理想負載電壓轉換為一常數和實際輸入的電源側電壓經轉換后相減,得到有功分量上需要補償的值,再經反變換即可得到最終的指令。其控制框圖如圖4所示。

圖4??? 利用瞬時無功獲得指令 ??? 圖4中的上半部分是SPLL,它保證準確的鎖定電源側畸變輸入電壓的基波正序相位;下半部分是為保持負載電壓有恒定的幅值。這種方案對電壓的幅值和相位分開考慮,物理意義比較明顯。而且,若目標補償電壓的幅值改變,僅須對目標輸入up*進行修改,所以比較靈活。如果使用空間矢量PWM調制(SVPWM)就不須對指令進行反變換,從而節省大量資源,該方案就更為適用。 ??? 使用這種控制方案,得到DVR的補償指令,通過三角波比較等跟蹤方式控制逆變器的工作,即可達到補償畸變電壓的目的。其流程如圖5所示。

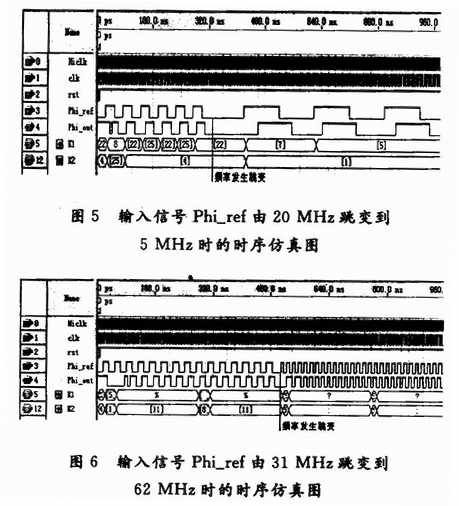

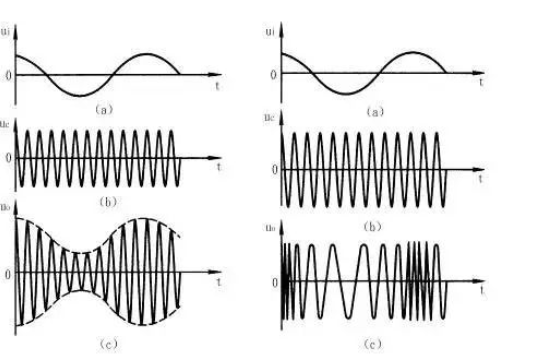

圖5??? DVR工作流程圖 4??? 試驗結果 ??? 以一臺三相四線制6kW的DVR為平臺,對該控制方案進行試驗驗證。控制方案的實現采用TI公司的DSP2000系列的C32。利用此裝置進行電壓跌落下的鎖相和補償試驗。 ??? 圖6是三相輸入電壓中a相電壓和鎖相輸出的電壓波形,可以看出,該鎖相方式具有很快的響應速度,很好的精度,并且對畸變電壓有很強的抑制作用。

圖6??? a相輸入電壓和SPLL輸出 ??? 圖7是采用本文所提出的控制方案時,補償電壓跌落的試驗結果。可以看出,此時負載電壓和網側電壓同相位,網側的電壓跌落和諧波得到了很好的補償。

圖7??? 網側電壓和補償后的負載電壓 5??? 結語 ??? 本文提出了一種以瞬時無功理論為基礎的鎖相方式——SPLL和以此為基礎的控制方案,由理論分析和試驗驗證可以看出SPLL的動態響應速度快,同時,對畸變輸入電壓有很強的抑制作用,而控制方案具有物理意義明顯,動態響應速度快,控制靈活簡便和補償效果好等優點。該方案對DVR控制方案的研制提供了一種新的選擇。 |

基于柔性鎖相環路的動態電壓恢復器控制方案的研究

- 恢復器(5112)

相關推薦

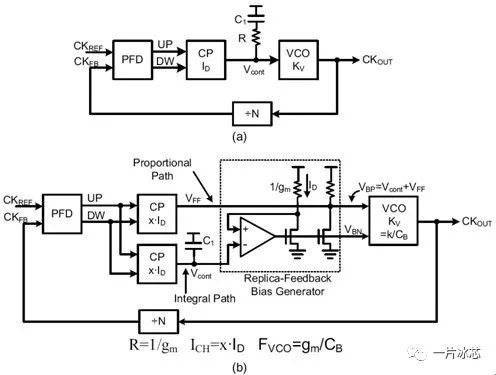

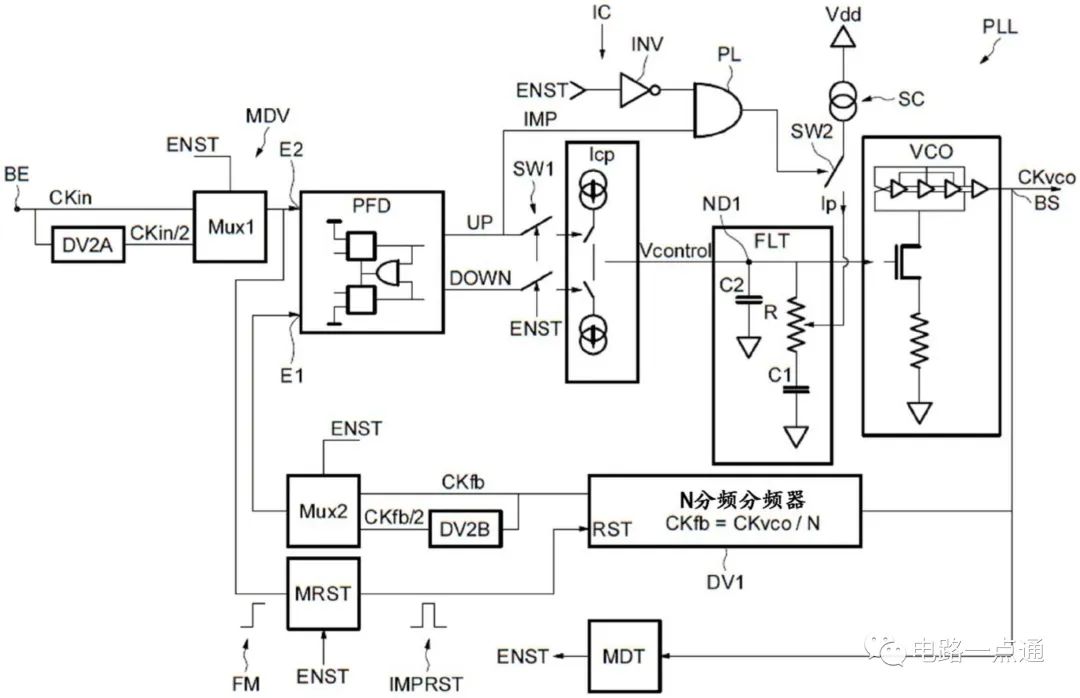

基于DSP Builder系統模型的數字鎖相環設計

本文采用一種基于比例積分(PI)控制算法的環路濾波器應用于帶寬自適應的全數字鎖相環,建立了該鎖相環的數學模型

2010-10-14 10:03:25 1270

1270

1270

1270

鎖相環鎖定時間取決于哪些因素

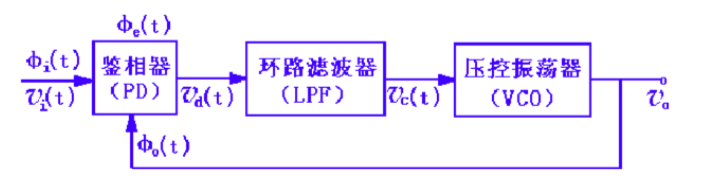

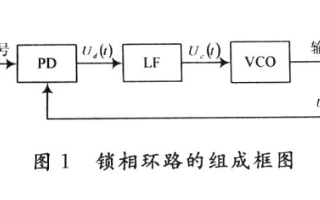

鎖相環路是由鑒相器《簡稱PD》、還路濾波器〔(簡稱LPF或LE和壓控振蕩器(簡稱VCO〕三個部件組成閉合系統。這是一個基本環路,其各種形式均由它變化而來。

2024-01-31 15:54:51 596

596

596

596

鎖相技術教程下載

;/strong><br/><strong>第1章&nbsp; 鎖相環路的基本工作原理</strong>

2009-10-08 15:37:53

鎖相環控制頻率的原理

保證環路所要求的性能, 增加系統的穩定性。壓控振蕩器受濾波器輸出的電壓控制, 使得壓控振蕩器的頻率向輸入信號的頻率靠攏, 也就是使差拍頻率越來越低, 直至消除頻率差而鎖定。鎖相環在開始工作時, 通常輸入

2022-06-22 19:16:46

鎖相環在電力系統中的應用

、軟件鎖相環原理軟件鎖相環采用瞬時無功理論鎖相原,其基本結構如下圖所示。三相電壓usa,u***,usc經坐標變換后得到usd,usq,這里的坐標變換相當于硬件鎖相環中的鑒相器,PI調節器相當于環路濾波器

2015-01-04 22:57:15

鎖相環的原理,特性與分析

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

鎖相環的原理,特性與分析所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL 表示。

2008-08-15 13:18:46

鎖相環知識

、壓控振蕩器(VCO) 四、環路濾波器(LPF) 五、固有頻率ωn和阻尼系數x 的物 理意義 六、同步帶和捕捉帶 ?第二部分:鎖相環實驗 ?實驗一、PLL參數測試 ?一、壓控靈敏度KO的測量 ?二

2011-12-21 17:35:00

鎖相環環路濾波器電路問題

如圖所示,該鎖相環電路VCOin的電壓波形如右圖所示,我需要得到的是該穩定的電壓,如果把C18由0.1uf改成10uF,鎖相環又不鎖相了,輸出電壓一直為5V。需要如何選擇濾波電容的參數來將該電壓進行濾波。

2016-09-11 22:23:46

鎖相環路是什么?有何特點

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號

2022-01-11 06:34:28

AD9957鎖相環一直失鎖

如題,AD9957的鎖相環一直失鎖,不用鎖相環輸出點頻信號時正常的,用了鎖相環后,PLL_LOCK信號一直為低,sync_clk輸出信號也不是穩定的周期信號,環路濾波器的值有點誤差,因為現有的器件沒有那么精確的電容電阻值,問下鎖相環的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

SFS11000Y-LF鎖相環

`SFS系列是一個固定頻率PLL解決方案,集成了鑒相器,環路濾波器,VCO和PIC控制器。它消除了對任何外部編程的需求,從而將設計復雜性降至最低。它是需要500 MHz至15 GHz范圍內的單個頻率

2021-04-03 17:05:46

一種基于ADF4106的鎖相環頻率合成器應用實例介紹

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。 關鍵詞:ADF4106,鎖相環,頻率合成器,環路濾波器

2019-07-04 07:01:10

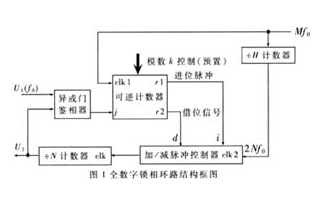

全數字鎖相環的設計及分析

Phase-Locked Loop)逐步發展起來。所謂全數字鎖相環,就是環路部件全部數字化,采用數字鑒相器、數字環路濾波器、數控振蕩器構成鎖相環路,并且系統中的信號全是數字信號。與傳統的模擬電路實現的鎖相環

2010-03-16 10:56:10

關于鎖相環的組成你了解多少?

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)。許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。鎖相環通常由鑒相器(PD)、環路濾波器(LF

2019-03-17 06:00:00

基于鎖相環的可變量程轉速控制系統

在電機轉速控制系統中,經常需要對電機的轉速信號進行測量和處理,以達到精確控制轉速的目的。通常采用旋轉編碼器、測速發電機等傳感器測量轉速,不但體積大、安裝不便,而且價格高;而利用鎖相環路可用很低的成本

2011-07-13 17:08:51

基于雙dq坐標系的自解耦三相鎖相環算法

0引言鎖相環廣泛應用于如電能質量分析、電力系統保護、并網變換器以及無功補償等現代工業控制領域。已有研究人員對單dq坐標系三相鎖相環算法進行了分析,通過對電壓矢量的坐標變換及PI控制,實現理想電壓工況

2021-09-06 09:24:01

如何配置鎖相環并為總線提供時鐘呢

由于一般的晶振受限于工藝與成本,做不到很高的頻率,可在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路來實現穩定且高頻的時脈沖訊號。本例通過MC9S12XS128這款

2021-12-10 06:26:47

高頻鎖相環路LMX2430電子資料

概述:LMX2430是一款高頻鎖相環路芯片,它可在2.25V至2.75V的電壓范圍內操作。這三款芯片的其他功能包括可隨意選擇的同步或異步停機模式、1mA或4mA的可編程電荷泵電流、內置超時計數器的快速鎖定技術、...

2021-04-08 07:24:00

高頻鎖相環路LMX2433相關資料分享

LMX2433是一款高頻鎖相環路芯片,它可在2.25V至2.75V的電壓范圍內操作。這三款芯片的其他功能包括可隨意選擇的同步或異步停機模式、1mA或4mA的可編程電荷泵電流、內置超時計數器的快速鎖定

2021-04-13 07:27:00

pll鎖相環

所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱

2008-08-15 12:41:05 332

332

332

332模擬鎖相環應用實驗

一、實驗目的1、掌握模擬鎖相環的組成及工作原理。2、學習用集成鎖相環構成鎖相解調電路。3、學習用集成鎖相環構成鎖相倍頻電路。

二、鎖相環路的基本原理

2009-03-22 11:44:37 126

126

126

126用鎖相環路實現任意頻率變換技術

介紹了鎖相環路的工作原理以及MM74HC4046AN鎖相環芯片的引腳功能。給出了利用鎖相環進行頻率變換的方案和用方波信號進行頻率變換的實際電路,并對環路和相位進行了分析。

2009-04-27 15:42:23 50

50

50

50集成鎖相環路解碼器LM567及其在檢測電路中的應用

美國國家半導體公司生產的集成鎖相環路解碼器LM567以其優良的性能和低廉的價格而在各種解碼電路中獲得了廣泛的應用.本文詳細介紹了LM567的內部結構、工作原理、性能指標和選擇

2009-04-30 15:22:57 156

156

156

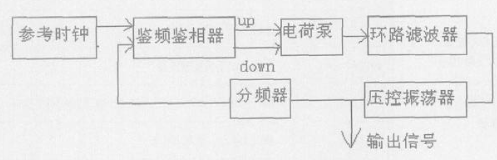

156基于時鐘恢復系統中的鎖相環電路的設計

本文主要設計了基于相位控制技術的時鐘恢復系統的PLL 鎖相環路。分別對各單元電路結構——鑒頻鑒相器、電荷泵、環路濾波器、壓控振蕩器、分頻器進行設計。采用2.5V,0.25μm

2009-06-01 15:51:53 54

54

54

54智能全數字鎖相環的設計

智能全數字鎖相環的設計:在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智能配

2009-06-25 23:32:57 72

72

72

72鎖相環的應用

在載波調制信號的相干解調中,必須提取相干載波,如何從接收信號中提取相干載波,一般方法是采用鎖相環路。它能從淹埋在噪聲中的微弱信號中提取出相干載波,從而大大提高接

2009-08-03 10:09:06 4

4

4

4鎖相環頻率合成器(Motorola集成電路應用技術叢書)

鎖相環頻率合成器(Motorola集成電路應用技術叢書):鎖相環路設計基礎,鑒相器,壓控振蕩器,程序分頻器,前置分頻器,單片集成鎖相環路等內容。

2009-09-05 08:20:52 0

0

0

0基于虛擬磁鏈和鎖相環的無電網電壓傳感器并網逆變器的研究

基于虛擬磁鏈和鎖相環的無電網電壓傳感器并網逆變器的研究:為了提高并網逆變器的可靠性和抗電網電壓波動,同時進一步降低并網逆變器的成本,提出了一種基于鎖相環和虛

2010-02-18 13:16:58 42

42

42

42鎖相環動態頻相跟蹤特性分析

在分析鎖相環工作原理的基礎上,利用傳遞函數法建立了鎖相環跟蹤誤差的二階等效模型,并對鎖相環的動態頻相跟蹤特性進行了理論分析.利用MATLAB構建了鎖相環的仿真

2010-03-01 18:14:11 32

32

32

32鎖相環原理

鎖相環原理

鎖相環路是一種反饋電路,鎖相環的英文全稱是Phase-Locked Loop,簡稱PLL。其作用是使得電路上的時鐘和某一外部時鐘的相位同步。因鎖相環可以

2007-08-21 14:46:04 4879

4879

4879

4879鎖相環路跟蹤特性的測量方法

鎖相環路跟蹤特性的測量方法:鎖相環路的跟蹤特性是可以測量的。以CMOS集成鎖相環路5G4046構成的跟蹤濾波器如圖6-2(a)。在電源電壓為10V,中心頻率fo=1

2008-04-21 11:53:40 1225

1225

1225

1225

鎖相環的研究和頻率合成

鎖相環的研究和頻率合成一、實驗目的:1. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環基本特性的研究3. 利用鎖相環實現頻率合成二、鎖相環原理:

2009-03-06 20:02:52 1939

1939

1939

1939

基于ADF4106的鎖相環頻率合成器

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。???

2009-05-05 19:57:57 2585

2585

2585

2585

智能全數字鎖相環的設計

摘要: 在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智

2009-06-20 12:39:32 1408

1408

1408

1408

模擬鎖相環,模擬鎖相環原理解析

模擬鎖相環,模擬鎖相環原理解析

背景知識:

鎖相技術是一種相位負反饋控制技術,它利用環路的反饋原理來產生新的頻率點。它的主要

2010-03-23 15:08:20 5780

5780

5780

5780CMOS高速鎖相環設計

本文涉及的鎖相環路是基于相位控制的時鐘恢復系統。目的是用鎖相環電路-PLL和DLL實現USB2.0收發器宏單遠UTM的時鐘恢復木塊。其中PLL環路構成的時鐘發生器獎外部晶振的12MHZ的正弦信號

2011-03-03 14:58:34 50

50

50

50集成鎖相環芯片應用 PPT培訓資料

集成鎖相環芯片類型較多,現介紹CC4046(或CD4046)和J691以及NE564(工作頻率可達 50MHz)集成鎖相環。 一、CC4046集成鎖相環芯片 CC4046和J691均為CMOS單片鎖相環路,工作頻率1MHz,其邏輯結構和

2011-03-15 10:05:11 263

263

263

263FPGA在鎖相頻率合成中的應用

鎖相環路由于具有高穩定性、優越的跟蹤性能及良好的抗干擾性,在頻率合成中得到了廣泛應用。但簡單的鎖相環路對輸出頻率、頻率分辨率等指標往往不能滿足要求,所以要對簡單鎖相環

2011-05-28 13:42:13 943

943

943

943

擴頻通信的數字鎖相環設計

針對擴頻通信系統的載波同步,提出一套完善的數字鎖相環設計方案. 該方案利用新穎的可控根法完成1~3階模擬鎖相環(APLL)環路參數設計,并實現從模擬域到數字域的轉換,得到的數字鎖相

2011-08-26 16:10:38 122

122

122

122基于PSpice的動態電壓恢復器研究

隨著現代電力電子設備的廣泛應用, 電壓跌落已日益成為電力部門和用戶關注的電能質量問題。介紹了減少電壓跌落的幾種方法,分析了采用動態電壓恢復器(Dynamic Voltage Restorer)的優

2011-11-03 10:46:35 24

24

24

24鎖相環在不同領域中的應用匯總

由于鎖相環路有上述種種優良的特性,再加上集成鎖相環的出現,使鎖相環路在電子技術等各個領域獲得了廣泛的應用,下面對鎖相環在不同領域中的應用情況作一簡單的概述。 1 在通

2012-09-21 10:09:10 3819

3819

3819

3819pLL射頻鎖相環基礎知識詳解

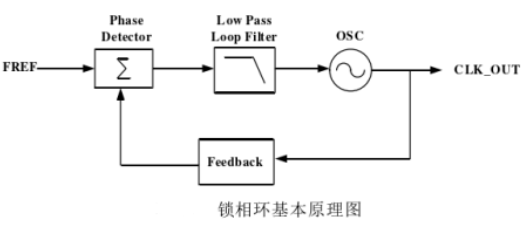

鎖相環路為什幺能夠進入相位跟蹤,實現輸出與輸入信號的同步呢?因為它是一個相位的負反饋控制系統。這個負反饋控制系統是由鑒相器(PD)、環路濾波器(LF)和電壓控制振蕩器(VCO)三個基本部件組成的,基本構成如圖:

2017-04-25 12:03:00 0

0

0

0PLL鎖相環的特性、應用與其基本工作過程

PLL(Phase Locked Loop),也稱為鎖相環路(PLL)或鎖相環,它能使受控振蕩器的頻率和相位均與輸入參考信號保持同步,稱為相位鎖定,簡稱鎖相。

2017-05-22 10:11:40 8672

8672

8672

8672

鎖相環是什么?鎖相環原理及鎖相環在調制和解調電路中的應用

鎖相環就是鎖定相位的環路,它一種典型的反饋控制電路,利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位,實現輸出信號頻率對輸入信號頻率的自動跟蹤,一般用于閉環跟蹤電路。

2017-07-24 15:07:12 27903

27903

27903

27903

基于LMX2315的讀寫器鎖相環應用

鎖相環路在通信系統中得到了廣泛的應用。本文針對超高頻RFID讀寫器的工作特點,設計了基于數字頻率合成器LMX2315的鎖相環路,給出了鎖相環偽隨機跳頻程序流程圖。

2017-09-07 18:54:00 18

18

18

18基于DSP電網動態電壓恢復器模擬系統裝置

本文旨在通過設計一款分布式電網動態電壓恢復器模擬系統裝置,解決電力設備運行過程中電壓暫降或中斷情況下的動態電能安全問題,.裝置采用直流一交流及交一直一交雙重結構,控制系統采用TMS320F28335

2017-11-10 17:26:56 6

6

6

6鎖相環捕捉過程的定性分析

鎖相環捕捉過程的定性分析 若環路原本是失鎖的,但環路能夠通過自身的調節由失鎖進入鎖定的過程稱為捕捉過程。一般情況下,捕捉帶不等于同步帶,且前者小于后者,鎖相環路的捕捉過程屬于非線性過程,在工程上廣泛

2017-11-16 15:37:35 4

4

4

4基于DSP的逆變電源鎖相環的設計與研究

采用基于DSP的數字鎖相環(DPLL )對高頻逆變電源輸出頻率的實時控制,可實現逆變器工作頻率對負載諧振頻率的同步跟蹤 ,確保逆變器開關器件工作在零電壓電流軟開關( ZV ZCS)狀態 ,顯著減小

2017-12-11 13:57:33 14

14

14

14鎖相環在調制和解調中的應用及概念解析

許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2018-01-22 11:18:45 13404

13404

13404

13404

中壓動態電壓恢復器的虛擬阻抗控制策略

中壓動態電壓恢復器(dynamic voltage restorer,DVR)可用于有效保護大范圍的用戶不受電壓暫降的影響,但不能補償其下游饋線上發生故障時的電壓擾動。提出了將DVR控制為虛擬阻抗

2018-02-02 09:53:23 18

18

18

18正點原子開拓者FPGA視頻:PLL鎖相環實驗

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。

2019-09-20 07:05:00 3503

3503

3503

3503

采用Spartan2系列FPGA器件實現全數字鎖相環路的設計和仿真驗證

技術的發展,不僅能夠制成頻率較高的單片集成鎖相環路,而且可以把整個系統集成到一個芯片上去,實現所謂片上系統SOC(System on a chip)。因此,可以把全數字鎖相環路作為一個功能模塊嵌入SOC,構成片內鎖相環。下面介紹采用VHDL技術設計DPLL的一種方案。

2020-07-23 16:23:25 1087

1087

1087

1087

采用二階無源環路濾波器實現三階電荷泵鎖相環的設計

,為了減小壓控振蕩器控制電壓的紋波,它采用了二階無源環路濾波器,這樣就構成了三階電荷泵鎖相環。系統級設計與仿真驗證是鎖相環設計的第一步和關鍵的一步。本文對一種用作時鐘倍頻器的三階電荷泵鎖相環進行了系統級設計與仿真驗證,仿真環境采用SIMULINK。

2020-07-24 09:59:51 2564

2564

2564

2564

鎖相環路的組成、的基本特性和應用分析

鎖相環路(Phase Lock Loop,PLL)是一種自動相位控制(APC)系統,是現代電子系統中應用廣泛的一個基本部件。它的基本作用是在環路中產生一個振蕩信號(有時也稱本地振蕩),這個信號的頻率

2020-08-05 14:15:24 5088

5088

5088

5088

使用FPGA實現數字鎖相環的設計資料說明

鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環通常

2020-08-06 17:58:25 24

24

24

24鎖相環路的典型應用實例詳細說明

基本鎖相環路是由鑒相器、低通濾波器以及壓控振蕩器構成的相位負反饋系統,具有一個頻率輸入端口,一個電壓輸出端口以及一個頻率輸出端口,通常,模擬模擬鎖相環的鑒相器由模擬乘法器承擔,壓控振蕩器由弛張振蕩器承擔。

2020-12-04 08:00:00 3

3

3

3基于鎖相環路實現CPFSK中頻調制器的設計方案

,具有廣泛的應用價值。本文介紹在我國磁懸浮列車車地通信系統中應用的一種CPFSK中頻調制器,其核心是基于鎖相環路的CPFSK信號調制技術。系統要求中頻頻率為280 MHz,在信道帶寬25 MHz以內

2021-04-05 09:22:00 2491

2491

2491

2491

鎖相環(PLL)的工作原理及應用

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2022-03-29 09:54:55 11472

11472

11472

11472鎖相環是如何實現倍頻的?

鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 1594

1594

1594

1594如何用鎖相環恢復載波同步信號?

如何用鎖相環恢復載波同步信號? 鎖相環(PLL)是一種電路,可用于恢復和跟蹤輸入信號的頻率和相位。PLL常用于電信、通訊和控制系統中,以恢復和跟蹤載波同步信號。本文將介紹鎖相環如何恢復載波同步信號

2023-10-30 10:56:38 356

356

356

356基于柔性鎖相環路的動態電壓恢復器控制方案的研究

簡介:動態電壓恢復器(DVR)是一種新型電能質量調節裝置,它能有效抑制電網電壓波動對敏感負載的影響。介紹了應用于DVR的一種新型的鎖相技術—柔性鎖相環路〔softphase locked loop(SPLL)〕和以此為基礎的控制方案。

2023-11-09 08:31:40 0

0

0

0鎖相環路的工作原理

簡介:鎖相環路的工作原理

§1-2 鎖相環路的工作原理

鎖相環路實質上是一個相差自動調節系統。為了掌握環境的工作原理,理解環 路工作過程中發生的物理現象,必須導出環路的相位

2023-11-09 15:16:24 0

0

0

0環路的跟蹤狀態和鎖定狀態的區別?鎖相環路的鎖定狀態應滿足什么條件?

環路的跟蹤狀態是指鎖相環鎖定后的狀態,即環路中的壓控振蕩器(VCO)的輸出信號的相位能夠自動跟蹤輸入信號的相位,從而保持恒定的穩態相位差。

2024-01-30 14:18:32 196

196

196

196為什么說鎖相環相當于一個窄帶跟蹤濾波器

鎖相環路與自動頻率控制電路有何區別?為什么說鎖相環相當于一個窄帶跟蹤濾波器 鎖相環路(PLL)和自動頻率控制電路(AFC)是常見的頻率調節電路,它們的主要區別在于功能和應用場景。 首先,我們來探討

2024-01-31 15:24:57 180

180

180

180鎖相環路鎖定狀態的條件及類型

基本鎖相環通常由鎖相檢測器(Phase Detector)、低通濾波器(Loop Filter)和令牌圈振蕩器(VCO)組成。它是最簡單的鎖相環形式,用于頻率和相位同步。

2024-01-31 16:00:55 217

217

217

217

電子發燒友App

電子發燒友App

評論