●使用大小合適的輸入濾波電容供應(yīng)或過濾高頻交流電源,以便盡可能降低電源干線上的電流。

●將輸入交流電流回路中的寄生電感和 ESL 降至最低。這可以通過在開關(guān)頻率較高的一側(cè)操作實(shí)現(xiàn),這樣就可以使用低 ESL 的陶瓷電容器,從而縮小回路半徑。需要再次強(qiáng)調(diào)的是開關(guān)頻率越高,開關(guān)損耗也越高。

●讓輸入濾波電容的 PCB 引線盡可能短且寬以降低引線電感。

●使用屏蔽式電感器以降低磁漏。

PowerSoC作為降噪策略

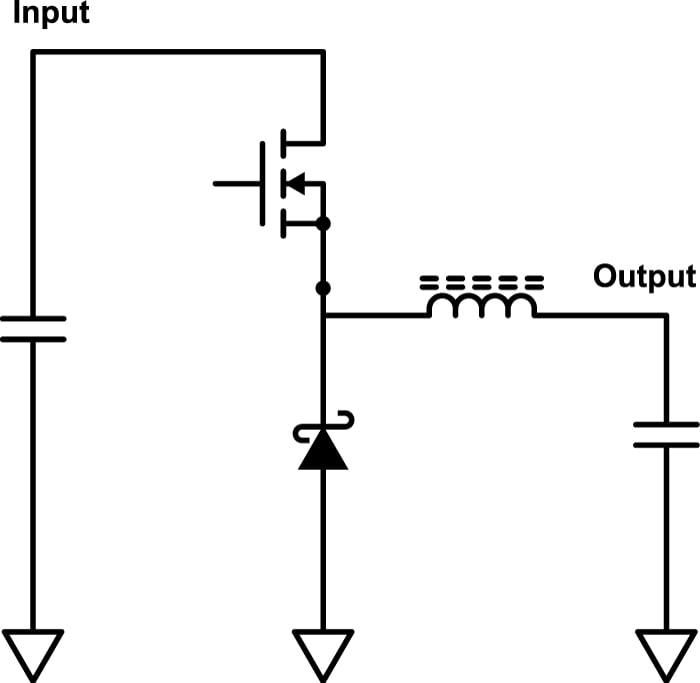

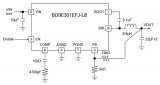

Enpirion于2004年推出全球第一個PowerSoC .PowerSoC在單個IC套件中集成了完整的直流 - 直流轉(zhuǎn)換器,包括控制器、柵極驅(qū)動器、MOSFET開關(guān)、高頻去耦,以及最重要的電感器。大多數(shù) PowerSoC 只需要輸入和輸出濾波電容,因此整個解決方案既簡單又輕巧。

●使用專用的深亞微米高頻 LDMOS 既可實(shí)現(xiàn)低開關(guān)損耗,又能集成整套的控制、驅(qū)動和開關(guān)元件。低開關(guān)損耗可以實(shí)現(xiàn)高開關(guān)頻率,例如 5MHz.

●高密度、高磁導(dǎo)率、小體積的磁性元件可以實(shí)現(xiàn)最低的交流損耗和低直流電阻。小體積的磁性元件和磁結(jié)構(gòu)具有自屏蔽特性,可以降低磁漏。高開關(guān)頻率則允許使用尺寸非常小的電感器。

●高開關(guān)頻率還允許使用小型的輸入和輸出濾波電容,這樣一來,可以縮小輸入和輸出交流回路的尺寸,從而降低紋波和 EMI.

●套件布線經(jīng)過設(shè)計可進(jìn)一步縮小輸入和輸出交流濾波回路的半徑,從而盡可能降低輻射性和傳導(dǎo)性 EMI 以及紋波。

●套件設(shè)計包括射頻技術(shù),旨在盡可能降低內(nèi)部電路元件內(nèi)的寄生阻抗以保持套件內(nèi)的高頻交流電源。

PowerSoC結(jié)果與離散實(shí)現(xiàn)方案

圖3–6展示了 PowerSoC 與離散式直流 - 直流轉(zhuǎn)換器實(shí)現(xiàn)方案的對比結(jié)果。

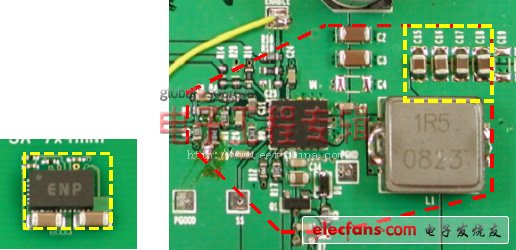

?

圖3:典型4A大小的轉(zhuǎn)換器解決方案區(qū)域?qū)Ρ取owerSoC(左圖)的輸入和輸出交流電流回路非常小,相當(dāng)于典型離散式實(shí)現(xiàn)方案尺寸的1/7.

黃色虛線方框表示PowerSoC尺寸和離散式直流-直流轉(zhuǎn)換器的對比結(jié)果。

?

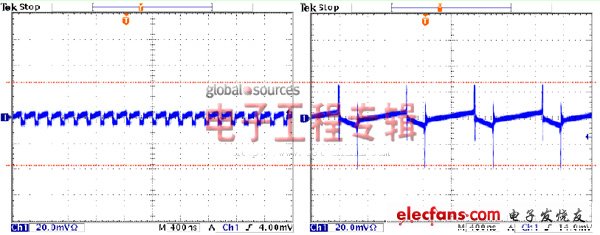

圖4:PowerSoC(左圖)與離散式直流-直流轉(zhuǎn)換器實(shí)現(xiàn)方案(右圖)的輸出紋波電壓對比。二者使用相同的設(shè)備和技術(shù)在供應(yīng)商評估板上測量紋波。測量帶寬為500MHz.

?

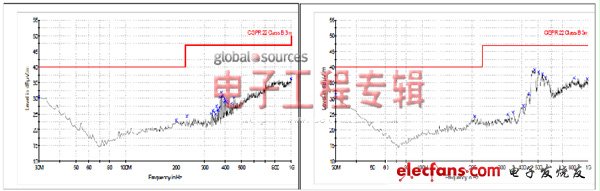

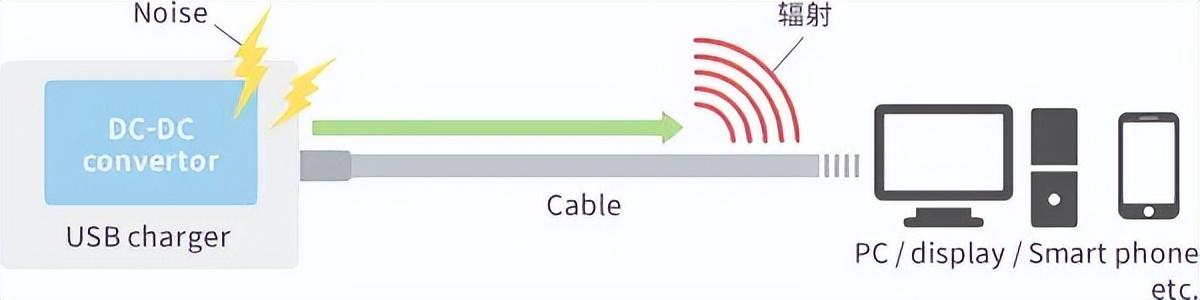

圖5:輻射性EMI測量結(jié)果;CISPR22 B等級3m.左圖為PowerSoC,右圖為離散式實(shí)現(xiàn)方案,均在供應(yīng)商評估板上測量得出。

?

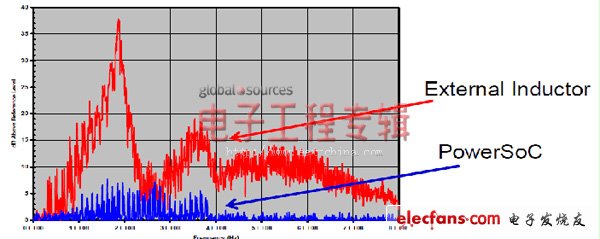

圖6:輸入接地端子上測量的傳導(dǎo)性干擾

采用Enpirion PowerSoC的供電Rocket IO應(yīng)用實(shí)例

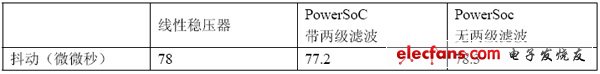

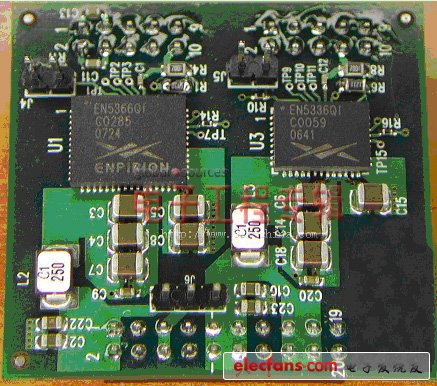

設(shè)計制造的子板插到Virtex 5開發(fā)板上(圖7)。對采用Enpirion裝置驅(qū)動的開發(fā)板和線性穩(wěn)壓器執(zhí)行同樣的抖動測量。分別測量Enpirion PowerSoC有兩級濾波和無兩級濾波的效果。抖動測量結(jié)果如表1所示。

表1. Rocket IO的抖動測量結(jié)果

?

?

圖7:帶Enpirion PowerSoC的子板

結(jié)論

對FPGA設(shè)計師而言PowerSoC代表強(qiáng)效的新型工具。這種裝置能夠有效減少從基于線性穩(wěn)壓器的電壓轉(zhuǎn)換器向更高效的開關(guān)模式轉(zhuǎn)換器轉(zhuǎn)變過程中面臨的諸多問題。 PowerSoC具有和線性穩(wěn)壓器相似的覆蓋區(qū)域,易于設(shè)計,同時也擁有開關(guān)模式轉(zhuǎn)換器的高效率,卻可免去離散式轉(zhuǎn)換器實(shí)現(xiàn)方案的噪聲和復(fù)雜度。

電子發(fā)燒友App

電子發(fā)燒友App

評論