在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。那么模塊的紋波噪聲該如何降低?下文為大家從紋波噪聲的波形、測試方式、模塊設計及應用的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。

2018-08-08 14:53:36 8244

8244

`+6V直流穩壓電源及集成運放電路`

2013-08-14 21:49:30

輸出功率大,放大倍數相應調大才能滿足靈敏度的要求,放大倍數增大直接影響音頻功放的輸出底噪聲。如何降低這兩類音頻功放的輸出底噪聲,針對客戶在應用中的問題,總結以下方法可供參考:1. 分地 電路板上所有

2020-04-30 09:38:53

這11個經典運放電路,電源工程師不能不看!

2021-03-09 07:14:48

輸入端視為等電位,這一特性稱為虛假短路,簡稱虛短。顯然不能將兩輸入端真正短路。那么在電路設計中,如何分析虛斷與虛短運放電路呢?

2019-03-27 09:39:16

Vin 的電壓,但是這個輸出電壓 Vout 是剛好低于 Vin 的,以保證的運放兩個輸入端之間有足夠的電壓差 Ve,來維持運放的輸出,也就是 Vout=Ve*A。 運放電路中的負反饋然后,這個電路

2020-02-28 08:00:00

運放電路,好像還有一些用,需要的來下載吧

2015-04-04 22:44:03

運放電路中沒有反饋電路,那它起什么作用?

2015-05-27 11:06:38

的噪聲。查看LM2904手冊,噪聲電壓密度曲線如下:我們要先求電路的帶寬噪聲,系統帶寬這里指的是運放電路的帶寬,上面電路放大兩倍,LM2904本身的增益帶寬積為0.7Mhz,所以系統3dB帶寬為

2023-02-01 09:58:50

運放電路中的相位補償

2021-03-17 07:04:41

運放電路PCB設計技巧

2020-12-29 07:50:05

本帖最后由 gk320830 于 2015-3-4 20:20 編輯

運放電路是模擬電路中最基本的電路,也是每個工程師必須要掌握的電路!!

2012-07-27 20:13:54

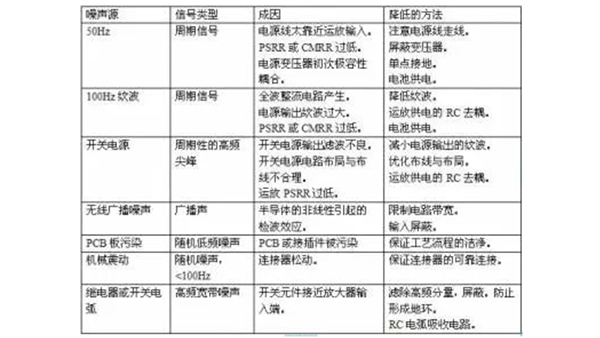

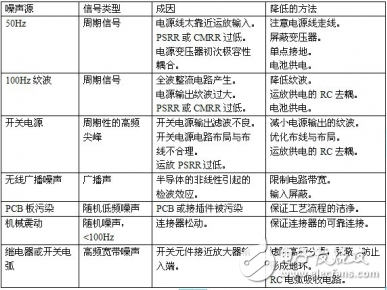

常見外部噪聲源運放電路如何降噪

2021-02-26 06:03:22

運放電路的七大應用場景

2021-03-11 07:49:46

OPA690 運放電路的實物電路為什么沒有輸出電壓沒有放大?仿真是放大10倍的。搞不懂啊,頭疼!!!

2019-07-28 21:58:33

各位前輩好,小弟初學開關電源知識,在學習電路過程中,遇到一個運放電路(如圖所示),不是很理解。這應該是一個反向比例放大器沒錯,可是電路中C54,C50以及R101各起什么作用呢,麻煩各位前輩不吝賜教,感激不盡~~

2015-12-10 10:36:27

此運放電路怎么計算啊,求解答

2014-08-26 18:39:05

運放電路輸出怎么計算

2021-08-23 11:57:19

降低噪聲與干擾1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。(2) 可用串一個電阻的辦法,降低控制電路上下沿跳變速

2010-02-26 11:42:31

小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路上下沿

2019-01-26 22:53:49

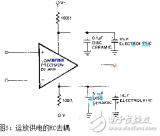

以上兩個參數,可以合理的設計電源工作頻率。 3.電源布局設計---噪聲的來源和降低 1)運放的輸入與輸出 在設計電源時,良好的布局可以降低電源噪聲,電源噪聲主要有三種:運算放大器的輸入與輸出

2023-03-16 15:55:02

~5V的范圍, 我需要做如下的運算之后把結果數據采集卡:vo=(vi1+vi2)-(vi3+vi4)附件圖上是我設計的電路, 實際的運放我選擇的是LM318, 網上說這個運算放大器的速度比較快(因為需要

2014-10-29 16:19:59

14腳,...使用LM324的升壓器怎么做?LM324D運放電路故障分析LM324簡易電子琴電路仿真proteus5V單電源供電LM324組成的差分放大電路,輸出波形被截波>>

2018-08-29 17:26:16

小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路上下沿

2018-09-18 15:40:54

的一些小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路

2018-11-28 17:05:55

STM32的ADC電路中,運放的電源端是否應該接VDDA和VSSA?經驗少,求指導~~~謝謝!

2016-01-26 21:00:38

單獨的運放電路好畫,可怎么才能在原理圖中畫lm324的運放電路,才能識別出dip14的封裝來啊,但是一個一個的運放單獨畫,由于運放電路的管腳,這樣就不能得到lm的封裝了,請教高手指點,是不是定義管腳啊,怎么定義啊

2009-02-11 19:35:34

在用multisim對用集成運放搭建的放大電路進行噪聲仿真與噪聲系數仿真時:噪聲仿真中最后輸出的噪聲是否包含了集成運放本身的輸入噪聲?還是只有電路中電阻元件產生的噪聲?噪聲系數仿真中輸出的噪聲系數dB值為什么為負數?理想狀態輸入輸出信噪比相等噪聲系數為1即0dB,怎么會出現負數呢?謝謝大家。

2020-05-22 00:38:00

需要先來透測的學習運放電路的內部結構和原理,對于我們來說運算放大器是模擬電路中十分重要的元件,它能組成放大、加法、減法、轉換等各種電路,我們可以運用運放的“虛短”和“虛斷”來分析電路,然后應用歐姆定律

2021-09-08 06:00:00

將該電阻移動到正相端,與R1串聯在輸入端。這里額外多插入一句,同相比例運放具有高輸入阻抗,低輸出阻抗的特性,廣泛應用在前置運放電路中。第三、 相位補償如何選擇當我們閱讀一個集成運放數據手冊的時候,會發

2019-09-17 07:00:00

小竅門。下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門:(1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。(2) 可用串一個電阻的辦法,降低控制電路上下沿跳變速

2018-03-10 21:32:11

匹配精度上高幾個數量級,確保數據表規格滿足精密集成電路(IC)要求。在電源方案的單片IC設計中,我們經常會用到精確匹配內部組件的能力。例如,通過精確匹配運放的輸入晶體管來提供低失調電壓。如果我們非得

2018-03-30 17:10:04

在全波整流的線性穩壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個因素:運放在100Hz時的電源抑制比

2018-03-28 17:14:04

對兩個運放電路的原理分析不明白,希望論壇里的高手能指導一下,比如,電路中每個輸出點的電壓是多少以及原理是什么,希望各位的指導能讓我理解的更正確,更全面!

2016-03-30 17:11:48

從0學運放,史上最全運放電路設計入門資料從零學運放—01運算放大器的參數從零學運放—02怎樣分析運放電路從零學運放—03 運放設計中的常遇到的三FAQ從零學運放—04 單電源運放的設計從零學運放

2017-04-08 16:44:35

從零學運放—05 單電源運放電路的實例 電路1、單電源MIC放大電路*常見駐極體MIC(常見咪頭,當然也有動圈的用的少),需要偏置電壓才能工作,給偏置電壓電路才能輸出電壓信號。那么咪頭很容易引起低噪

2017-04-26 09:57:57

我最近使用multisim12仿真分析簡單運放電路的總輸出噪聲,電路圖如下所示,但是發現仿真輸出結果和自己根據運放datasheet上的數據計算出來的結果相差很大。也不知道是不是我用錯了,請問該如何使用?求大神幫忙。

2016-03-25 17:19:32

如果想要更小的噪聲的話應該依據什么選呢?另外如果想在現有電路基礎上降噪,有什么合適的辦法呢?最后想了解運放電路噪聲降低的問題的話,有什么資料和書籍可以看呢,現在有點不知道從哪下手?十分感謝!!!

2018-12-05 16:26:08

關于集成運放,我們在學校學習的時候,都是雙電源的,有正電源VCC和負電源-VCC,而且運放的datasheet里面,也是標注的是雙電源的。而在實際應用中我們發現,電路一般只有正電源,不會有負電源

2021-12-27 07:10:45

對于單電源運放電路的設計要比雙電源的復雜。小弟看到書上說當信號源以地為參考時,單電源運放電路會承受很大的輸入共模電壓.請教大神們這句話怎么理解?

2012-09-02 21:45:52

各種運放電路

2015-03-14 19:22:25

我用同相輸入運放電路放大一下轉速正弦信號時,LM324使用單電源5V供電, 為什么到正弦波的負半周輸出變成了高電平?見附圖,負半周輸出不是應該是0電位嗎?

補充內容 (2017-9-24 18:19):

用Multisim仿真也是這樣的結果,說明電路是對的,但是不理解為什么這樣。

2017-09-18 18:45:02

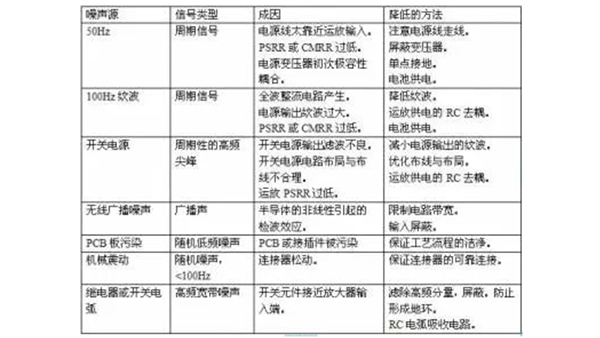

外部噪聲源

電源紋波

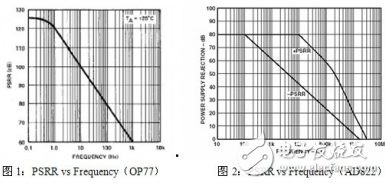

在全波整流的線性穩壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個因素:運放在

2023-11-21 06:27:27

中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個因素:運放在100Hz時的電源抑制比(PSRR),穩壓器的紋波抑制比及

2017-10-19 23:34:27

源 電源紋波在全波整流的線性穩壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個

2018-12-29 10:10:32

,可以合理的設計電源工作頻率。3. 電源布局設計 --- 噪聲的來源和降低1)運放的輸入與輸出在設計電源時,良好的布局可以降低電源噪聲,電源噪聲主要有三種:運算放大器的輸入與輸出,參考電壓和斜坡。如下

2020-10-03 19:30:00

也是經常使用的。輸入電壓和輸出電壓都是參考地給出的,還包括正負電壓的擺動幅度極限Vom以及最大輸出擺幅。 單電源供電的電路(圖1中右)運放的電源腳連接到正電源和地。正電源引腳接到VCC+,地或者VCC-

2018-09-19 09:58:22

分享最簡單可行的兩個步驟去有效降低測試中的噪聲

2021-05-07 06:54:16

如何確定運放電源需要多大的電流? 比如 這個-6V只是專門給運放供電的,那么如何確認這個運放對于-6V電源的電流的需求呢?

2019-09-18 10:14:55

的線性穩壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個因素:運放在100Hz時的電源抑制比(PSRR),穩壓器

2019-06-18 07:30:00

使用的。輸入電壓和輸出電壓都是參考地給出的,還包括正負電壓的擺動幅度極限Vom以及最大輸出擺幅。

單電源供電的電路(圖1中右)運放的電源腳連接到正電源和地。正電源引腳接到VCC+,地或者VCC-引腳連接

2024-01-08 08:26:03

較高. 兩個單運放型雖然可以實現整流的目的,但是輸入輸出特性都很差.需要輸入輸出都加跟隨器或同相放大器隔離. 各個電路都有其設計特色,希望我們能從其電路的巧妙設計中,吸取有用的.例如單電源全波電路

2011-07-23 09:43:36

`30個常用運放電路供壇友學習點擊下載:[hide][/hide]`

2011-10-14 10:35:40

` 本帖最后由 weijianli000 于 2012-12-5 09:24 編輯

常用運放電路集錦,希望對大家有幫助`

2012-12-05 09:22:42

降低開關電源輸出紋波與噪聲的常用方法

2021-03-16 13:50:26

是地,地,電源,地。運放平面上的鋪銅不接元器件,單點接地輸入電源地,運放電路中的接地通過過孔接到第二層的鋪銅,一級和二級運放之間的信號傳遞走第二層。請問這樣正確嗎?

2014-12-10 12:38:49

虛短是什么?虛斷又是什么?怎樣去計算運放電路的放大倍數?

2021-09-28 06:56:44

大家用SIM900A免提運放電路推薦下 謝謝

2019-01-10 10:25:33

各位大俠:你們好! 遇到一個運放電路,不知其工作原理,請各位指點一下,電路圖如下:測試輸入輸出電壓在工作過程中變化:當Vin_1輸入電壓為0V時,Vout(第4腳)輸出為0V;當Vin_1輸入電壓為

2017-04-28 11:48:16

如何降低運放電路中的電源噪聲你能從這本書中學到什么這本書從電源噪聲產生的原因出發,深入分析了消除電源噪聲干擾的對策和影響準確性的因素。其中包括:電源噪聲產生的各種原因分析電源噪聲余量該從何分析如何消除電源

2019-02-26 18:13:03

關于運放電路的些問題,我從學校帶到了工作中,甚至還很長一段時間固執的以為 運放IC前面的隔直電容會和運放IC組成個微分器,一直沒多想過。到用的時候出了問題才走出這一誤區!希望此貼能給大家以幫助

2018-07-19 02:08:40

這是我搭建的一個雙極性運放電路 增益設置100倍放大不變 輸出是+-2.5v.現在希望增加一個2.5V的上拉電壓,將其變成單極性輸出 也就是0-5V 通過模擬 發現在負電源和R1之間增加一個100K

2022-07-18 09:18:39

這是一個運放電路,我不太清楚是什么原理,請教各位老師解答,感謝!

2020-04-20 10:42:56

斬波運放的工作原理是什么?怎樣去設計斬波運放電路?如何降低D類音頻系統的低頻噪聲和電壓失調?

2021-04-23 07:28:32

這個運放電路怎么分析?

2019-09-12 02:27:42

:從虛斷,虛短分析基本[url=https://bbs.elecfans.com/jishu_200255_1_1.html]:從虛斷,虛短分析基本運放電路 運放電路[/url]

2012-09-23 15:42:16

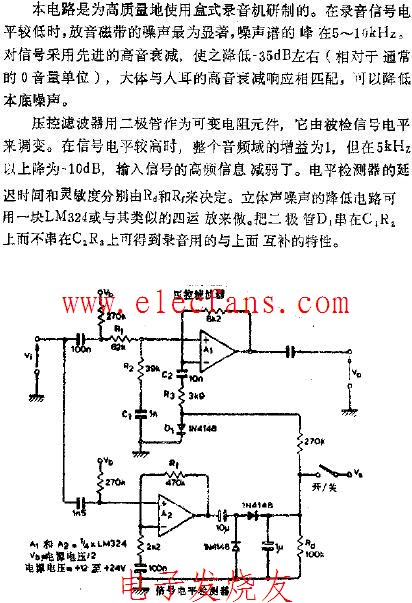

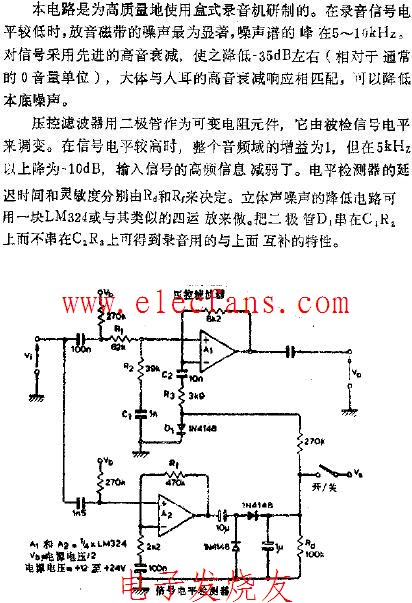

降低動態噪聲的電路圖

2008-02-25 22:09:09 684

684

運放電路的電源噪聲電路圖

2009-07-17 14:52:56 957

957 無噪聲的的功放電源電路

工作原理:交流電源輸入經T1進行濾波后分成兩路輸出,一路去降壓變壓器T3,在T3的初

2010-10-03 15:48:20 3147

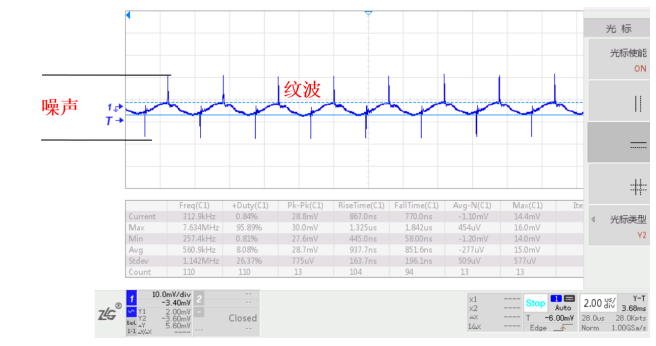

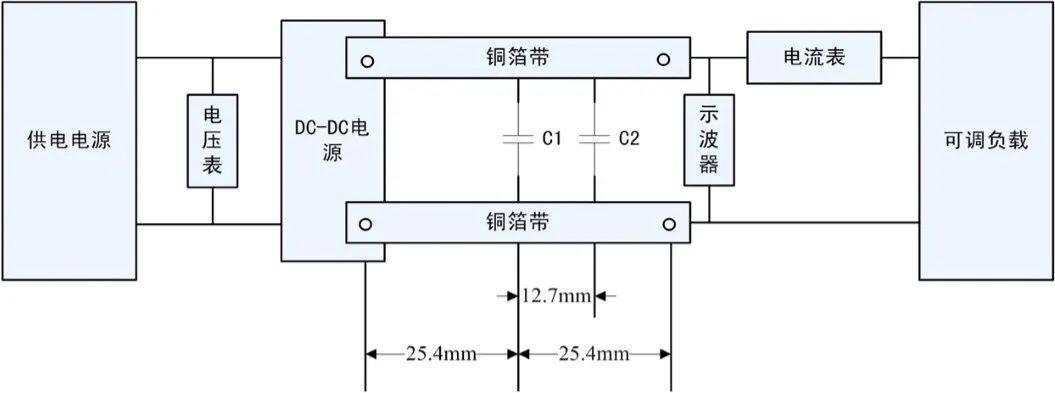

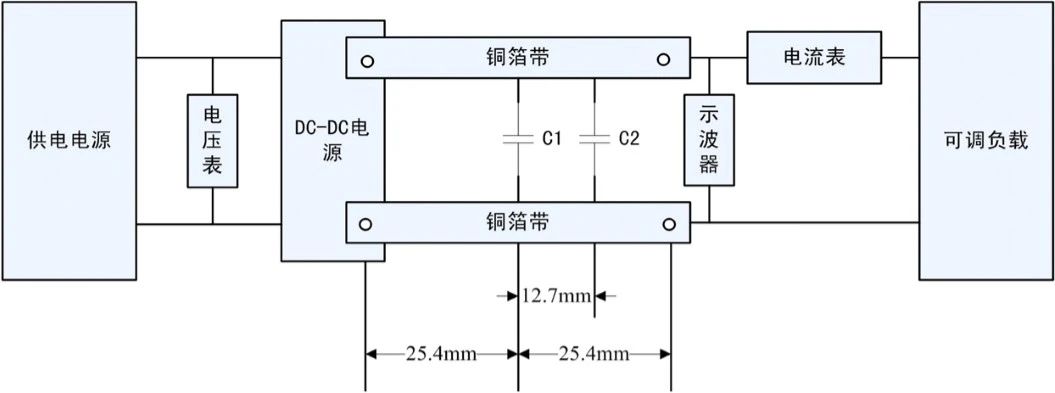

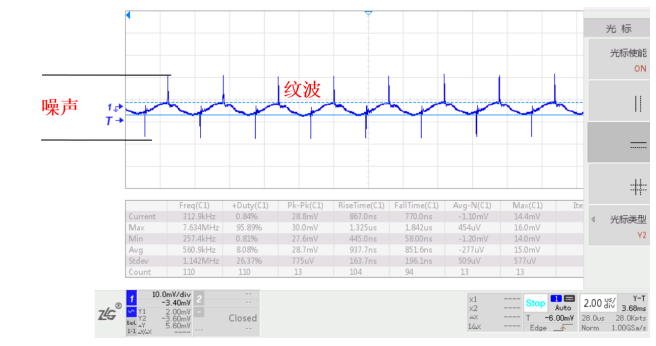

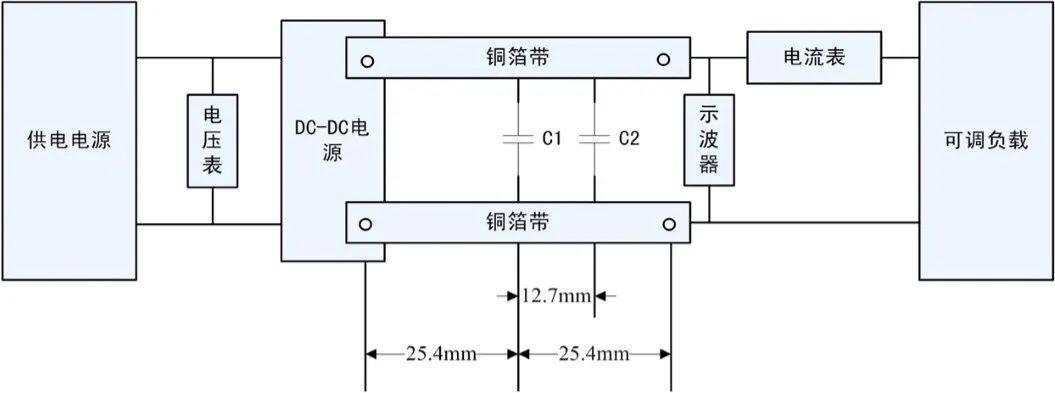

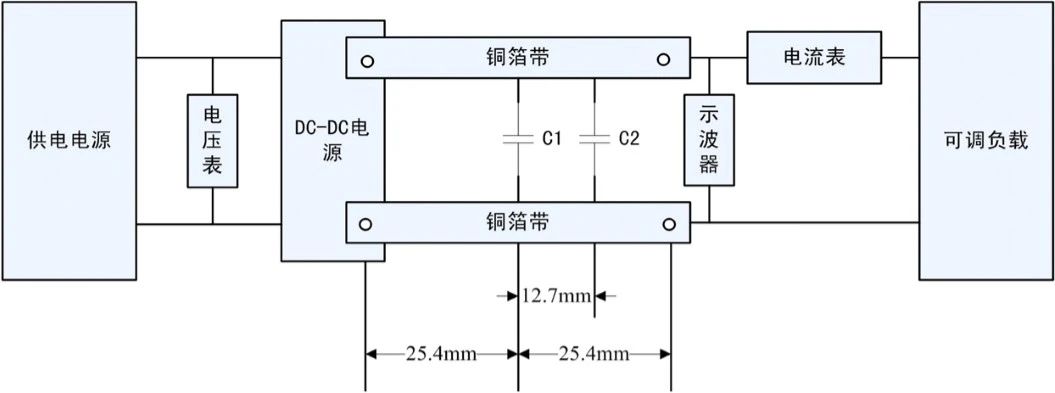

3147 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。 1、電源的紋波與噪聲圖示 紋波和噪聲即:直流電源輸出上疊加的與電源開關頻率同頻的波動為紋波,高頻雜音為噪聲。

2016-11-09 02:08:11 8958

8958

如何降低電源紋波噪聲的分析與應用

2017-02-08 01:27:55 16

16 在全波整流的線性穩壓供電的電路中,100Hz紋波是主要的電源噪聲,對于運放電路,100Hz噪聲電平通常要求控制在10nV-100nV(RTI)內,這取決于三個因素:運放在100Hz時的電源抑制

2018-06-13 09:14:00 8729

8729

開關電源的特征就是產生強電磁噪聲,若不加嚴格控制,將產生極大的干擾。下面介紹的技術有助于降低開關電源噪聲,能用于高靈敏度的模擬電路。

2018-10-14 10:43:00 4470

4470 紋波噪聲是衡量電源的一個重要指標,但有多少人知道紋波和噪聲其實是兩個性能指標,降低紋波和噪聲的方法是有一定區別的,本文將與大家一起探索如何降低紋波和噪聲。

2019-06-20 14:27:08 11684

11684

、散彈噪聲和低頻噪聲(1/f噪聲)等;外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。

常見外部噪聲源...

2022-02-22 11:23:41 1732

1732

電子發燒友網為你提供在運放電路設計中降低電源噪聲的主要措施資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-24 08:47:12 14

14 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。那么模塊的紋波噪聲該如何降低?下文為大家從紋波噪聲的波形、測試方式、模塊設計及應用的角度出發,闡述幾種有效降低輸出紋波噪聲的方法

2022-02-11 15:18:00 13

13 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。紋波噪聲的測試方法對于中小

2023-05-08 09:48:54 472

472

在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。

2023-06-20 17:48:24 1184

1184

降低電源紋波噪聲的方法與實例

2023-10-24 17:37:22 261

261

運放電路的噪聲組成 運放電路是現代電子技術中最重要的組成部分之一,其主要目的是放大電信號,并將不同信號進行復雜處理。然而,所有電路都存在著一定的噪聲,而運放電路也不例外。本文將詳細探討運放電路

2023-10-30 09:11:54 332

332 降低開關電源噪聲

2023-11-24 15:39:50 186

186 電源濾波器是怎么降低電源噪聲的? 電源濾波器是一種電子裝置,用于減少或消除電源中的噪聲。噪聲是電力系統中的一個常見問題,它可以由各種因素引起,包括電源脈動、電源雜散、電磁干擾等。這些噪聲不僅會對

2023-12-15 14:37:56 374

374

電子發燒友App

電子發燒友App

評論