獲得ADC的最佳SNR性能并不僅僅是給ADC輸入提供低噪聲信號的問題,提供一個低噪聲基準電壓是同等重要。雖然基準噪聲在零標度沒有影響,但是在全標度,基準上的任何噪聲在輸出代碼中都將是可見的。對于某個

2022-07-13 09:17:27 1039

1039 電流,合規范圍減小至1V左右。應注意,DAC2902的配置不超過合規范圍,以避免失真性能和整體線性度下降。當最大滿標度輸出信號限制在約0.5Vp-p時,通常可獲得最佳失真性能。50?雙端接負載和20mA

2020-09-14 17:22:30

LTC2656采用纖巧20 引腳4mmx 5mmQFN和TSSOP 封裝。該器件在整個溫度范圍內提供 ±4LSBINL最大值,比最接近的 8 通道同類器件好 3 倍。0.1%(最大值) 的低增益誤差

2021-04-19 06:05:37

親愛的社區,我一直與ADC D-S的PSoC5LP沒有成功地放大2個divand信號與5MVPP最大。我讀過不同的文件,對此我感到很困惑。在ADC Delta Sigma 3.30參考文獻的第9頁中

2018-09-20 16:34:34

源的輸出電阻。這種電荷泵的作用對于在滿標度下與VIN(+)輸入電壓的連續轉換更為不利。對于連續轉換1.8款MHz時鐘頻率,輸入電壓為5V,該直流電流最大約為5微安。因此,旁路電容器不應對于高電阻源(》1 k

2020-07-10 14:59:34

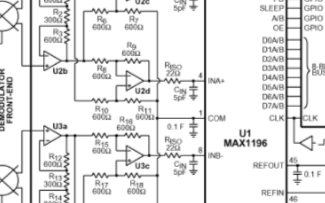

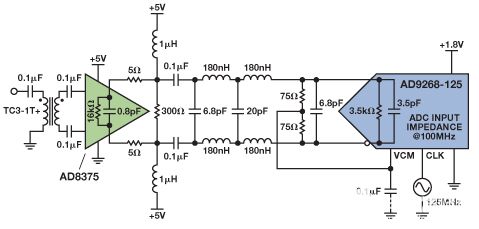

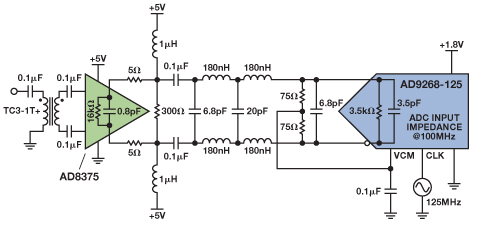

性能。問題許多采用高速ADC的實際應用都需要某種驅動器、放大器或增益模塊,用以將輸入信號縮放到滿量程模擬輸入范圍1 ,確保獲得最佳 信噪比 (SNR)和無雜散動態范圍(SFDR)。此外,差分放大器也可以

2018-10-23 11:43:54

器,將較高帶寬信號搬移到ADC的有效帶寬。要想該技術取得成功,ADC跟蹤-保持電路的帶寬必須能夠處理預期的最高頻率信號。單極性對于單端模擬輸入ADC,單極性信號輸入范圍為零幅(通常為地)至滿幅(通常為基準

2019-02-25 13:52:58

DAC輸出端產生的噪聲。在下圖中,DAC輸出端的饋通是串行時鐘信號噪聲的結果。

動態范圍

動態范圍定義為器件本底噪聲至其規定最大輸出電平之間的范圍,通常以dB表示。ADC的動態范圍為ADC能夠

2023-12-18 07:08:34

時間點有用信號幅度與噪聲幅度之比,該值越大越好。對于由數字采樣完美重構的波形,理論上的最大SNR為滿幅模擬輸入(RMS值)與RMS量化誤差(剩余誤差)之比。理想情況下,理論上的最小ADC噪聲僅包含

2018-10-17 09:44:40

3.3V的交流電壓,正弦信號轉化為數字信號,若3.3V用數字信號100表示,則1.65V則用熟悉信號50表示。一. 采集信號范圍:0-3.3VADC 輸入范圍為: VREF- ≤ VIN ≤ VREF+。由 VREF-、 VREF+ 、 VDDA 、 VSSA、這四個外部引腳決定.在設計時,已經將VREF-與

2021-08-19 08:12:31

的特性以確保足夠的性能水平。使用與“在ADC中測量PSRR”中相同的等式,參見下面的等式1和2。現在可以估計DC / DC轉換器中存在的最大允許紋波,現在考慮到ADC直接由包含紋波的電源供電。圖7:非

2018-07-24 17:42:15

應用中,若發現啟動ADC之后VREF端無電壓,則應立即將芯片復位,并檢查模擬輸入信號的采集放大部分。在確保進入ADμC812的模擬信號在0~+2.5 V范圍內之后,才能再次啟動ADC。實際應用時,應

2011-07-15 15:00:08

工作輸入范圍的比率。更確切地說,TUE是單位為最低有效位 (LSB) 的DC誤差技術規格。最低有效位 (LSB) 代表ADC的實際和理想傳遞函數之間的最大偏離。這個技術規格假定未執行系統級校準。在概念上

2018-09-12 11:48:15

放大的成本可能會使無需外部放大器的高分辨率ADC更吸引人。低分辨率方案的最大優點在于其對基準的要求。設計能在整個時間和溫度范圍內穩定達到16位分辨率的電壓基準、電流源或參考電阻通常是不切實際的。該實例中

2019-06-10 05:00:05

方根噪聲隨著輸出數據速率增加而增加。不過,在整個輸出數據速率范圍內,該器件均能保持良好的噪聲性能。 圖3. AD7190在不同輸出數據速率下的均方根噪聲如果使用靈敏度為2 mV/V的2 kg稱重

2018-08-22 13:38:34

與可編程的高低限制進行比較,并可為ADC輸出數據在設定的門限值內、外、高或低自動生成可編程中斷。使用數據窗口比較器,設計人員能夠配置ADC來自動檢查“水池滿”液面監測器輸入,直到數據窗口比較器發出一個中斷信號給MCU程序為止。當觸發中斷時,MCU可以中斷當前執行的任務并切換到嚴密控制水池系統的任務中。

2017-12-19 17:10:08

在發生超范圍情況時,ADC的輸出數據是什么樣子?

2023-12-21 06:20:04

信號?●在模擬還是數字(IF采樣)域中?選擇ADC的動態范圍選擇ADC本身就值得討論。ADC的動態范圍可確定系統架構(反之亦然)。首先,我們要查看信號帶寬和采樣頻率(準確的采用頻率通常由時鐘和/或幀

2018-10-10 11:27:09

止ADC過驅動。如果接通衰減18db(或任何其他任意值),則系統的信號動態范圍將增加18db。當輸入信號達到編程設定的上限時,該過程開始。在典型應用中,這可以設置為滿標度以下1db(用戶可定義)。當滿足該

2020-07-16 15:36:37

AD694配置有10 V輸入滿標度時,可使用圖7所示的網絡調整量程。該方案允許在標稱值以上或以下的跨度近似線性調整。量程調整不與4毫安偏移量相互作用。 要選擇RS和RT,請選擇X,所需的調整范圍,作為

2020-07-17 14:52:19

,指定的負滿標度代碼(16位級別為12288)與理想的車輛識別號+車輛識別號-(-200毫伏)之間的偏差。增益誤差包括參考誤差。 信噪比(SINAD) 這個比率是在ADC輸出端測得的信號與(噪聲

2020-07-10 15:23:13

的偏差。增益誤差包括參考誤差。信噪比(SINAD)這個比率是在ADC輸出端測得的信號與(噪聲+失真)的比率。信號是基波的均方根振幅。噪聲是所有非基本信號的總和,最多為采樣頻率(fS/2)的一半,不包括

2020-09-25 17:55:01

模擬域中的偏移誤差。滿標度誤差效應是線性的,只要輸入信號在adc的全動態范圍內,就不會引起問題。一些應用程序總是要求輸入信號跨越整個模擬輸入動態范圍。在這種應用中,必須將偏移量和滿標度誤差調整為零

2020-07-02 15:01:47

模擬域中的偏移誤差。滿標度誤差效應是線性的,只要輸入信號在adc的全動態范圍內,就不會引起問題。一些應用程序總是要求輸入信號跨越整個模擬輸入動態范圍。在這種應用中,必須將偏移量和滿標度誤差調整為零

2020-07-02 10:44:28

誤差對系統性能影響很小或沒有影響。通過交流耦合,可以消除模擬域中的偏移誤差。滿標度誤差效應是線性的,只要輸入信號在ADC的全動態范圍內,就不會引起問題。一些應用程序總是要求輸入信號跨越整個模擬輸入動態

2020-07-17 14:36:40

計算: 增益誤差 增益誤差是測量值和理想值之間的差ADC的滿標度輸入電壓范圍。諧波失真,秒有效值信號振幅與二次諧波分量,用dbc表示。 諧波失真,第三 有效值信號振幅與三次諧波分量,用dbc

2020-07-20 17:26:09

IOUTFS=2毫安時)。當IOUTA和IOUTB處的最大滿標度信號不超過0.5v時,可實現單端或差分輸出的最佳失真性能。要求AD9760的輸出(即VOUTA和/或VOUTB)擴展其輸出符合范圍的應用應相應

2020-09-25 17:50:28

信號可能會更高或更低。在定義最大FSCR時,再次加入裕度以適應固有增益誤差。此外,對于大于所選范圍的標稱滿標度值的滿標度輸入,由于放大器的凈空空間有限,在某些電壓下各種內部電路可能飽和。這最有可能發生

2020-07-06 14:53:27

:為了獲取最高精度,美信信號鏈方案能夠提供業內領先的性能指標,包括:初始精度、長期穩定性/溫漂、低噪聲、器件在整個工業級溫度范圍內的一致性等。雙極性/高壓信號鏈方案:許多工業系統工作在較高電壓,也可能需要測量

2014-01-20 10:04:20

對于具有差分輸入的開關電容 ADC,只要輸入電壓在 GND/VDDA 范圍內,我預計共模電壓不會受到限制。然而,STM32 ADC 僅允許 (Vref-VDDa) /2 左右的小范圍共模電壓。在某些

2022-12-14 06:13:56

最近在做一個項目,運用到ADC采集。在測試過程中發現當ADC值在0xC00即3072時,采集的電壓即使在一定范圍內變化,ADC并不會改變或者說值變化1、2,跳出該范圍ADC又恢復正常。按設計來說

2019-02-18 07:28:28

來自MCU的電壓我可以利用 ADC 全范圍的引腳是引腳 5 和 6,因為沒有來自 MCU 的殘余電壓。ST,你能說明這個問題嗎?ADC 的整個范圍只能用于引腳 5 和 6 嗎?或者是否有一些我需要注意的位寄存器,以禁用那些可能導致 MCU 在引腳 7 上輸出電壓的引腳上的任何其他潛在功能?

2022-12-20 06:02:42

使用TC7107 ADC實現TC7106A輸出范圍內和超范圍信號的典型應用。低成本,高分辨率指示儀表僅需要顯示器,四個電阻器和四個電容器。該器件采用低功耗和9V電池供電,適合便攜式應用

2019-07-25 08:36:02

標度輸入,建議使用40kΩ輸入電阻器。其他輸入電壓范圍可以通過改變R1的值。R1應為金屬膜類型,以獲得良好的穩定性。制造公差可產生大約±10%的變化在輸出頻率。滿標度輸出頻率可以是通過調整R1的值進行

2020-10-20 16:28:53

WiFi信號滿格網速卻很卡怎么解決?路由器放在哪個位置網速更快?如何調整路由器?

2021-03-10 07:03:15

我下載了官方的泰克示波器驅動,示波器和電腦連接沒有問題,接受的信號是一個200cycle的正弦波,就是一運行vi時示波器自動選擇顯示的信號只有幾個cycle,我想把整個信號脈沖都顯示在示波器上,我

2018-04-01 09:50:33

參考和跟蹤保持。輸出時鐘簡化了數據捕獲。3.采用無鉛100鉛TQFP/EP包裝。4.時鐘DCS在很寬的時鐘脈沖寬度范圍內保持ADC的整體性能。5.或(超出范圍)輸出指示信號何時超出選定的輸入范圍。開關

2020-10-16 16:48:07

時,產生正滿標度輸出。負滿標度輸出-當差動電壓為-4.096V時,產生標度輸出。在每種情況下,實際輸入電壓必須保持在-0.3V至+VDD范圍內。實際模擬輸入電壓-任何一個模擬輸入端相對于GND的電壓。滿

2020-10-13 15:13:28

的LT3999與ADC采樣時鐘同步的情況。請記住,初級到次級電容為開關噪聲提供了一個避免共模噪聲效應的返回路徑。該電容可以在PCB設計中利用重疊的頂層平面和第二層平面實現,以及利用實際電容。 圖

2021-07-22 07:00:00

你好!我正在使用 F746ZG + IHM08M1。我需要配置 2 個絕緣電流傳感器。我的問題是,為什么在 Workbench 中 ICS 增益在 -5V 到 5V 的范圍內,而 ADC 最大工作范圍僅為 3.3V。我應該購買 3.3V 還是 5V 的電流傳感器?謝謝!

2023-01-03 06:57:34

。如果用軟件處理,那么VOFF就變成0伏。 用軟件消除偏移的問題在于,限制了可測量的傳感器范圍。如果偏移是正的,將限制可以測量的最大傳感器輸出,因為放大的傳感器輸出可能比期望的更早達到ADC滿刻度值

2018-11-13 10:36:15

本人使用的是 AD6.9版本的軟件,網上自己下載的破解版本求助各位大神如何在畫原理圖零部件時,如何畫滿整個零件,就是比如電感,如何填滿整個三角符號,讓其變成中間部分是填滿狀態的,謝謝!!!本人純新手,謝謝!!!

2019-06-25 11:46:31

接口。在整個溫度范圍內,LTC2654 DAC 實現了 INL 最大值為 ±4LSB 的 16 位性能,該性能比最接近和具內部基準的同類 16 位 4 通道產品好兩倍。LTC2654 具有 ±2mV

2018-12-06 10:21:11

傳送。通過一個 I2C 兼容兩線接口通信,在 1ksps 輸出速率時僅消耗 1.5mW 功率。±1LSBINL和 DNL、±2mV(最大值) 零標度誤差和 ±1LSB(最大值) 滿標度誤差。AC 輸入

2021-04-15 07:15:24

電流,合規范圍減小至1V左右。應注意,DAC2902的配置不超過合規范圍,以避免失真性能和整體線性度下降。當最大滿標度輸出信號限制在約0.5Vp-p時,通常可獲得最佳失真性能。50?雙端接負載和20mA

2020-09-11 17:30:20

標度轉換說白了就是點斜式求斜率和與Y軸的截距,即y=kx+b,已知X、Y的最大值和最小值,求K值和B值,在程序中用來表示每一個X刻度對應的Y值。

2018-05-12 17:14:09

以用于其他外設的聯動。帶有計算功能的ADC——對轉換結果自動進行計算處理ADC的轉換結果,被用來做某種類型的計算或分析。比如驗證結果是否在一定的范圍內或者用來濾除信號中的噪聲。盡管用來濾波的軟件算法都比

2021-05-18 09:14:06

以用于其他外設的聯動。帶有計算功能的ADC——對轉換結果自動進行計算處理ADC的轉換結果,被用來做某種類型的計算或分析。比如驗證結果是否在一定的范圍內或者用來濾除信號中的噪聲。盡管用來濾波的軟件算法都比

2022-04-19 08:00:00

LTC2378-20 提供了一種數字增益壓縮 (DGC) 功能,其把全標度輸入擺幅定義為介于 ±VREF 模擬輸入范圍的 10% 和 90% 之間。該功能允許由單個正電源來給 SAR ADC 驅動器

2018-10-31 10:20:33

引言要獲得 ADC 的最佳 SNR 性能并不僅僅是給 ADC 輸入提供低噪聲信號,提供一個低噪聲基準電壓是同等重要。雖然基準噪聲在零標度沒有影響,但是在全標度,基準上的任何噪聲在輸出代碼中都將是可見

2019-07-25 07:15:15

動態相位對準(DPA)電路和對新的外部存儲器接口的支持。AD芯片可以穩定工作在100 MHz,FPGA速度可高達幾百MHz,故可保證系統的測量精度。那么有誰知道如何利用ADC和FPGA設計脈沖信號測量嗎?

2019-07-31 06:25:45

請問如何利用混合信號MCU發揮最大設計潛能?

2021-04-21 06:52:55

信號完整性是指信號在信號線上的質量,即信號在電路中以正確的時序和電壓作出響應的能力。如果電路中信號能夠以要求的時序、持續時間和電壓幅度到達接收器,則可確定該電路具有較好的信號完整性。反之,當信號不能

2018-07-31 17:12:43

也有,但是價格極貴,不在本文討論范圍之列。如何使用單極性 ADC 對雙極性信號進行采樣呢?有兩種方法,下面舉例說明。18.9.1 運放法例 18.1 利用 4.096V 滿量程輸入的 ADC 來采集-10V 到+10V 的輸入信號。 解決方案, 可以使用運放對信號進行縮放和平移, 如圖 18.18 所示

2022-01-21 07:33:03

我們在電路板上使用 MIMXRT1172AVM8A 處理器。我們想使用處理器的 ADC 功能。VREFH 引腳連接到 1.8V。在我們的設備中,我們的 ADC 輸入信號范圍為 0 至 3.3V。我們

2023-03-17 06:35:18

、雙通道或三通道轉換●您目前如何生成正交信號?●在模擬還是數字(IF采樣)域中?選擇ADC本身就值得討論。ADC的動態范圍可確定系統架構(反之亦然)。首先,我們要查看信號帶寬和采樣頻率(準確的采用頻率通常

2015-01-29 15:54:02

對輸入信號進行數字量化的接收機應用中,系統設計人員必須密切關注絕對最大輸入電壓。該參數直接影響ADC的使用壽命和可靠性。不可靠的ADC可能導致整個無線電系統無法使用,且更換成本也許非常巨大。為了抵消過壓帶

2018-11-01 11:25:01

表示。? 動態范圍(DR)指DAQ/ADC產生的最大輸入信號與最小輸入信號之比。DR用dB表示。? 信納比(SINAD)指實際輸入信號的均方根值與奈奎斯特頻率以下包括諧波但排除直流的所有其它頻譜

2018-10-17 10:37:13

嗨,我需要通過FPGA內部的源同步信號,我該怎么做才能確保來自FPGA的信號在clk和數據之間具有正確的時序相位關系。與輸入的相同。我可以復制兩個輸出。請指教。

2020-05-22 14:19:26

) 新近業界出現的新概念,最先應用于運算放大器領域,指輸出電 壓的幅度可達輸入電壓范圍。在 DA 中一般是指輸出信號范圍可達到電源電壓范圍。(國 內的翻譯并不統一,如“軌-軌”、“滿擺幅”) 主要針對

2017-09-12 14:37:14

與應用編程ADC編程時序調試AD值標度變化1.逼近式ADC原理1.1ADC步驟(1)在將模擬量轉化為數字量的過程中,一般需要經過采樣、量化和編碼三個步驟(2)由于模擬信號在時間上是連續的,而A/D轉換的過程是需要時間的,所以不可能把模擬信號的每一個瞬間值都轉換成數字量,只能在連續變化的模擬量上接一定的

2022-02-18 06:54:10

重要。雖然基準噪聲在零標度沒有影響,但是在全標度,基準上的任何噪聲在輸出代碼中都將是可見的。對于某個給定的 ADC,在零標度測量的動態范圍 (DR) 之所以通常比在全標度或接近全標度測量的信噪比 (SNR

2021-03-05 07:35:24

說的小信號和大信號是相對于放大器的動態范圍來說的信號分類,是兩個不同層面或角度上對放大器特性的描述。任何實際器件都不是理想線性的,特別是在其整個動態范圍內。如果將信號的范圍限制在整個動態范圍中相對

2018-02-07 09:29:57

工作。 9 后制造階段 采取上述措施可以確保電路板的SI設計品質,在電路板裝配完成之后,仍然有必要將電路板放在測試平臺上,利用示波器或者TDR(時域反射計)測量,將真實電路板和仿真預期結果進行比較。這些

2015-01-07 11:44:45

穩定。設計二階濾波的目的是獲得更好的濾波特性和截至頻率。如果ADC內部輸入端沒有buffer,例如Intersil的FemtoCharge系列ADC,ADC輸入端會有明顯的周期性(與采樣頻率一致)吸收電流。這樣,確保輸入信號直流電平控制在ADC所需的電平范圍內就顯的非常重要。

2019-06-19 06:50:39

之間的動態比值。因此,根據定義,該動態范圍不得存在其他雜散頻率。SFDR通常采用功率單位(dBc),量化為目標載波相對于下一個最大有效頻率的功率的范圍。然而,該參數也可以滿量程信號為基準,以功率單位

2018-11-01 11:31:37

aic23b的ADC輸入信號范圍是多少,如何計算得出電壓

2019-08-16 09:42:57

±10V差分信號如何調理到差分ADC可以接受的±2.5V的范圍內?另外采用差分放大器驅動差分ADC時,發現在絕對最大額定值參數中,有個差分輸入電壓電壓,一般比較小,這個參數是不是說明只能輸入的差分信號就這么大?

2018-11-16 10:09:29

±10V差分信號如何調理到差分ADC可以接受的±2.5V的范圍內?另外采用差分放大器驅動差分ADC時,發現在絕對最大額定值參數中,有個差分輸入電壓電壓,一般比較小,這個參數是不是說明只能輸入的差分信號就這么大?

2023-11-27 06:06:36

,限制了可測量的傳感器范圍。如果偏移是正的,將限制可以測量的最大傳感器輸出,因為放大的傳感器輸出可能比期望的更早達到ADC滿刻度值。如果偏移是負的,將無法精確測量很小的傳感器輸出電平,因為在超過放大的偏移

2018-11-01 17:15:51

能會嚴重破壞載波邊帶。總之,電源噪聲應當像轉換器的任何其他輸入一樣進行測 試和處理。用戶必須了解系統電源噪聲,否則電源噪聲會提高轉換器噪底,限制整個系統的動態范圍。電源測試圖6所示為在系統板上測量ADC

2019-12-25 18:03:49

數字式儀表標度變換的實例1、模數轉換式儀表的標度變換2、頻率計數式儀表的標度變換3、時間計數式儀表的標度變換4、累積計數式儀表的標度變換

2010-09-20 09:48:07 28

28 利用網絡結構熵定量分析了無標度網絡拓撲結構的非均勻性.通過引入度秩函數,解析地給出了無標度網絡的網絡結構熵.研究發現當標度指數大于2時,無標度網絡的網絡結構熵

2010-10-15 16:24:57 0

0 簡述了無標度網絡的發現及其特性,闡述了無標度網絡對于系統科學研究的意義,提出$以無標度網絡研究為切入點,深入開展系統結構的研究1

2010-10-26 16:28:04 12

12 為了實現令人驚異的動態范圍,您需要確保最大的信號利用了該ADC的整個滿標度范圍。換句話說,您需要運用所有代碼。怎樣才能做到這一點呢?

2012-11-28 15:08:22 3503

3503 基于復雜網絡理論知識研究了無標度網絡的構造算法,并在原有的BA無標度網絡模型的基礎上,通過加入內部邊和重連邊機制使該網絡模型不但具有無標度特性而且具有現實社會網絡的小世界特性,同時給網絡的節點加入

2017-11-09 17:23:44 3

3 實際應用中有人或許特意挑選一個分辨率比較滿意的ADC芯片或帶ADC的MCU,然而在具體設計的時候,ADC的最大輸入信號離ADC模塊的參考電壓還相差一大截,這時當初挑選的ADC分辨率精度就根本沒有

2018-09-10 17:44:37 12427

12427

當信號沿著PCB走線和很長的電纜傳輸時,系統中的信號噪聲在累積,差分ADC抑制所有以共模電壓出現的信號噪聲。采用差分信號而不是單端信號有兩個優點:差分信號可使ADC動態范圍擴大兩倍,以及提供更好的諧波失真性能。

2020-08-07 14:49:56 585

585

輸入共模電壓范圍(Vcm)對于包含了基帶采樣和高速ADC的通信接收機設計非常重要,尤其是采用直流耦合輸入、單電源供電的低壓電路。對于單電源供電電路,饋送到放大器和ADC的輸入信號應該偏置在Vcm范圍以內的直流電平,能夠消除放大器和ADC設計的一大屏障,因為不必在0V保持低失真和高線性度。

2020-09-17 10:21:32 5713

5713

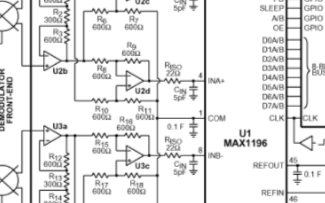

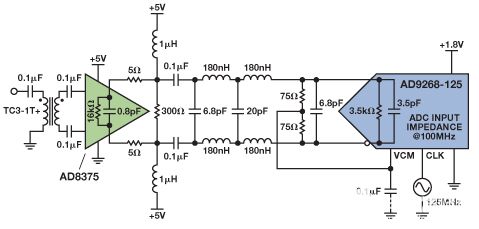

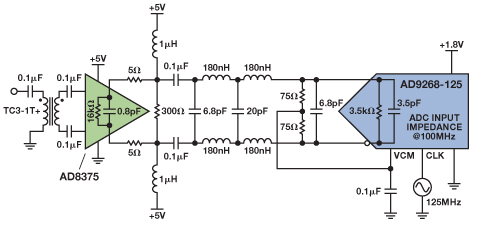

DN468-精心設計IF信號鏈,最大限度提高16位、105Msps ADC的性能

2021-04-14 09:56:02 6

6 設計解決方案3雙極輸入24位A/D轉換器接受±2.5V輸入差分輸入24位A/D轉換器為雙極輸入信號提供半標度零

2021-04-25 10:48:34 1

1 DN468-精心設計IF信號鏈,最大限度提高16位、105Msps ADC的性能

2021-06-18 10:27:30 4

4 最先進的每秒 112 吉比特 (Gbps) 長距離 (LR) SerDes PHY 的設計要求將模數轉換器 (ADC) 的位數降至最低,以實現整個系統占用最小的面積和消耗最小的功率。為此,利用

2022-07-28 08:03:10 1083

1083 MAX1464為高性能、多通道、信號調理器,采用內部16位模數轉換器將模擬輸入信號轉換為數字值。為了最大限度地提高轉換分辨率,必須從輸入信號中剝離偏移,然后放大,同時不超過模數轉換器的線性范圍。本應用筆記描述了高效執行此任務的過程,并提供了流程圖。

2023-01-11 16:48:17 441

441

模數轉換器(ADC)在模擬輸入驅動至額定滿量程輸入電壓時提供最佳性能,但在許多應用中,最大可用信號與指定電壓不同,可能需要進行調整。滿足這一要求的有用器件是可變增益放大器(VGA)。了解VGA如何影響ADC的性能將有助于優化整個信號鏈的性能。

2023-01-30 14:02:45 1236

1236

當模數轉換器(ADC)的模擬輸入被驅動至額定滿量程輸入電壓時,ADC提供優質性能。但在許多應用中,最大可用信號與額定電壓不同,可能需要調整。用于滿足這一要求的器件之一是可變增益放大器(VGA)。了解VGA如何影響ADC的性能,將有助于優化整個信號鏈的性能。

2023-06-17 16:43:09 718

718

AD9361是一款高性能的射頻前端芯片,廣泛應用于無線通信系統中。其中一個重要特性是其具有靈活可調的ADC采樣率。本文將詳細介紹AD9361的ADC采樣率設置范圍,包括其相關特性、設置方法以及在實際

2024-01-04 09:37:57 904

904

電子發燒友App

電子發燒友App

評論