低壓差穩壓器工作原理

隨著便攜式設備(電池供電)在過去十年間的快速增長,象原來的業界標準 LM340 和 LM317 這樣的穩壓器件已經無法滿足新的需要。這些穩壓器使用NPN 達林頓管,在本文中稱其為NPN 穩壓器(NPN regulators)。預期更高性能的穩壓器件已經由新型的低壓差(Low-dropout)穩壓器(LDO)和準LDO穩壓器(quasi-LDO)實現了。

(原文:Linear Regulators: Theory of Operation and Compensation )

NPN 穩壓器(NPN regulators)

在NPN穩壓器(圖1:NPN穩壓器內部結構框圖)的內部使用一個 PNP管來驅動 NPN 達林頓管(NPN Darlington pass transistor),輸入輸出之間存在至少1.5V~2.5V的壓差(dropout voltage)。這個壓差為:

Vdrop = 2Vbe +Vsat(NPN 穩壓器) (1)

LDO 穩壓器(LDO regulators)

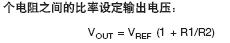

在LDO(Low Dropout)穩壓器(圖2:LDO穩壓器內部結構框圖)中,導通管是一個PNP管。LDO的最大優勢就是PNP管只會帶來很小的導通壓降,滿載(Full-load)的跌落電壓的典型值小于500mV,輕載(Light loads)時的壓降僅有10~20mV。LDO的壓差為:

Vdrop = Vsat (LDO 穩壓器) (2)

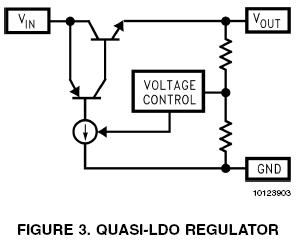

準LDO 穩壓器(Quasi-LDO regulators)

準LDO(Quasi-LDO)穩壓器(圖3: 準 LDO 穩壓器內部結構框圖)已經廣泛應用于某些場合,例如:5V到3.3V 轉換器。 準LDO介于 NPN 穩壓器和 LDO 穩壓器之間而得名, 導通管是由單個PNP 管來驅動單個NPN 管。 因此,它的跌落壓降介于NPN穩壓器和LDO之間:

Vdrop = Vbe +Vsat (3)

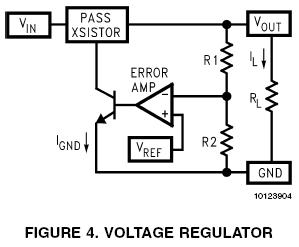

穩壓器的工作原理(Regulator Operation)

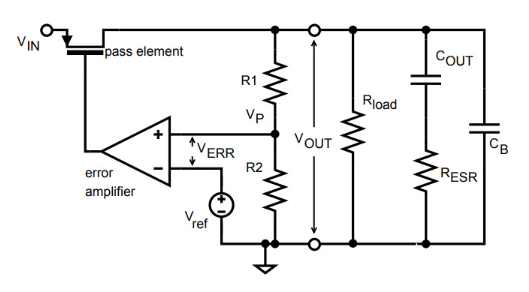

所有的穩壓器,都利用了相同的技術實現輸出電壓的穩定(圖4:穩壓器工作原理圖)。輸出電壓通過連接到誤差放大器(Error Amplifier)反相輸入端(Inverting Input)的分壓電阻(Resistive Divider)采樣(Sampled),誤差放大器的同相輸入端(Non-inverting Input)連接到一個參考電壓Vref。 參考電壓由IC內部的帶隙參考源(Bandgap Reference)產生。 誤差放大器總是試圖迫使其兩端輸入相等。為此,它提供負載電流以保證輸出電壓穩定:

Vout = Vref(1 + R1 / R2) (4)

性能比較(Performance Comparison)

NPN,LDO和準LDO在電性能參數上的最大區別是:跌落電壓(Dropout Voltage)和地腳電流(Ground Pin Current)。跌落電壓前文已經論述。為了便于分析,我們定義地腳電流為Ignd (參見圖4),并忽略了IC到地的小偏置電流。那么,Ignd等于負載電流IL除以導通管的增益。

NPN 穩壓器中,達林頓管的增益很高(High Gain), 所以它只需很小的電流來驅動負載電流IL。這樣它的地腳電流Ignd也會很低,一般只有幾個mA。 準LDO也有較好的性能,如國半(NS)的LM1085能夠輸出3A的電流卻只有10mA的地腳電流。

然而,LDO的地腳電流會比較高。在滿載時,PNP管的β值一般是15~20。也就是說LDO的地腳電流一般達到負載電流的7%。

NPN穩壓器的最大好處就是無條件的穩定,大多數器件不需額外的外部電容。 LDO在輸出端最少需要一個外部電容以減少回路帶寬(Loop Bandwidth)及提供一些正相位轉移(Positive Phase Shift)補償。 準LDO一般也需要有輸出電容,但容值要小于LDO的并且電容的ESR局限也要少些。

反饋及回路穩定性(Feedback and Loop Stability)

所有穩壓器都使用反饋回路(Feedback Loop)以保持輸出電壓的穩定。 反饋信號在通過回路后都會在增益和相位上有所改變,通過在單位增益(Unity Gain,0dB)頻率下的相位偏移總量來確定回路的穩定性。

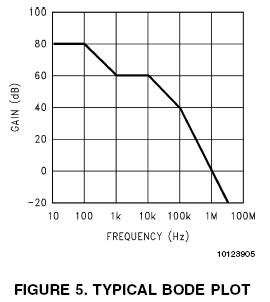

波特圖(Bode Plots)

波特圖(Bode Plots)可用來確認回路的穩定性,回路的增益(Loop Gain,單位:dB)是頻率(Frequency)的函數(圖5:典型的波特圖)。 回路增益及其相關內容在下節介紹。 回路增益可以用網絡分析儀(Network Analyzer)測量。 網絡分析儀向反饋回路(Feedback Path)注入低電平的正弦波(Sine Wave),隨著直流電壓(DC)的不斷升高, 這些正弦波信號完成掃頻,直到增益下降到0dB。然后測量增益的響應(Gain Response)。

波特圖是很方便的工具,它包含判斷閉環系統(Closed-loop System)穩定性的所有必要信息。 包括下面幾個關鍵參數:環路增益(Loop Gain),相位裕度(Phase Margin)和零點(Zeros)、極點(Poles)。

回路增益(LOOP GAIN)

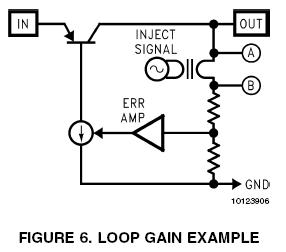

閉環系統(Closed-loop System)有個特性稱為回路增益(Loop Gain)。在穩壓電路中,回路增益定義為反饋信號(Feedback Signal)通過整個回路后的電壓增益(Voltage Gain)。為了更好的解釋這個概念,LDO的結構框圖(圖2)作如下修改(圖6:回路增益的測量方法)。

變壓器(Transformer)用來將交流信號(AC Signal)注入(Inject)到“A”、“‘B”點間的反饋回路。借助這個變壓器,用小信號正弦波(Small-signal Sine Wave)來“調制”(modulate)反饋信號。可以測量出A、B兩點間的交流電壓(AC Voltage),然后計算回路增益。回路增益定義為兩點電壓的比(Ratio):

Loop Gain = Va / Vb (5)

需要注意, 從Vb點開始傳輸的信號, 通過回路(Loop)時會出現相位偏移(Phase Shift),最終到達Va點。相位偏移(Phase Shift)的多少決定了回路的穩定程度(Stability)。

反饋(FEEDBACK)

如前所述,所有的穩壓器都采用反饋( Feedback)以使輸出電壓穩定。輸出電壓是通過電阻分壓器進行采樣的(圖6),并且該分壓信號反饋到誤差放大器的一個輸入端,誤差放大器的另一個輸入端接參考電壓,誤差放大器將會調整輸出到導通管(Pass Transistor)的輸出電流以保持直流電壓(DC Valtage)的穩定輸出。

為了達到穩定的回路就必須使用負反饋(Negative Feedback)。負反饋,有時亦稱為改變極性的反饋(degenerative feedback),與源信號的極性相反(圖7:反饋信號的相位示意圖)。

負反饋與源(Source)的極性相反,它總會阻止輸出的任何變化。也就是說,如果輸出電壓想要變高(或變低),負反饋回路總會阻止,強制其回到正常值。

正反饋(Positive Feedback)是指當反饋信號與源信號有相同的極性時就發生的反饋。此時,回路響應會與發生變化的方向一致。顯而易見不能達到輸出的穩定,不能消除輸出電壓的改變,反而將變化趨勢擴大了。

當然,不會有人在線性穩壓器件中使用正反饋。但是如果出現180°的相移,負反饋就成為正反饋了。

相位偏移(PHASE SHIFT)

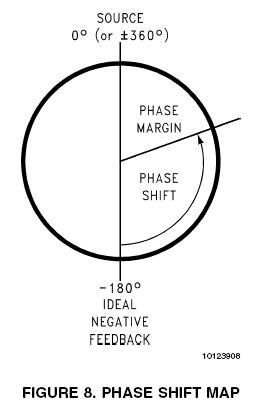

相位偏移就是反饋信號經過整個回路后出現的相位改變(Phase Change)的總和(相對起始點)。相位偏移,單位用度(Degrees)表示,通常使用網絡分析儀(network analyzer)測量。理想的負反饋信號與源信號相位差180°(如圖8:相位偏移示意圖),因此它的起始點在-180°。在圖7中可以看到這180°的偏置,也就是波型差半周。

可以看到,從-180°開始,增加180°的相移,信號相位回到零度,就會使反饋信號與源信號的相位相同,從而使回路不穩定。

相位裕度(PHASE MARGIN)

相位裕度(Phase Margin,單位:度),定義為頻率的回路增益等 0dB(單位增益,Unity Gain)時,反饋信號總的相位偏移與-180°的差。一個穩定的回路一般需要20°的相位裕度。

相位偏移和相位裕度可以通過波特圖中的零、極點計算獲得。

極點(POLES)

極點(Pole)定義為增益曲線(Gain curve)中斜度(Slope)為-20dB/十倍頻程的點(圖9:波特圖中的極點)。每添加一個極點,斜度增加20dB/十倍頻程。增加n個極點,n ×(-20dB/十倍頻程)。每個極點表示的相位偏移都與頻率相關,相移從0到-90°(增加極點就增加相移)。最重要的一點是幾乎所有由極點(或零點)引起的相移都是在十倍頻程范圍內。

注意:一個極點只能增加-90°的相移,所以最少需要兩個極點來到達-180°(不穩定點)。

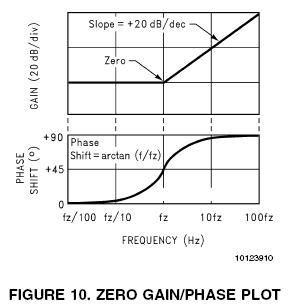

零點(ZEROS)

零點(Zero)定義為在增益曲線中斜度為+20dB/十倍頻程的點(如圖10:波特圖中的零點)。零點產生的相移為0到+90°,在曲線上有+45°角的轉變。必須清楚零點就是“反極點”(Anti-pole),它在增益和相位上的效果與極點恰恰相反。這也就是為什么要在LDO穩壓器的回路中添加零點的原因,零點可以抵消極點。

波特圖分析

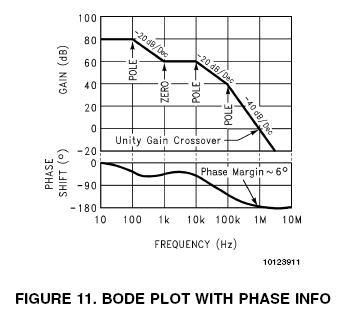

用包含三個極點和一個零點的波特圖(圖11:波特圖)來分析增益和相位裕度。

假設直流增益(DC gain)為80dB,第一個極點(pole)發生在100Hz處。在此頻率,增益曲線的斜度變為-20dB/十倍頻程。1kHz處的零點使斜度變為0dB/十倍頻程,到10kHz處斜度又變成-20dB/十倍頻程。在100kHz處的第三個也是最后一個極點將斜度最終變為-40dB/十倍頻程。

圖11中可看到單位增益點(Unity Gain Crossover,0dB)的交點頻率(Crossover Frequency)是1MHz。0dB頻率有時也稱為回路帶寬(Loop Bandwidth)。

相位偏移圖表示了零、極點的不同分布對反饋信號的影響。為了產生這個圖,就要根據分布的零點、極點計算相移的總和。在任意頻率(f)上的極點相移,可以通過下式計算獲得:

極點相移 = -arctan(f/fp) (6)

在任意頻率(f)上的零點相移,可以通過下式計算獲得:

零點相移 = -arctan(f/fz) (7)

此回路穩定嗎?為了回答這個問題,我們根本無需復雜的計算,只需要知道0dB時的相移(此例中是1MHz)。

前兩個極點和第一個零點分布使相位從-180°變到+90°,最終導致網絡相位轉變到-90°。最后一個極點在十倍頻程中出現了0dB點。代入零點相移公式,可以計算出該極點產生了-84°的相移(在1MHz時)。加上原來的-90°相移,全部的相移是-174°(也就是說相位裕度是6°)。由此得出結論,該回路不能保持穩定,可能會引起振蕩。

NPN 穩壓器補償

NPN 穩壓器的導通管(見圖1)的連接方式是共集電極的方式。所有共集電極電路的一個重要特性就是低輸出阻抗, 意味著電源范圍內的極點出現在回路增益曲線的高頻部分。

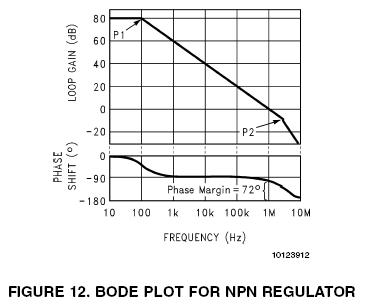

由于NPN穩壓器沒有固有的低頻極點,所以它使用了一種稱為主極點補償(dominant pole compensation)的技術。方法是,在穩壓器的內部集成了一個電容,該電容在環路增益的低頻端添加了一個極點(圖12:NPN穩壓器的波特圖)。

NPN穩壓器的主極點(Dominant Pole), 用P1點表示, 一般設置在100Hz處。100Hz處的極點將增益減小為-20dB/十倍頻程直到3MHz處的第二個極點(P2)。在P2處,增益曲線的斜率又增加了-20dB/十倍頻程。P2點的頻率主要取決于 NPN 功率管及相關驅動電路, 因此有時也稱此點為功率極點(Ppower pole)。另外,P2點在回路增益為-10dB處出現,也就表示了單位增益(0dB)頻率處(1MHz)的相位偏移會很小。

為了確定穩定性,只需要計算0dB頻率處的相位裕度。

第一個極點(P1)會產生-90°的相位偏移,但是第二個極點(P2)只增加了-18°的相位偏移(1MHz處)。也就是說0dB點處的相位偏移為-108°,相位裕度為72°,表明回路非常穩定。

需要兩個極點才有可能使回路要達到-180°的相位偏移(不穩定點),而極點P2又處于高頻,它在0dB處的相位偏移就很小了。

LDO 穩壓器的補償

LDO穩壓器中的PNP導通管的接法為共射方式(common emitter)。它相對共集電極方式有更高的輸出阻抗。由于負載阻抗和輸出容抗的影響在低頻程處會出現低頻極點(low-frequency pole)。此極點,又稱負載極點(load pole),用Pl表示。負載極點的頻率由下式計算獲得:

F(Pl) =1 / (2π × Rload × Cout) (8)

從此式可知,LDO不能通過簡單的添加主極點的方式實現補償。為什么? 先假設一個5V/50mA的LDO穩壓器有下面的條件,在最大負載電流時,負載極點(Pl)出現的頻率為:

Pl = 1 / (2π × Rload × Cout)=1/(2π × 100 × 10-5)=160Hz (9)

假設內部的補償在1kHz處添加了一個極點。由于PNP功率管和驅動電路的存在,在500kHz處會出現一個功率極點(Ppwr)。

假設直流增益為80dB。在最大輸出電流時的負載阻值為RL=100Ω,輸出電容為Cout =10uF。

使用上述條件可以畫出相應的波特圖(如圖13:未補償的LDO增益波特圖)。

可以看出回路是不穩定的。極點PL和P1每個都會產生-90°的相移。在0dB處(此例為40kHz),相移達到了-180°為了減少負相移(阻止振蕩),在回路中必須要添加一個零點。一個零點可以產生+90°的相移,它會抵消兩個低頻極點的部分影響。

因此,幾乎所有的LDO都需要在回路中添加這個零點。該零點一般是通過輸出電容的等效串聯電阻(ESR)獲得的。

使用 ESR 補償 LDO

等效串聯電阻(ESR)是電容的一個基本特性。可以將電容表示為電阻與電容的串聯等效電路(圖14:電容器的等效電路圖)。

輸出電容的ESR在回路增益中產生一個零點,可以用來減少負相移。零點處的頻率值(Fzero)與ESR和輸出電容值密切相關:

Fzero = 1 / (2π × Cout × ESR) (10)

再看上一節的例子(圖13),假設輸出電容值Cout =10uF,輸出電容的ESR = 1Ω。則零點發生在16kHz。圖15的波特圖顯示了添加此零點如何使不穩定的系統恢復穩定。

回路的帶寬增加了,單位增益(0dB)的交點頻率從30kHz移到了100kHz。到100kHz處該零點總共增加了+81°相移(Positive Phase Shift)。也就是減少了極點PL和P1造成的負相移(Negative Phase Shift)。 極點Ppwr處在500kHz,在100kHz處它僅增加了-11°的相移。累加所有的零、極點,0dB處的總相移為-110°。也就是有+70°的相位裕度,系統非常穩定。

這就解釋了選擇合適ESR值的輸出電容可以產生零點來穩定LDO系統。

ESR 和穩定性

通常所有的LDO都會要求其輸出電容的ESR值在某一特定范圍內,以保證輸出的穩定性。 LDO制造商會提供一系列由輸出電容ESR和負載電流(Load Current)組成的定義穩定范圍的曲線(圖16:典型LDO的ESR穩定范圍曲線),作為選擇電容時的參考。

要解釋為什么有這些范圍的存在,我們使用前面提到的例子來說明ESR的高低對相位裕度的影響。

高ESR

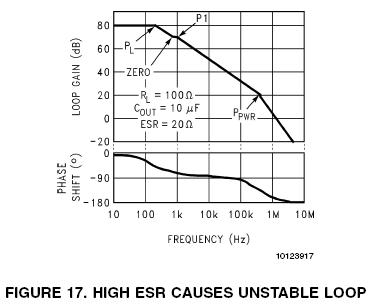

同樣使用上一節提到的例子,我們假設10uF輸出電容的ESR增加到20Ω。這將使零點的頻率降低到800Hz(圖17:高ESR引起回路振蕩的波特圖)。

降低零點的頻率會使回路的帶寬增加,它的單位增益(0Db)的交點頻率從100kHz 提高到2MHz。 帶寬的增加意味著極點 Ppwr 會出現在帶寬內(對比圖15)。分析圖17波特圖中曲線的相位裕度,發現如果同時拿掉該零點和P1或PL中的一個極點,對曲線的形狀影響很小。也就是說該回路受到-90° 相移的低頻極點和發生-76° 相移的高頻極點Ppwr共同影響。

盡管有 14° 的相位裕度,系統可能會穩定。但很多經驗測試數據顯示,當ESR >10Ω時,由于其它的高頻極點的分布(在此簡單模型中未表示)很可能會引入不穩定性。

低ESR

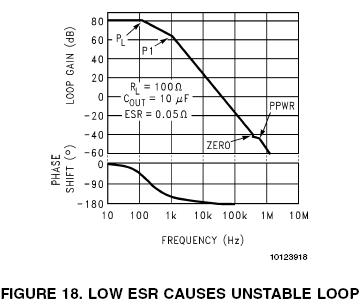

選擇具有很低的ESR的輸出電容,由于一些不同的原因也會產生振蕩。繼續沿用上一節的例子,假定10uF輸出電容的ESR只有50mΩ,則零點的頻率會變到320kHz(圖18:低ESR引起回路振蕩的波特圖)。

不用計算就知道系統是不穩定的。兩個極點P1和PL在0dB處共產生了-180°的相移。如果要系統穩定,則零點應該在0dB點之前補償正相移。然而,零點在320kHz處,已經在系統帶寬之外了,所以無法起到補償作用。

輸出電容的選擇

綜上,輸出電容是用來補償LDO穩壓器的,所以選擇時必須謹慎。基本上所有的LDO應用中引起的振蕩都是由于輸出電容的ESR過高或過低。

LDO的輸出電容,通常鉭電容是最好的選擇(除了一些專門設計使用陶瓷電容的LDO,例如:LP2985)。測試一個AVX的4.7uF鉭電容可知它在25℃時ESR為1.3Ω,該值處在穩定范圍的中心(圖16)。

另一點非常重要,AVX電容的ESR在-40℃到+125℃溫度范圍內的變化小于2:1。鋁電解電容在低溫時的ESR會變大很多,所以不適合作LDO的輸出電容。

必須注意大的陶瓷電容(≥1uF)通常會用很低的ESR(<20mΩ),這幾乎會使所有的LDO穩壓器產生振蕩(除了LP2985)。如果使用陶瓷電容就要串聯電阻以增加ESR。大的陶瓷電容的溫度特性很差(通常是Z5U型),也就是說在工作范圍內的溫度的上升和下降會使容值成倍的變化,所以不推薦使用。

準LDO補償

準LDO(圖3)的穩定性和補償,應考慮它兼有LDO和NPN穩壓器的特性。因為準LDO穩壓器利用NPN導通管,它的共集電極組合也就使它的輸出極(射極)看上去有相對低的阻抗。

然而,由于NPN的基極是由高阻抗PNP電流源驅動的,所以準LDO的輸出阻抗不會達到使用NPN達林頓管的NPN穩壓器的輸出阻抗那樣低,當然它比真正的LDO的輸出阻抗要低。

也就是說準LDO的功率極點的頻率比NPN穩壓器的低,因此準LDO也需要一些補償以達到穩定。當然了這個功率極點的頻率要比LDO的頻率高很多,因此準LDO只需要很小的電容,而且對ESR的要求也不很苛刻。

例如,準LDO LM1085可以輸出高達3A的負載電流,卻只需10uF的輸出鉭電容來維持穩定性。準LDO制造商未必提供ESR范圍的曲線圖,所以準LDO對電容的ESR要求很寬松。

低ESR的LDO

國半(NS)的兩款LCO,LP2985和LP2989,要求輸出電容貼裝象陶瓷電容一樣超低ESR。 這種電容的ESR可以低到5~10mΩ。 然而這樣小的ESR會使典型的LDO穩壓器引起振蕩(圖18)。

為什么LP2985在如此低ESR的電容下仍能夠穩定工作? 國半在IC內部放置了鉭輸出電容來補償零點。這樣做是為了將可穩定的ESR的上限范圍下降。LP2985的ESR穩定范圍是3Ω到500MΩ,因此它可以使用陶瓷電容。未在內部添加零點的典型LDO的可穩定的ESR的范圍一般為100mΩ-5Ω,只適合使用鉭電容并不適合使用陶瓷電容。

要弄清ESR取之范圍上限下降的原因,請參考圖15。上文提到,此LDO的零點已被集成在IC內部。因此外部電容產生的零點必須處在足夠高的頻率,這樣就不能使帶寬很寬。否則,高頻極點會產生很大的相移從而導致振蕩。

使用場效益管(FET)作為導通管LDO的優點

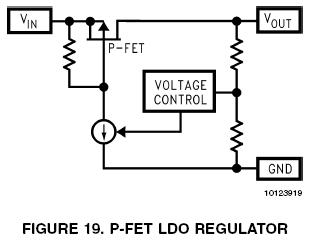

LDO穩壓器可以使用P-FET(P溝道場效應管)作為導通管(圖19:P溝道場效應管LDO內部結構框圖)。為了闡述使用Pl-FET LDO 的好處,在PNP LDO(圖2)中要驅動PNP功率管就需要基極電流。基極電流由地腳(ground pin)流出并反饋回反相輸入電壓端。因此,這些基極驅動電流并未用來驅動負載。它在LDO穩壓器中耗損的功耗由下式計算:

PWR(Base Drive)=Vin × Ibase (11)

需要驅動PNP管的基極電流等于負載電流除以β值(PNP管的增益)。在一些PNP LDO穩壓器中β值一般為15~20(與負載電流相關)。此基極驅動電流產生的功耗可不是我們期望的(尤其是在電池供電的低功耗應用中)。P溝道場效應管(P-FET)的柵極驅動電流極小,較好地解決這個問題。

P-FET LDO穩壓器的另一個優點,是通過調整場效應管(FET)的導通阻抗(ON-resistance)可以使穩壓器的跌落電壓更低。 對于集成的穩壓器而言,在單位面積上制造的場效應功率管(FET power transistors)的導通阻抗會比雙極型開關管(Bipolar ONP Devices)的導通阻抗低。這就可以在更小封裝(Packages)下輸出更大的電流。

電子發燒友App

電子發燒友App

評論