引語

能效和可靠性是所有電子功率變換器必備的主要特性。在與人類社會活動和生態環境保護相關的應用領域,例如,交通、工業、能源轉換等,標準硅基功率開關管已被SiC MOSFET取代,因為 SiC MOSFET在電流密度/芯片面積、擊穿電壓、開關頻率、工作溫度方面表現更出色,可縮減功率變換器的體積和尺寸,同時提高能效[1],[2]。

采用最新一代SiC MOSFET設計功率變換器應該認真考慮器件的可靠性和魯棒性,避免讓異常失效現象破壞系統的整體安全性[3],[4]。短路和雪崩是可能導致電源轉換器開關管嚴重失效的異常事件[5],[6]。

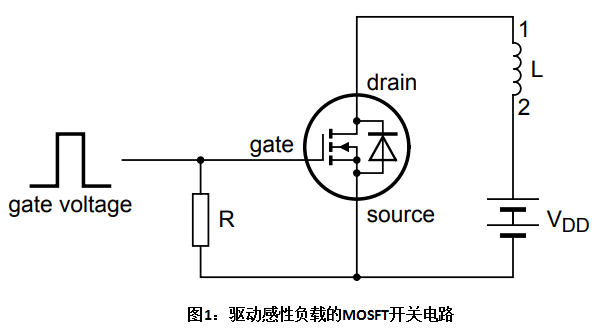

短路事件可能是錯誤和失控的工作條件引起的,例如,器件開關順序命令出錯。當漏源電壓VDS超過擊穿電壓額定值時,會發生雪崩事件[7]。

對于dvDS/dt 和 diD/dt變化率很高的應用,在開關瞬變期間,VDS可能會超過擊穿電壓額定值。高瞬變率結合變換器布局固有的寄生電感,將會產生電壓尖峰,在極端情況下,導致雪崩事件發生[7],[14],[16]。SiC MOSFET可能會出現這些工作條件,分立器件的dvDS/dt可能輕松超過100V/ns,diD/dt超過10A/ns[1],[21] 。

另一方面,電機功率變換器也是一個值得關注的重點,例如,電動汽車的驅動電機逆變器、工業伺服電機等,這些應用的負載具有典型的電感特性,要求功率開關還必須兼備續流二極管的功能。因此,在二極管關斷時,其余器件將傳導負載電流,進行非鉗位感性負載開關UIS操作,工作于雪崩狀態是無法避免的[13]。在這種雪崩期間,除過電壓非常高之外,高耗散能量也是一個需要考慮的重要問題,因為器件必須耐受異常的電壓和電流值。

采用失效檢測算法和保護系統,配合同樣基于“可靠性”標準的變換器設計方法,是很有必要的[20]。但是,除了安全保護和最佳設計規則外,功率開關管還必須強健結實,即具有“魯棒性”,才能耐受某種程度的異常工作條件,因為即便超快速檢測算法和保護系統也無法立即發揮作用[19]。SiC MOSFET的雪崩問題已成為一個重要的專題,由于該技術尚未完全成熟,因此需要進行專門的研究[7]-[13]。

本文的目的是分析SiC MOSFET在雪崩工作條件下的魯棒性。為了驗證魯棒性分析結果,我們做了許多實驗。最后,我們介紹了器件在不同的UIS測試條件下的魯棒性。

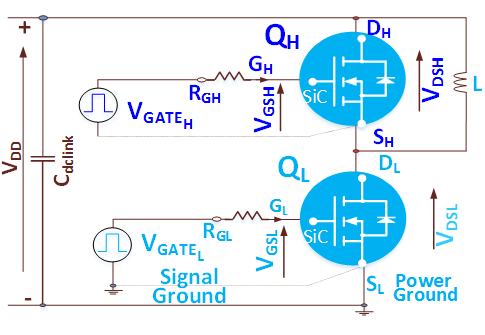

(a)

(b)

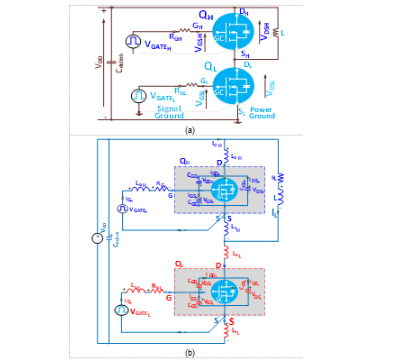

圖1:半橋轉換器橋臂:(a)簡化框圖,(b)包括主要寄生元件的等效電路。

雪崩事件

通常來說,雪崩事件只有在器件達到擊穿電壓時才會發生。在正常工作條件下,凡是設置或要求高開關頻率的應用都會發生這種現象。

以基于半橋轉換器的應用為例,讓我們詳細解釋一下雪崩現象。

圖1(a)是一個簡化的半橋轉換器電路原理圖,電路中有兩個SiC MOSFET開關管,分別用QH和QL表示,除開關管外,還有一個感性負載;圖1(b)是上面電路的等效電路圖,最重要的部分是主要寄生元件,特別是代表電源回路等效寄生電感的LDH,LSH,LDL和LSL,電源回路是指連接+ DC電路(VDD)與QH漏極,QH源極至QL漏極,QL源極至-DC電路的電源軌。此外,LGH,LGL是QH和QL的柵極-源極路徑信號回路的等效寄生電感。考慮到HiP247封裝分立器件有三或四個引線,上面的寄生電感中包含SiC MOSFET焊線和引線的寄生電感,詳細信息參見[15],[16]。同樣重要的是,還要考慮SiC MOSFET的寄生電容CGS,CDS和CGD,這些參數是漏極-源極電壓VDS的函數[21]。

不難理解在下面兩個案例的極端工作條件期間產生的電壓尖峰:

1) 有源器件導通,無源器件的體二極管關斷

2) 有源器件關斷,無源器件的體二極管導通

用1200V,25mΩ,HIP247-4L封裝的SiC MOSFET分立器件,按照圖1的方案做實驗測試,描述瞬變在什么情況下被定義為極端工作條件。為簡單起見,將QL視為有源器件,它由適合的柵極驅動器電路控制;QH是無源器件,用作續流二極管,并且通常在相關終端施加-5V的恒定負柵極-源極電壓。

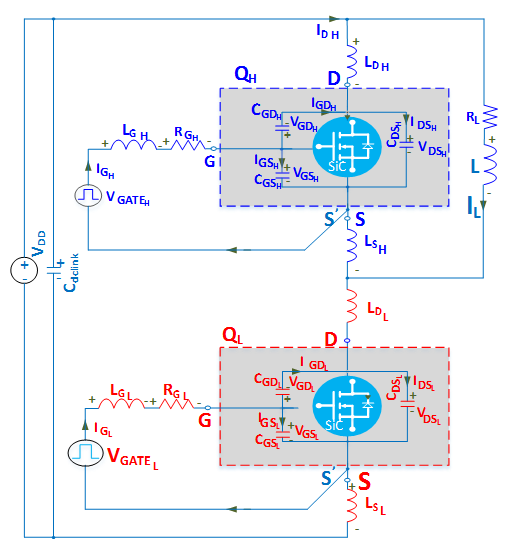

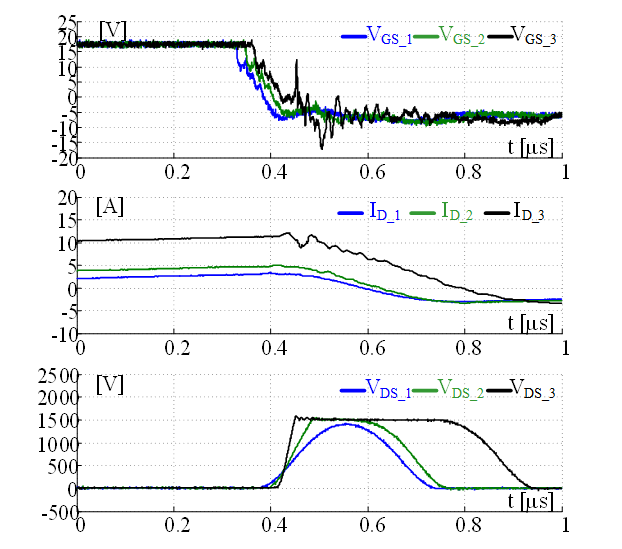

通過分析圖2的實驗結果,可以知曉案例1)的極端工作條件。

圖 2:在850V, 130A,QH 體二極管關斷時,VGS, ID 和VDS的典型波形。

本節重點介紹在QL導通時QH體二極管的“反向恢復”過程。測試條件是175°C,VDD=850V, ID=130A。SiC MOSFET的反向恢復過程是一個重要的課題,許多人都在研究這種現象。軟恢復和硬恢復模式受載流子壽命、摻雜分布、裸片面積等因素影響。從應用角度來看,反向恢復特性主要與正向電流大小ID及其變化率diD/dt和 工作溫度有關。圖2顯示了變化速率12A/ns 的ID引起的QH體二極管硬恢復特性。由于結耗盡非常快,漏極-源極電壓VDS以最快的速度上升。在diD/dt 和 dirr/dt與寄生電感的綜合作用下,尖峰電壓現象嚴重,并且在VDS波形上看到振蕩行為。另外,VGS波形出現明顯振蕩,應鉗制該電壓,以避免雜散導通。

快速恢復用于描述恢復的效果,概念定義詳見文獻。

通過優化轉換器電路板布局,將寄生電感降至非常低,可以限制在電流變化率非常高的關斷期間產生的電壓尖峰,從而最大程度地利用SiC MOSFET的性能。

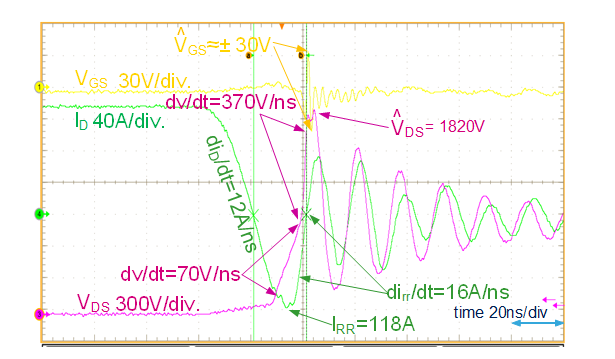

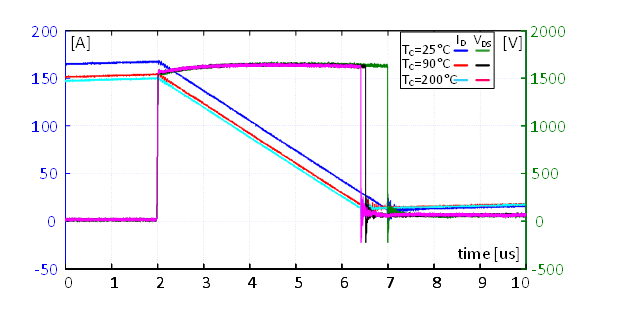

圖3的實驗測試結果解釋了案例2)的極端工作條件。圖中所示是在室溫(25°C),850V,130A條件下QL“關斷”時的相關參數波形。因為器件采用HIP247-4L封裝,3.3?的柵極電阻Rg加快了關斷瞬變,并且VDS的峰值非常高(約1550V)。

圖 3:在850V, 130A條件下關斷QL,VGS, ID, VDS 和 Poff的典型波形。

通過進一步降低Rg阻值提高關斷速度,將會引發雪崩事件,不過,在本實驗報告中沒有達到雪崩狀態。

但是,除極端工作條件外,元器件失效也會導致雪崩事件。

以前文提到的圖1半橋轉換器為例,當QH續流二極管失效,致使器件關斷時,負載電流必須在關斷瞬變期間流經互補器件QL,這個過程被稱為非鉗位感性負載開關UIS。在這個事件期間,器件必須承受某種程度的能量,直到達到QL擊穿極限值為止。

這種失效機制與臨界溫度和熱量產生有關。SiC MOSFET沒有硅基器件上發現的其它失效模式,例如,BJT閂鎖。在UIS條件下的雪崩能量測試結果被用于定義SiC MOSFET的魯棒性。

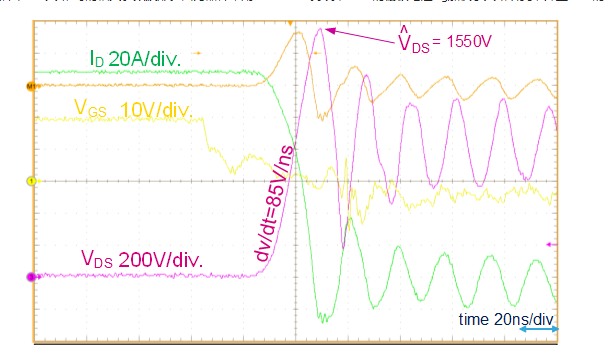

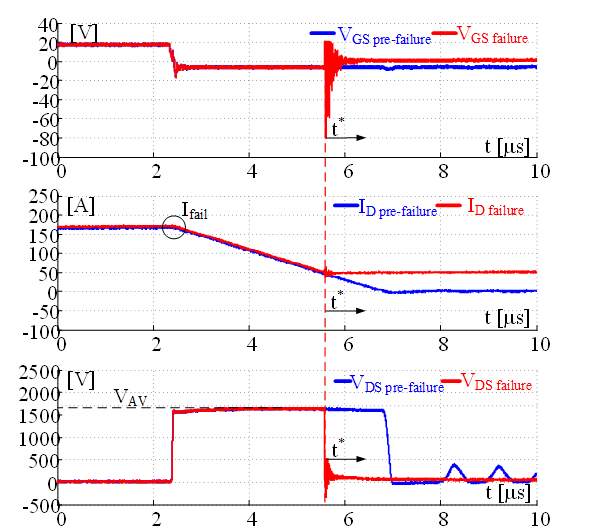

圖4(a)和圖4(b)是SiC MOSFET的UIS測試結果。這些測試是在圖1無QH的配置中做的,測試條件是VDD=100V, VGS=-5/18V, RGL=4,7?, L=50H, Tc=25°C,下一章詳細解釋這樣選擇的原因。

圖4(a)所示是前三次脈沖測試。QL正在傳導電流,在第一個脈沖時關斷,如圖中藍色的VGS,VDS和ID的波形所示,有過電壓產生,VDS略低于1500V,但器件沒有雪崩。在增加脈沖周期后,如圖中綠色波形所示,電流ID達到5A,器件開始承受雪崩電壓。再重復做一次UIS測試,如黑色波形所示,電流值變大,但由于負載電感器較小,直到電流值非常大時才達到失效能量。

(a)

(b)

圖4:UIS實驗,(a)雪崩過程開始時的波形;(b)施加最后兩個脈沖時的波形。

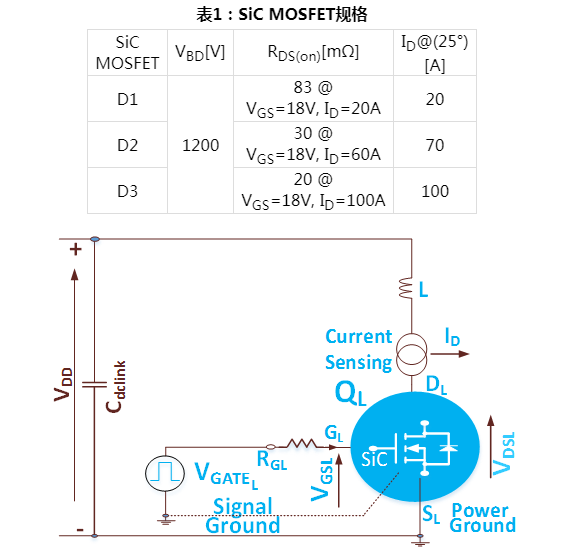

圖4(b)所示是最后一種情況的測試結果。藍色波形是在一系列單脈沖后,器件失效前倒數第二個脈沖產生的波形,從圖中可以看到,器件能夠處理關斷瞬變,耐受根據下面的雪崩能量公式(1)算出的約0,7J雪崩能量,最大漏極電流為170A,雪崩電壓平均值為1668V。

紅色波形是在施加最后一個脈沖獲得的失效波形,這時器件不再能夠耐受雪崩能量,并且在t *時刻發生失效,漏極電流開始驟然增加。

魯棒性評估和雪崩測試

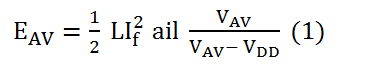

我們用三組1200V SiC MOSFE做了UIS測試,表1列出了這三組器件的主要數據。

5(a)所示是測試等效電路圖,5(b)所示是相關實驗裝置。QL是待測器件(DUT),測試目標是分析DUT的關斷特性。

(a)

(b)

圖5:UIS實驗裝置: (a)等效電路, (b) 實驗臺

設置A,B,C三種測試條件;施加周期遞增的單脈沖序列,直到待測器件失效為止。

VDD=100V, VGS=-5/18V

1, vs RGL=4,7?, 10?, 47?, at L=50uH, Tc=25°C

2, vs L=50uH, 1mH,at RGL=4,7?, Tc=25°C

3, vs Tc=25°C,90°C, 200°C, at L=50uH, RGL=4,7?

為了便于統計,從D1,D2和D3三組器件中分別抽出五個樣品,按照每種測試條件各做一次UIS實驗,測量和計算失效電流和失效能量,參見圖6,圖7和圖8。

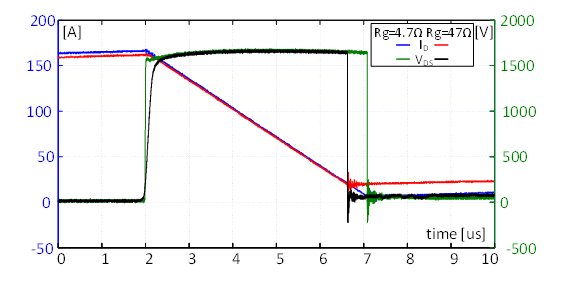

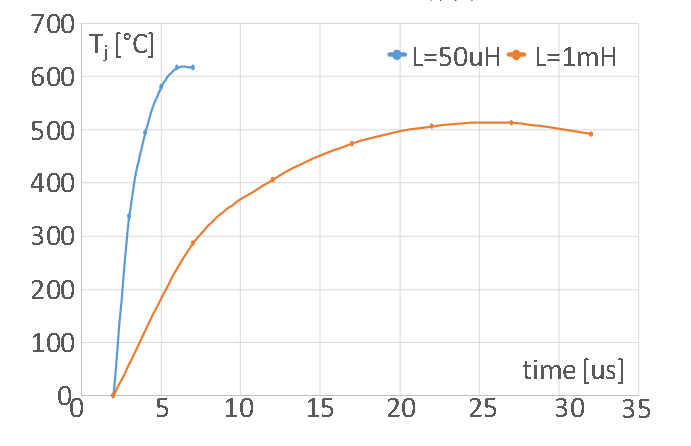

圖6(a)所示是從SiC MOSFET D3中抽出的一個典型器件,按照測試條件“A”做UIS測試的VDS 和ID失效波形。

(a)

(b)

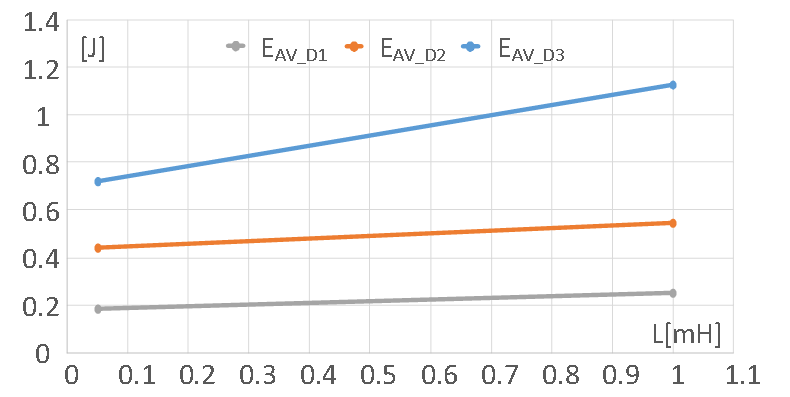

圖6:UIS對RG最終測試結果:(a) 一個D3樣品的VDS和ID典型值;(b)平均失效能量EAV。

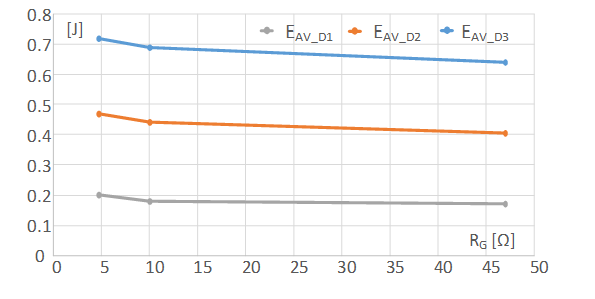

為了清楚起見,只給出了RG =4.7Ω和47Ω兩種情況的波形。我們觀察到,失效電流不受RGL的影響。圖6(b)顯示了D1,D2和D3三組的平均EAV。

注意到EAV失效能量略有降低,可忽略不計,因此,可以得出結論,在UIS測試條件下,這些SiC MOSFET的魯棒性與RG無關。

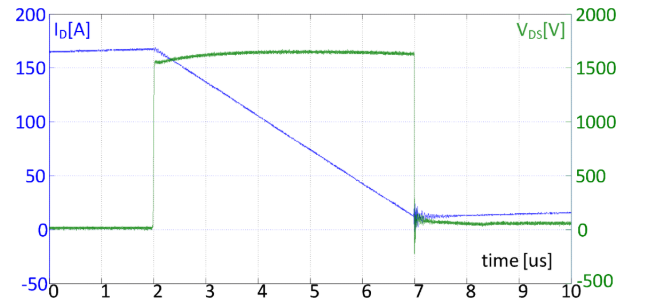

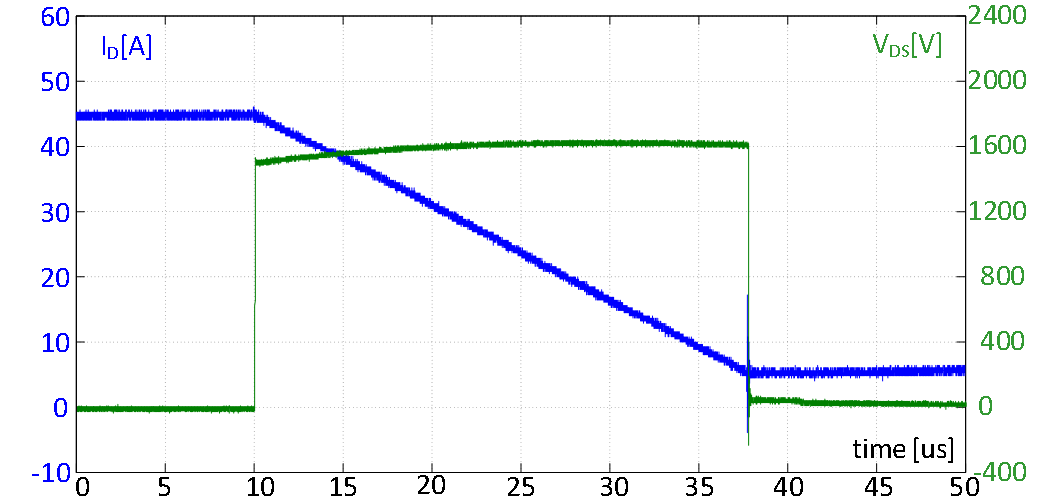

圖7(a)和(b)所示是按照測試條件B,在L=50H 和1mH時,各做一次UIS測試的失效波形,為簡單起見,只從SiC MOSFET D3中抽取一個典型樣品做實驗。

在提高負載電感后,電感器儲存的能量增加,因此,失效電流減小。

(a)

(b)

(c)

圖7:UIS對L最終測試結果 (a) 在L=50H時, D3樣品的VDS 和 ID 典型值 (b)在L=1mH時, D3樣品的VDS 和 ID 典型值 (c) 平均失效能量EAV.

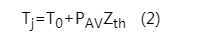

圖7(c)顯示了D1,D2和D3的平均EAV與L的關系,可以觀察到,器件D3的失效能量EAV隨著負載電感提高而顯著提高,而D1和D2的EAV則略有增加。通過分析圖8可以發現這種行為特性的原因。圖8是根據等式(2)計算出來的結溫Tj的分布圖:

其中:T0是起始溫度,PAV是平均脈沖功率,Zth是芯片封裝熱阻,本次實驗用的是不帶散熱器的TO247-3L封裝。

電感器儲存能量的大小與電感值有關,儲存能量將被施加到裸片上,轉換成熱能被耗散掉。如圖7(a)所示,低電感值會導致非常大的熱瞬變,這是因為電流在幾微秒內就達到了非常高的數值,如圖7(a)所示,因此,結溫在UIS期間上升非常快,但裸片沒有夠的時間散掉熱量。相反,在高電感值的情況下,電流值較低,如圖7(b)所示,并且裸片有足夠的時間散掉熱量,因此,溫度上升平穩。

這個實驗結果解釋了為什么被測器件D3的EAV隨負載電感提高而顯著增加的原因,另外,它的裸片面積比SiC MOSFET D1和D2都大。

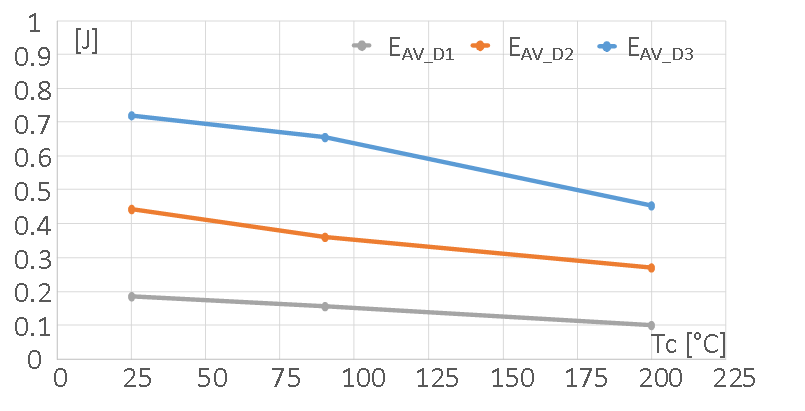

最后,在圖9中報告了測試條件C的UIS測試結果,測試條件C是封裝溫度的函數,用熱電偶測量封裝溫度數值。

圖9(a)所示是D3在Tc=25°C,90℃和200℃三個不同溫度時的VDS和ID波形。不出所料,D1,D2和D3三條線的趨勢相似,工作溫度越高,引起器件失效的EAV就越低,圖9(b)。

圖8:典型D3器件的估算結溫Tj對L曲線圖。

結論

本文探討了在SiC MOSFET應用中需要考慮的可能致使功率器件處于雪崩狀態的工作條件。為了評估SiC MOSFET的魯棒性,本文通過實驗測試評估了雪崩能量,最后還用三款特性不同的SiC MOSFET做對比測試,定義導致器件失效的最大雪崩能量。雪崩能量與芯片面積成正比,并且是柵極電阻、負載電感和外殼溫度的函數。

這種在分立器件上進行的雪崩耐量分析,引起使用電源模塊開發應用的設計人員的高度關注,因為電源模塊是由許多并聯芯片組成,這些芯片的魯棒性需要高度一致,必須進行專門的測試分析。此外,對于特定的應用,例如,汽車應用,評估雪崩條件下的魯棒性,可以考慮使用單脈沖雪崩測試和重復雪崩測試方法。這是一個重點課題,將是近期評估活動的目標。

(a)

(b)

圖9:UIS對Tc的最終測試結果;(a)D3樣品在不同的Tc時的VDS和ID典型值;(b)平均失效能量EAV 對TC曲線

參考文獻:

[1] F. Wang and Z. Zhang “Overview of Silicon Carbide Technology: Device, Converter, System, and Application,” Power Electr. And Appl. Trans on. CPSS, vol. 1, no. 1, pp. 13-32, December 2016.

[2] S. Ji, Z. Zhang, F. F. Wang “Overview of High Voltage SiC Power Semiconductor Devices: Development and Application,” CES Trans. On Elec. Machines and Systems, vol. 1, no. 3, Sept. 2017, pp.:254-264.

[3] B. Wang, J. Cai, X.Du and L. Zhou “Review of Power Semiconductor Device Reliability for Power Converters,” CPSS Trans. On Pow. Elect. and Appl. Vol.2, no.2, pp. 101-117, June2017.

[4] A. Hanif, Y. Yu, D. DeVoto and F.Khan “A Comprehensive Review Toward the State-of-the-Art in Failure and Lifetime Predictions of Power Electronic Devices,” IEEE Trans. On Pow. Elect. vol.34, no.5, pp. 4729- 4746May2019.

[5] B. Mirafzal “Survey of Fault-Tolerance Techniques for Three-Phase Voltage Source Inverters,” IEEE Trans. on Ind. Elec. Vol.61, no.10, pp. 5192-5202, Oct.2014.

[6] F. Richardeau, P. Baudesson, T. A. Meynard “Failures-Tolerance and Remedial Strategies of a PWM Multicell Inverter,” IEEE Trans. Power Elec., vol. 17, no. 6, pp 905-912, Nov.2002.

[7] A. Fayyaz, G. Romano, J. Urresti, M. Riccio, A. Castellazzi, A. Irace, and N. Wright, “A Comprehensive Study on the Avalanche Breakdown Robustness of Silicon Carbide Power MOSFETs”, Energies, vol. 10, no. 4, pp. 452-466, 2017.

[8] M. D. Kelley, B. N. Pushpakaran and Stephen B. Bayne “Single-Pulse Avalanche Mode Robustness of Commercial 1200 V/80 mΩ SiC MOSFETs,” IEEE Trans. On Pow. Elec. Vol. 32, no.8, pp. 6405-6415, Aug. 2017.

[9] I. Dchar, M. Zolkos, C. Buttay, H. Morel “Robustness of SiC MOSFET under Avalanche Conditions”, 2017 IEEE Applied Power Electronics Conference and Exposition (APEC)

[10] N. Ren, H. Hu, K. L. Wang, Z. Zuo, R. Li, K. Sheng “Investigation on Single Pulse Avalanche Failure of 900V SiC MOSFETs” Int. Symp. On Power Semic. Dev. & ICs, May 13-17, 2018.

[11] J. Wei, S. Liu, S. Li, J. Fang, T. Li, and W. Sun “Comprehensive Investigations on Degradations of Dynamic Characteristics for SiC Power MOSFETs under Repetitive Avalanche Shocks,” IEEE Trans. on Power Elec. Vol.: 34, no: 3, pp. 2748– 2757, March 2019

[12] J. Hu, O. Alatise, J. Angel Ortiz Gonzalez, R. Bonyadi, P. Alexakis, L. Ran and P. Mawby “Robustness and Balancing of Parallel-Connected Power Devices: SiC Versus CoolMOS,” IEEE Trans. On Ind. Elec. Vol. 63, no.4, pp.2092-2102 April 2016.

[13] M. Nawaz “Evaluation of SiC MOSFET power modules under unclamped inductive switching test environment”, Journal of Microelec. Reliability, vol. 63, pp. 97-103, 2016.

[14] H. Chen, D. Divan “High Speed Switching Issues of High Power Rated Silicon-Carbide Devices and the Mitigation Methods” 2015 ECCE, pp.2254-2260.

[15] M. Pulvirenti, L. Salvo, G. Scelba, A.G. Sciacca, M. Nania, G. Scarcella, M. Cacciato, “Characterization and Modeling of SiC MOSFETs Turn On in a Half Bridge Converter” 2019 IEEE En. Conv. Cong. and Expo. (ECCE2019)。

[16] M. Pulvirenti, G. Monotoro, M. Nania, R. Scollo, G. Scelba, M. Cacciato, G. Scarcella, L. Salvo “Analysis of Transient Gate-Source OverVoltages in Silicon Carbide MOSFET Power Devices” 2018 IEEE En. Conv. Cong. and Expo. (ECCE2018)。

[17] J. Mari, F. Carastro, M.-J. Kell, P. Losee, T. Zoels “Diode snappiness from a user’s perspective” 2015, 17th European Conference on Power Electronics and Applications (EPE‘15 ECCE-Europe)。

[18] R. Wu, F. Blaabjerg, H. Wang, M. Liserre, “Overview of catastrophic failures of freewheeling diodes in power electronic circuits”, Microelectronics Reliability, vol. 53, no.9-11, 2013, pp.:1788-1792.

[19] Y. Shi, R. Xie, L. Wang, Y. Shi, and H. Li, “Switching Characterization and Short-Circuit Protection of 1200V SiC MOSFET T-Type Module in PV Inverter Application”, IEEE Trans. on Ind. Electron., to be published.

[20] R. Katebi, J.He, N. Weise “An Advanced Three-Level Active Neutral-Point-Clamped Converter With Improved Fault-Tolerant Capabilities,” IEEE Trans. On Power Elect., vol. 33, no.8, pp. 6897-6909, Aug. 2018.

電子發燒友App

電子發燒友App

評論