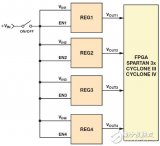

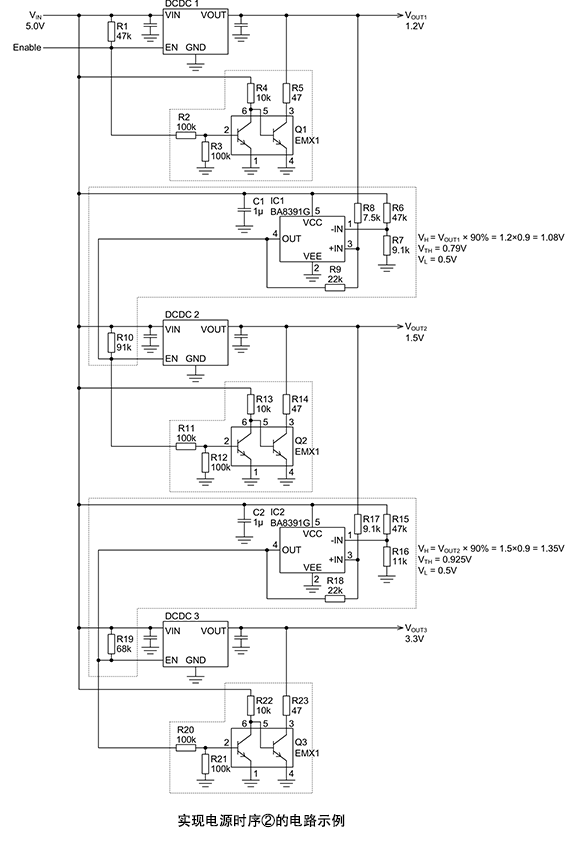

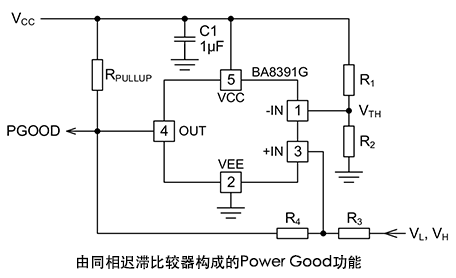

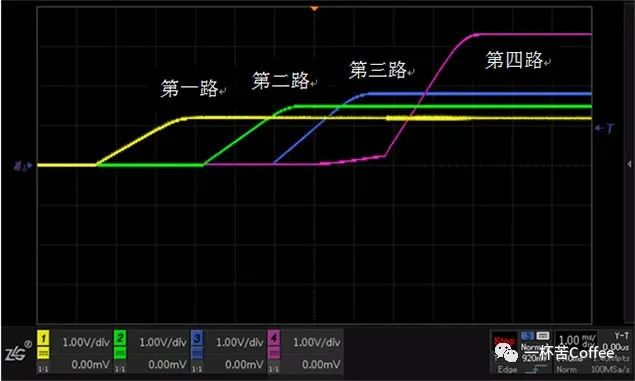

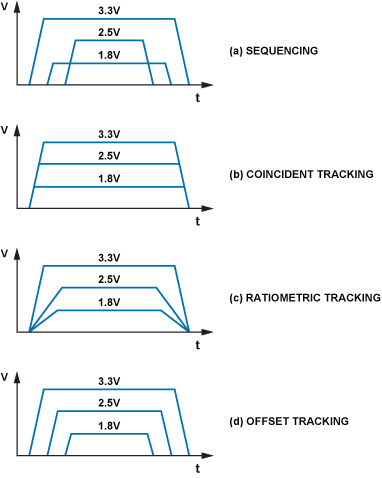

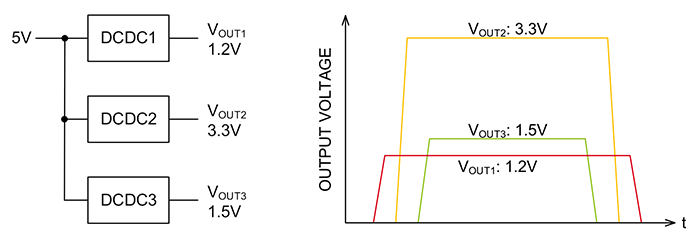

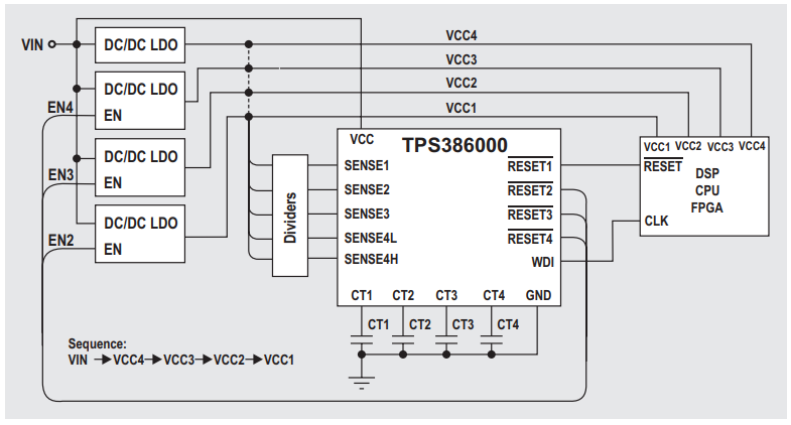

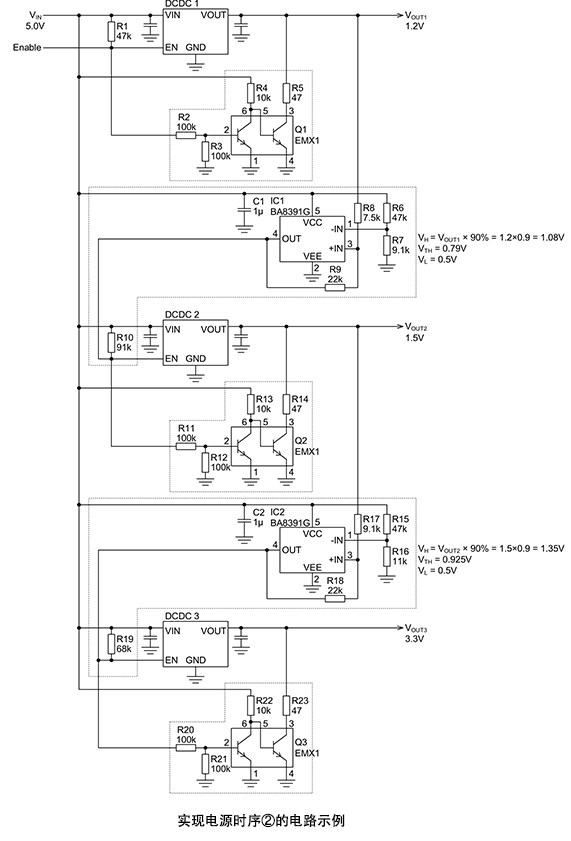

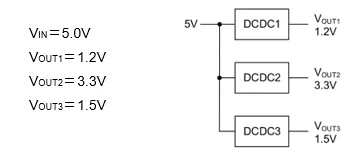

電源時(shí)序控制是微控制器、FPGA、DSP、 ADC和其他需要多個(gè)電壓軌供電的器件所必需的一項(xiàng)功能。##通過將衰減版本的調(diào)節(jié)器輸出端連接至待上電的下一個(gè)調(diào)節(jié)器使能引腳,可對(duì)多通道電源進(jìn)行時(shí)序控制。

2014-08-05 10:15:54 3878

3878

電源時(shí)序控制是微控制器、FPGA、DSP、ADC和其他需要多個(gè)電壓軌供電的器件所必需的一項(xiàng)功能。##使用電阻分壓器簡化電源時(shí)序控制

2014-08-14 10:57:25 2414

2414 在數(shù)字電路中,凡是任一時(shí)刻的穩(wěn)定輸出不僅決定于該時(shí)刻的輸入,而且還和電路原來狀態(tài)有關(guān)者都叫時(shí)序邏輯電路。時(shí)序邏輯電路結(jié)構(gòu)示意圖如圖2-41所示。時(shí)序邏輯電路的狀態(tài)是靠具有存儲(chǔ)功能的觸發(fā)器所組成的存儲(chǔ)電路來記憶和表征的。

2018-01-31 09:27:23 53523

53523

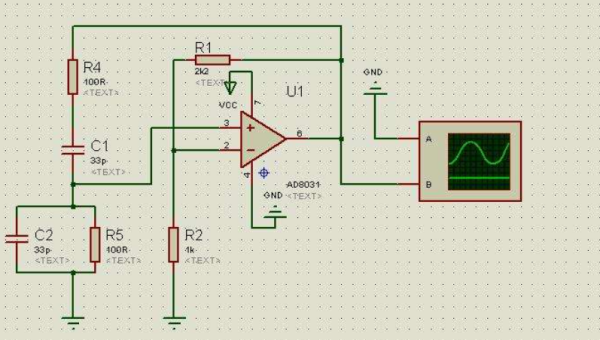

本文通過介紹多種電源時(shí)序控制的實(shí)現(xiàn),簡述應(yīng)對(duì)多領(lǐng)域應(yīng)用的電源時(shí)序控制挑戰(zhàn)ADI是如何提供易于使用解決方案的。

2022-08-01 09:10:15 552

552

同步電路設(shè)計(jì)中,時(shí)序是一個(gè)主要的考慮因素,它影響了電路的性能和功能。為了驗(yàn)證電路是否能在最壞情況下滿足時(shí)序要求,我們需要進(jìn)行靜態(tài)時(shí)序分析,即不依賴于測試向量和動(dòng)態(tài)仿真,而只根據(jù)每個(gè)邏輯門的最大延遲來檢查所有可能的時(shí)序違規(guī)路徑。

2023-06-28 09:35:37 490

490

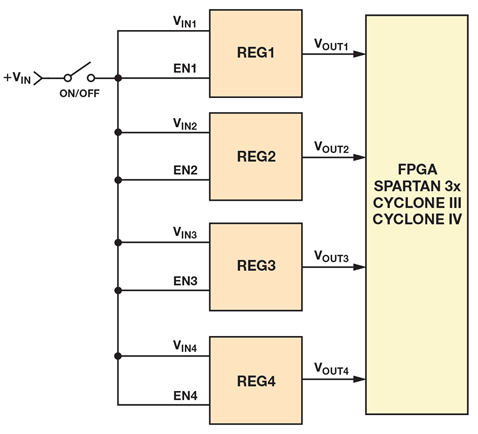

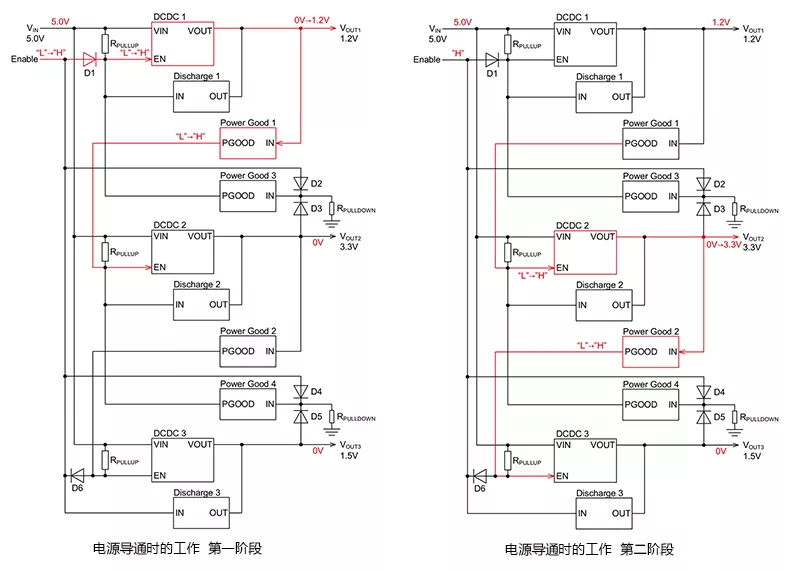

上電時(shí)序(Power-up Sequeence)是指各電源軌上電的先后關(guān)系。 與之對(duì)應(yīng)的是下電時(shí)序,但是在電路設(shè)計(jì)過程中,一般不會(huì)去考慮下電時(shí)序(特殊的場景除外)。今天,我們主要了解一下上電時(shí)序控制相關(guān)內(nèi)容。

2023-12-11 18:17:05 784

784

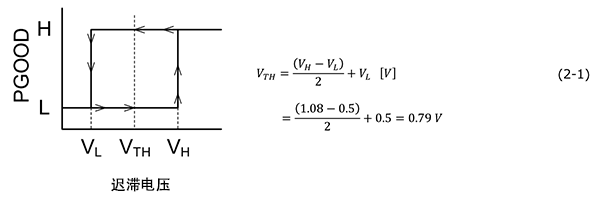

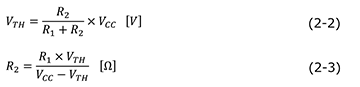

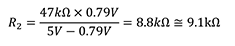

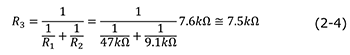

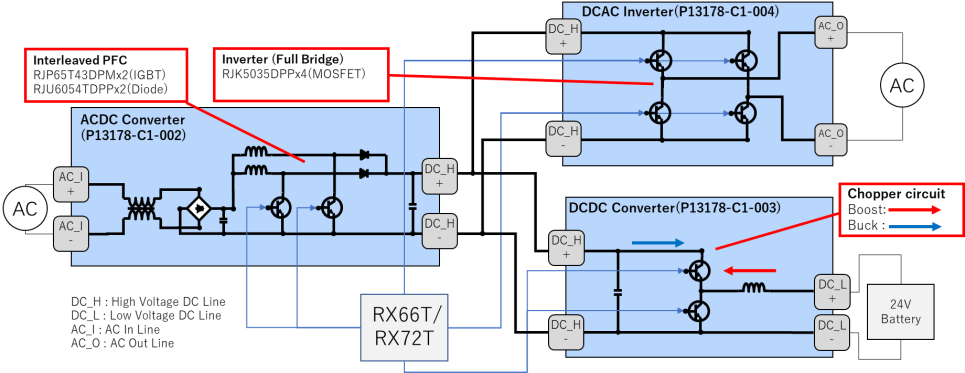

啟動(dòng)和關(guān)斷這些電源軌。此過程稱為電源時(shí)序控制或電源定序,目前有許多解決方案可以有效實(shí)現(xiàn)定序。對(duì)于需要電壓定序的復(fù)雜器件,其內(nèi)核和模擬模塊的電壓軌可能需要在數(shù)字 I/O 電壓軌之前上電。有些設(shè)計(jì)可能會(huì)要求...

2021-11-12 06:01:50

的外部柵壓控制可以實(shí)現(xiàn)這些功能。舉個(gè)栗子:外部偏置放大器的時(shí)序和控制要求HMC1131是一款砷化鎵(GaAs)、pHEMT單片微波集成電路(MMIC)中功率放大器。工作頻率范圍為24 GHz至35 GHz

2017-11-22 09:28:58

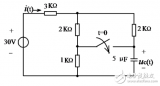

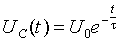

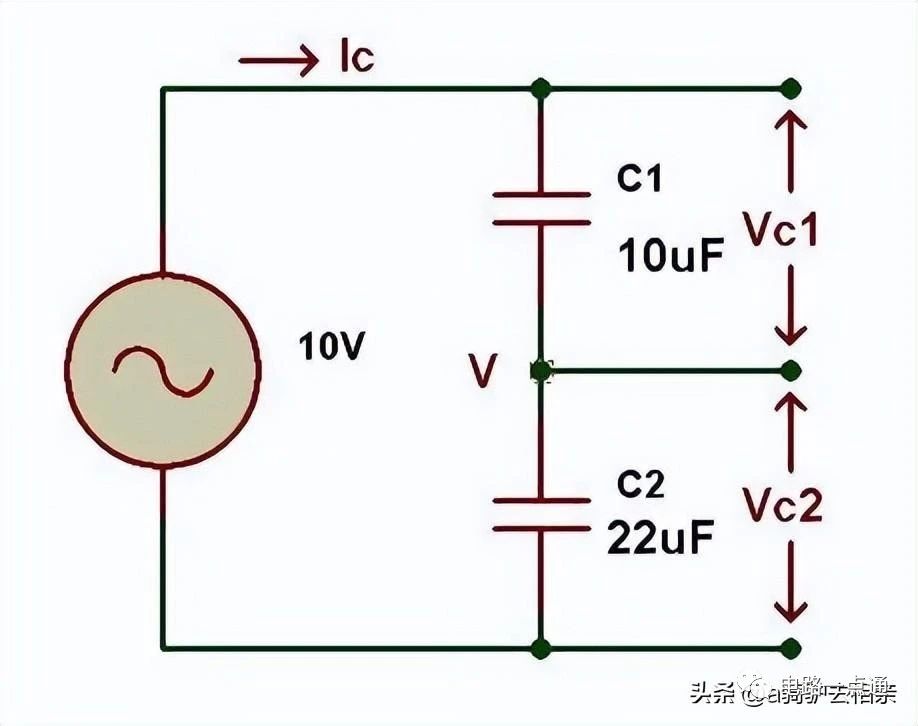

初始值iL(0)按指數(shù)規(guī)律單調(diào)的衰減到零,其時(shí)間常數(shù) τ =L/RRC電路時(shí)間常數(shù)的計(jì)算假設(shè)有電源Vu通過電阻R給電容C充電,V0為電容上的初始電壓值,Vu為電容充滿電后的電壓值,Vt為任意時(shí)刻t時(shí)電容

2019-04-08 09:00:00

各位大神,我手機(jī)想安裝個(gè)計(jì)算軟件,可以計(jì)算RC時(shí)間常數(shù)的,手機(jī)軟件圖標(biāo)是二極管符號(hào)的,有誰知道他叫什么名字么?或者還有其他的軟件告訴一下,謝謝

2019-04-17 10:10:58

稱為電源時(shí)序控制或電源定序,目前有許多解決方案可以有效實(shí)現(xiàn)定序。對(duì)于需要電壓定序的復(fù)雜器件,其內(nèi)核和模擬模塊的電壓軌可能需要在數(shù)字 I/O 電壓軌之前上電。有些設(shè)計(jì)可能會(huì)要求不同的順序,但是

2019-07-30 10:43:06

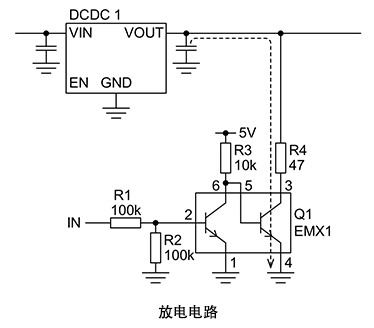

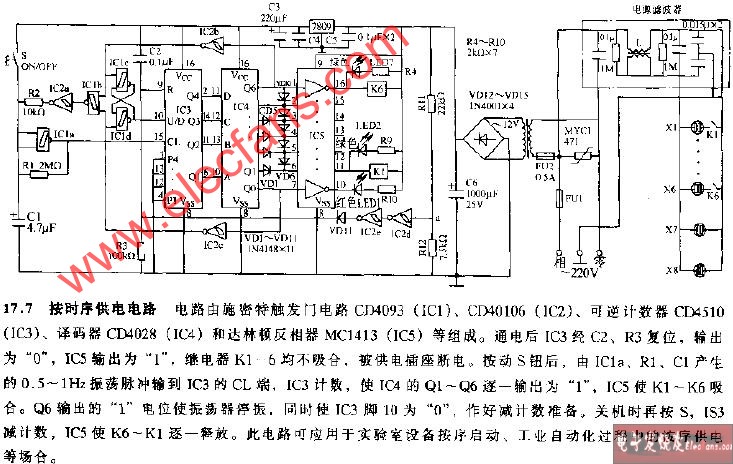

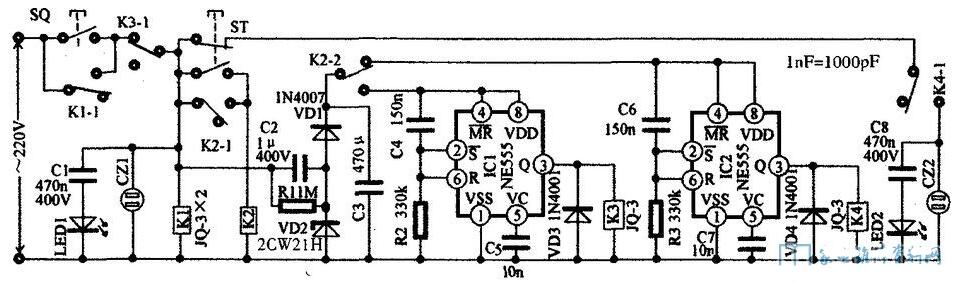

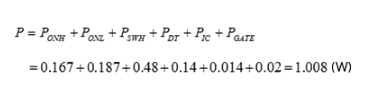

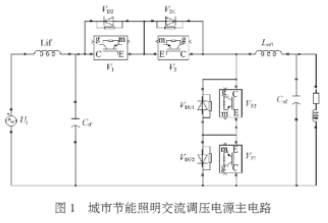

用電腦的朋友都知道,電腦設(shè)備的開關(guān)機(jī)操作應(yīng)遵循先開外設(shè)后開主機(jī)、先關(guān)主機(jī)后關(guān)外設(shè)的順序。本文介紹專為電腦設(shè)計(jì)的時(shí)序控制電源插座, 稍加改動(dòng)也可以用到其他的需要時(shí)序控制的電路中去。

2021-04-22 07:18:24

為什么FPGA可以用來實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

2023-04-23 11:53:26

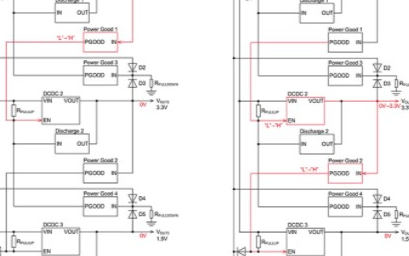

進(jìn)行電源時(shí)序控制的優(yōu)缺點(diǎn),同時(shí)介紹利用ADP5134內(nèi)部精密使能引腳實(shí)現(xiàn)時(shí)序控制的一種簡單而有效的方法ADP5134內(nèi)置2個(gè)1.2-A 降壓調(diào)節(jié)器與2個(gè)300-mA LDO。同時(shí),本文還列出一系列IC

2018-09-30 16:01:35

我想計(jì)算LM2576外圍電路電感的值,好像要用到電壓·微秒常數(shù)和負(fù)載電流曲線,電壓·微秒常數(shù)和負(fù)載電流曲線是什么,在哪可以得到?買LM2576就有配的嗎?

2013-07-17 19:51:25

開關(guān)電源001–時(shí)間常數(shù)我們可以看到這是一個(gè)普通的RC串聯(lián)電路,但是我們可以以此退出對(duì)電容和電感的時(shí)間常數(shù)的表達(dá)。時(shí)間常數(shù)是一個(gè)很重要的變量,在之后開關(guān)電源的很多地方有用,如RC串聯(lián)無損電流檢測電路

2021-12-31 06:07:01

本帖最后由 一只耳朵怪 于 2018-5-21 11:23 編輯

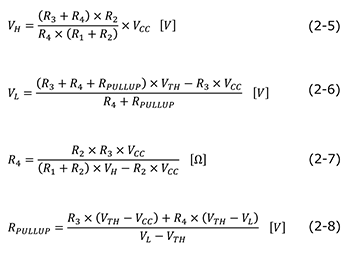

想用labview進(jìn)行如圖所示的公式計(jì)算,我找到了多項(xiàng)式插件,但是沒研究明白怎么實(shí)現(xiàn)上面是常數(shù)下面是多項(xiàng)式這種形式的多項(xiàng)式的運(yùn)算,不知道能否請各位大佬指點(diǎn)一二,最好能給出相應(yīng)的程序,圖中除了x之外都是變量。

2018-05-21 11:03:27

RT:求助一下關(guān)于標(biāo)準(zhǔn)電能脈沖常數(shù)計(jì)算公式,謝謝。

2016-09-18 20:15:12

RT:請教一下關(guān)于標(biāo)準(zhǔn)電能脈沖常數(shù)的計(jì)算公式

2016-09-18 20:07:43

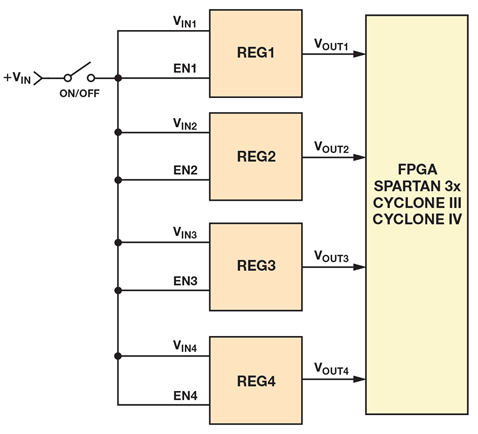

要求,但為了實(shí)現(xiàn)最小浪涌電流電平并遵循連接至FPGA 的電路時(shí)序控制要求,供電軌應(yīng)當(dāng)按以下序列上電VCC_INT → VCC_AUX→ VCCO。請注意:有些應(yīng)用要求采用特定序列,因此,務(wù)必閱讀數(shù)據(jù)手冊的電源要求部分。

2019-07-03 08:15:19

對(duì)器件進(jìn)行配置。這樣有助于降低電源時(shí)序控制要求,但為了實(shí)現(xiàn)最小浪涌電流電平并遵循連接至 FPGA 的電路時(shí)序控制要求,供電軌應(yīng)當(dāng)按以下序列上電:VCC_INT a VCC_AUX a VCCO。請注意

2018-10-23 14:30:34

高速電路信號(hào)完整性分析與設(shè)計(jì)—時(shí)序計(jì)算引入:在數(shù)字電路中,從一個(gè)芯片發(fā)信息A到另一個(gè)芯片變成信息B,那么這個(gè)數(shù)字系統(tǒng)失敗;如何保證信息不變?關(guān)鍵點(diǎn),就是在傳輸過程的任意點(diǎn)都保持時(shí)序的正確性。時(shí)序概念

2009-09-12 10:28:42

高速電路的時(shí)序分析電路中,數(shù)據(jù)的傳輸一般都是在時(shí)鐘對(duì)數(shù)據(jù)信號(hào)進(jìn)行有序的收發(fā)控制下進(jìn)行的。芯片只能按規(guī)定的時(shí)序發(fā)送和接收數(shù)據(jù),過長的信號(hào)延遲或信號(hào)延時(shí)匹配不當(dāng)都會(huì)影響芯片的建立和保持時(shí)間,導(dǎo)致芯片無法

2012-08-02 22:26:06

時(shí)序邏輯電路的輸出不但和當(dāng)前輸入有關(guān),還與系統(tǒng)的原先狀態(tài)有關(guān),即時(shí)序電路的當(dāng)前輸出由輸入變量與電路原先的狀態(tài)共同決定。為達(dá)到這一目的,時(shí)序邏輯電路從某一狀態(tài)

2009-03-18 22:13:04 71

71 印刷電路板結(jié)構(gòu)中的等效介電常數(shù)和快速電容提取:摘要:出了用于印刷電路板,平多層介質(zhì)結(jié)構(gòu)的等效介電常數(shù)的概念,使在結(jié)構(gòu)中電容提取的計(jì)算量減少到自由空間中電容提取的量級(jí),

2009-05-16 21:39:39 30

30 同步時(shí)序邏輯電路:本章系統(tǒng)的講授同步時(shí)序邏輯電路的工作原理、分析方法和設(shè)計(jì)方法。從同步時(shí)序邏輯電路模型與描述方法開始,介紹同步時(shí)序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 異步時(shí)序邏輯電路:本章主要從同步時(shí)序邏輯電路與異步時(shí)序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時(shí)序邏輯電路的電路結(jié)構(gòu)、工作原理、分析方法和設(shè)計(jì)方法。

2009-09-01 09:12:34 0

0 高速電路信號(hào)完整性分析與設(shè)計(jì)—時(shí)序計(jì)算:基本概念引入:在數(shù)字電路中,從一個(gè)芯片發(fā)信息A到另一個(gè)芯片變成信息B,那么這個(gè)數(shù)字系統(tǒng)失敗;如何保證信息不變?關(guān)鍵點(diǎn),就

2009-10-06 11:08:19 0

0 時(shí)序計(jì)算和Cadence 仿真結(jié)果的運(yùn)用中興通訊康訊研究所 EDA 設(shè)計(jì)部 余昌盛 劉忠亮摘要:本文通過對(duì)源同步時(shí)序公式的推導(dǎo),結(jié)合對(duì)SPECCTRAQuest 時(shí)序仿真方法的分析,推導(dǎo)出了使

2009-12-21 09:05:39 172

172 采用三相交流電源的低功耗絕熱時(shí)序電路

研究采用三相交流電源的絕熱時(shí)序電路。首先介紹了采用三相交流電源的雙傳輸門絕熱電路并分析其工作原理, 在此基

2010-02-22 15:41:56 15

15 摘要:針對(duì)同步時(shí)序電路的初始化問題,提出了一種新的實(shí)現(xiàn)方法。當(dāng)時(shí)序電路中有未確定狀態(tài)的觸發(fā)器時(shí),就不能順利完成該電路的測試生成,因此初始化是時(shí)序電路測試生成中

2010-05-13 09:36:52 6

6 提要:本文試圖避開繁雜的高等數(shù)學(xué)推導(dǎo)和運(yùn)算,對(duì)RC電路的時(shí)間常數(shù)T的物理意義進(jìn)行描述;找出常見較復(fù)雜Rc電路T的簡單計(jì)算方法,對(duì)相同形式的RC電路,由于元件參數(shù)配置及使用

2010-05-30 09:20:47 110

110 本文介紹將量子進(jìn)化算法應(yīng)用在時(shí)序電路測試生成的研究結(jié)果。結(jié)合時(shí)序電路的特點(diǎn),本文將量子計(jì)算中的量子位和疊加態(tài)的概念引入傳統(tǒng)的測試生成算法中,建立了時(shí)序電路的量

2010-08-03 15:29:01 0

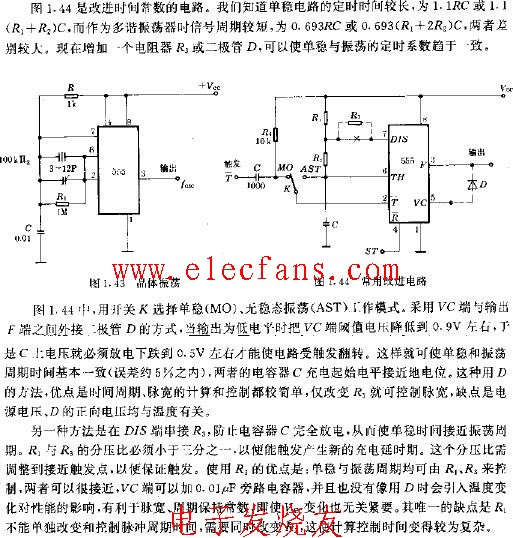

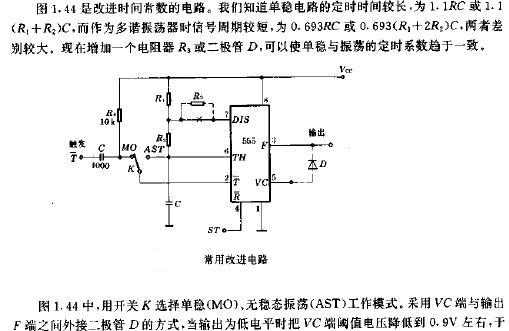

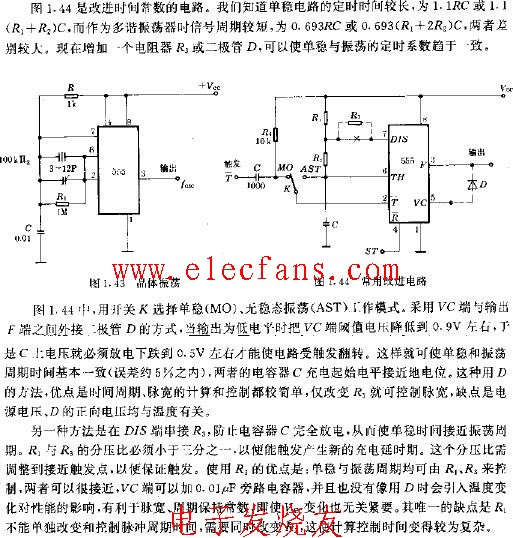

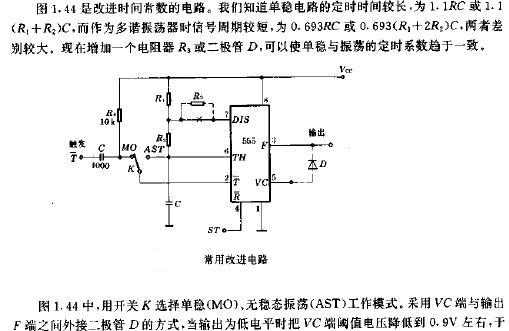

0 555常用改進(jìn)時(shí)間常數(shù)的電路:是改進(jìn)時(shí)間常數(shù)的電路。我們知道單穩(wěn)電路的定時(shí)間較長,為1。1RC或1。1(R1+R2)C而作為多諧振蕩器時(shí)信號(hào)周期較短,為0。693RC或0.693(R1+

2008-05-19 22:47:21 1239

1239

常用改進(jìn)時(shí)間常數(shù)的電路

常用改進(jìn)時(shí)間常數(shù)的電路

2009-04-08 18:13:07 917

917

如何計(jì)算時(shí)間常數(shù)RC

時(shí)間常數(shù)在電子線路中,特別是在脈沖電路中,是一個(gè)很重要的

2009-08-14 08:57:32 15159

15159 同步時(shí)序電路

4.2.1 同步時(shí)序電路的結(jié)構(gòu)和代數(shù)法描述

2010-01-12 13:31:55 4671

4671

Verilog HDL語言實(shí)現(xiàn)時(shí)序邏輯電路

在Verilog HDL語言中,時(shí)序邏輯電路使用always語句塊來實(shí)現(xiàn)。例如,實(shí)現(xiàn)一個(gè)帶有異步復(fù)位信號(hào)的D觸發(fā)器

2010-02-08 11:46:43 4467

4467 本文通過對(duì)源同步時(shí)序公式的推導(dǎo),結(jié)合對(duì)SPECCTRAQuest 時(shí)序仿真方法的分析,推導(dǎo)出了使用SPECCTRAQuest 進(jìn)行時(shí)序仿真時(shí)的計(jì)算公式,并對(duì)公式的使用進(jìn)行了說明。 通常我們在時(shí)序仿真中

2011-07-12 10:05:52 97

97 現(xiàn)今,電子系統(tǒng)往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統(tǒng)中,尤其如此。為實(shí)現(xiàn)可靠、可重復(fù)的操作,必須監(jiān)控各電源電壓的開關(guān)時(shí)序、上升和

2012-04-20 11:53:06 2615

2615

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論