定義:

電源完整性(Power integrity)簡(jiǎn)稱PI,是確認(rèn)電源來源及目的端的電壓及電流是否符合需求。

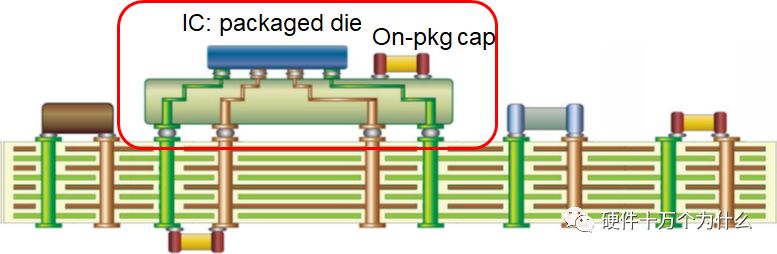

電源完整性在現(xiàn)今的電子產(chǎn)品中相當(dāng)重要。有幾個(gè)有關(guān)電源完整性的層面:芯片層面、芯片封裝層面、電路板層面及系統(tǒng)層面。在電路板層面的電源完整性要達(dá)到以下三個(gè)需求:

1、使芯片引腳的電壓噪聲+電壓紋波比規(guī)格要求要小一些(例如芯片電源管腳的輸入電壓要求1V之間的誤差小于+/-50 mV)

2、控制接地反彈(地彈)(同步切換噪聲SSN、同步切換輸出SSO)

3、降低電磁干擾(EMI)并且維持電磁兼容性(EMC):電源分布網(wǎng)絡(luò)(PDN)是電路板上最大型的導(dǎo)體,因此也是最容易發(fā)射及接收噪聲的天線。

名詞解釋:

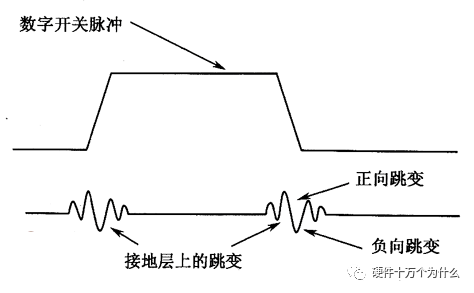

a、“地彈”,是指芯片內(nèi)部“地”電平相對(duì)于電路板“地”電平的變化現(xiàn)象。以電路板“地”為參考,就像是芯片內(nèi)部的“地”電平不斷的跳動(dòng),因此形象的稱之為地彈(ground bounce)。

當(dāng)器件輸出端由一個(gè)狀態(tài)跳變到另一個(gè)狀態(tài)時(shí),地彈現(xiàn)象會(huì)導(dǎo)致器件邏輯輸入端產(chǎn)生毛刺。對(duì)于任何形式封裝的芯片,其引腳必會(huì)存在電感電容等寄生參數(shù),而地彈主要是由于GND引腳上的阻抗引起的。集成電路的規(guī)模越來越大,開關(guān)速度不斷提高,地彈噪聲如果控制不好就會(huì)影響電路的功能,因此有必要深入理解地彈的概念并研究它的規(guī)律。

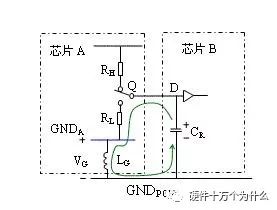

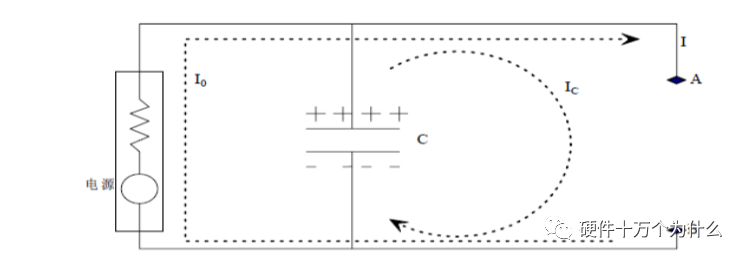

我們可以用下圖來直觀的解釋一下。圖中開關(guān)Q的不同位置代表了輸出的“0”“1”兩種狀態(tài)。假定由于電路狀態(tài)轉(zhuǎn)換,開關(guān)Q接通RL低電平,負(fù)載電容對(duì)地放電,隨著負(fù)載電容電壓下降,它積累的電荷流向地,在接地回路上形成一個(gè)大的電流浪涌。隨著放電電流建立然后衰減,這一電流變化作用于接地引腳的電感LG,這樣在芯片外的電路板“地”與芯片內(nèi)的地之間,會(huì)形成一定的電壓差,如圖中VG。這種由于輸出轉(zhuǎn)換引起的芯片內(nèi)部參考地電位漂移就是地彈。

芯片A的輸出變化,產(chǎn)生地彈。這對(duì)芯片A的輸入邏輯是有影響的。接收邏輯把輸入電壓和芯片內(nèi)部的地電壓差分比較確定輸入,因此從接收邏輯來看就像輸入信號(hào)本身疊加了一個(gè)與地彈噪聲相同的噪聲。

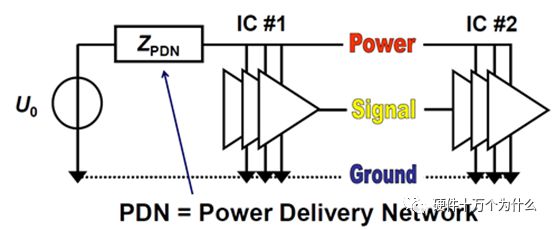

b、PDN

電路板設(shè)計(jì)中,都有電源分配網(wǎng)絡(luò)系統(tǒng)。電源分配網(wǎng)絡(luò)系統(tǒng)的作用就是給系統(tǒng)內(nèi)所有器件或芯片提供足夠的電源,并滿足系統(tǒng)對(duì)電源穩(wěn)定性的要求。

我們看到電源、GND網(wǎng)絡(luò),其實(shí)分布著阻抗。

電源噪聲余量計(jì)算:

1、芯片的datasheet會(huì)給一個(gè)規(guī)范值,通常是5%;要考慮到穩(wěn)壓芯片直流輸出誤差,一般是+/_2.5%,因此電源噪聲峰值幅度不超過+/_2.5%。

2、如芯片的工作電壓范圍是3.13~3.47,穩(wěn)壓芯片標(biāo)出輸出電壓是3.3V,安裝在電路板后的輸出電壓是3.36V。容許的電壓的變化范圍是3.47-3.36=110mv。穩(wěn)壓芯片輸出精度是+/_1%,及3.36* +/_1%=+/_33.6mv。電源噪聲余量為110-33.6=76.4mv。

計(jì)算電源噪聲要注意五點(diǎn)

(1)穩(wěn)壓芯片的輸出的精確值是多少。

(2)工作環(huán)境的是否是穩(wěn)壓芯片所推薦的環(huán)境。

(3)負(fù)載情況是怎么樣,這對(duì)穩(wěn)壓芯片輸出也有影響。

(4)電源噪聲最終會(huì)影響到信號(hào)質(zhì)量。而信號(hào)上的噪聲來源不僅僅是電源噪聲,反射竄擾等信號(hào)完整性問題也會(huì)在信號(hào)上疊加,因此不能把所有噪聲余量留給電源系統(tǒng)。

(5)不同的電壓等級(jí)對(duì)電源噪聲要求也不樣,電壓越小噪聲余量越小。模擬電路對(duì)電源要求更高。

電源噪聲來源

(1)穩(wěn)壓芯片輸出的電壓不是恒定的,會(huì)有一定的紋波。

(2)穩(wěn)壓電源無法實(shí)時(shí)響應(yīng)負(fù)載對(duì)于電流需求的快速變化。穩(wěn)壓電源響應(yīng)的頻率一般在200Khz以內(nèi),能做正確的響應(yīng),超過了這個(gè)頻率則在電源的輸出短引腳處出現(xiàn)電壓跌落。

(3)負(fù)載瞬態(tài)電流在電源路徑阻抗和地路徑阻抗產(chǎn)生的壓降。

(4)外部的干擾。

去耦電容

?電容去耦是解決電源噪聲的主要方法。

這種方法對(duì)提高瞬態(tài)電流的響應(yīng)速度,降低電源分配系統(tǒng)的阻抗都非常有效。

一種解釋是儲(chǔ)能,當(dāng)負(fù)載發(fā)生瞬態(tài)電流變化時(shí),電源不能即時(shí)滿足負(fù)載的瞬態(tài)電流的要求,可根據(jù)公式I=Cdv/dt,此時(shí)電容二端存在電壓的變化,電容開始放電,及時(shí)提供負(fù)載電流。

一種解釋是阻抗,把負(fù)載芯片拿掉,從AB二點(diǎn)向左看去,穩(wěn)壓電源及電容可以看出一個(gè)復(fù)合電源系統(tǒng),不能AB二點(diǎn)負(fù)載電流如何變化,都保證AB二點(diǎn)電壓穩(wěn)定及AB二點(diǎn)電壓變化很小,可根據(jù)公式△V=Z *△I。

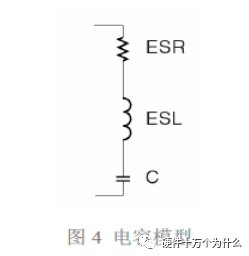

實(shí)際的電容存在寄生電感與等效串聯(lián)電阻。

R=esr +1/j2πfc +j2πfl?等效竄聯(lián)電感無法消除,只要存在引線就會(huì)有寄生電感。等效串聯(lián)電阻也是存在的,因?yàn)橹谱麟娙莸牟牧喜皇浅瑢?dǎo)體。當(dāng)頻率很低時(shí),j2πfl遠(yuǎn)小于1/j2πfc,整個(gè)電容器呈現(xiàn)電容性;當(dāng)頻率很高時(shí), j2πfl大于1/j2πfc,整個(gè)電容器呈現(xiàn)電感性;當(dāng)j2πfl等于1/j2πfc,整個(gè)電容器呈現(xiàn)純電阻特性,阻抗最小,其稱為諧振點(diǎn)。

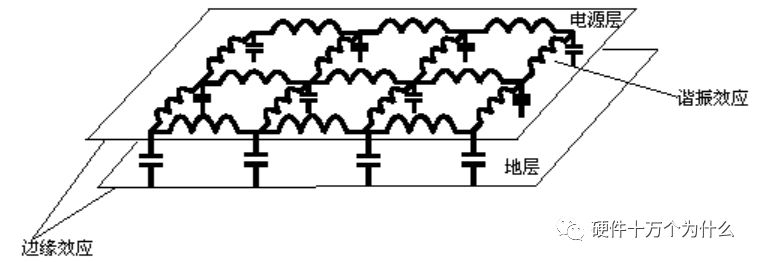

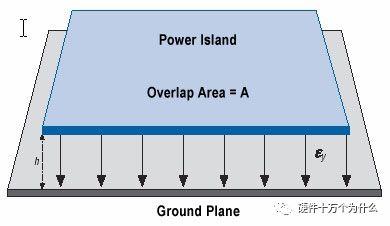

圖1.并聯(lián)平面電容

當(dāng)電源平面與地平面接近時(shí),會(huì)出現(xiàn)電場(chǎng)。圖1中上面的區(qū)域顯示了電源島,即電源平面,下面的區(qū)域顯示了地平面,箭頭表示電場(chǎng)電力線。這一電場(chǎng)提高了電容,由下面的公式表示其大小:

平面電容

對(duì)于高頻,使用分立電容進(jìn)行去耦合的效率不高。對(duì)于這些頻率,使用電源平面電容對(duì)噪聲去耦合。如圖1所示,您可以看一下標(biāo)準(zhǔn)的并聯(lián)平行極板電容,理解平面電容的概念。

C=(εοεrA)/h

其中:

εο = 自由空間的介電常數(shù)

εr = 所使用電介質(zhì)的相對(duì)介電常數(shù)

A = 重疊區(qū)域

h = 單獨(dú)的平面

電源島的兩側(cè)如果都有地平面,那么,需要計(jì)算每一側(cè)的電容,加起來以確定總電容。

平面電容是高頻時(shí)去耦合的主要方法,因此,這是所有高速設(shè)計(jì)都要采用的。在高頻,分立電容的作用并不明顯。

例如,考慮下面。

實(shí)例:確定FR-4絕緣材料疊層(εr = 4.5)1平方英寸面積的并聯(lián)平行極板電容,隔開了4 mils。

解決方案:

h = 4mils = 1.016 * 10-4 m

εο = 自由空間的介電常數(shù) = 8.85 * 10-12 F/m

A = 1平方英寸 = 6.4516 * 10-4 m2

εr = 4.5

把這些數(shù)值應(yīng)用到上面的電容公式中,得到C = 253 pF。因此,典型FR-4電路板疊層間隔4 mils,每平方英寸的電容大約是253 pF。數(shù)值與間隔距離成線性反比,與面積成線性正比。Altera在多種電路板上成功應(yīng)用了平面電容。

減小雜散電感

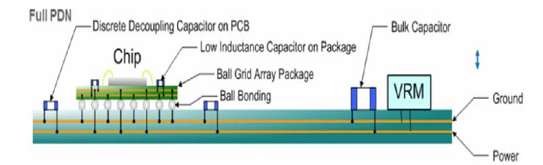

電源分配系統(tǒng)(PDS)的目的是為每一器件的電源和地焊盤提供并維持所要求的目標(biāo)恒定電壓。為能夠高效的實(shí)現(xiàn)這一目標(biāo),體電容和去耦合電容(Decaps),以及電源和地平面夾層結(jié)構(gòu)(平面電容)。在各種瞬變的負(fù)載條件下,這些元器件能否有效的幫助維持恒定電壓主要取決于它們相關(guān)的雜散電感。

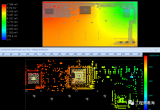

目標(biāo)阻抗

目標(biāo)阻抗是電源系統(tǒng)的瞬態(tài)阻抗,對(duì)快速變化的電流的表現(xiàn)出來的一種特性阻抗。目標(biāo)阻抗和一定寬度的頻率有關(guān),在感興趣的頻率范圍內(nèi),電源阻抗都不能超過這個(gè)值。

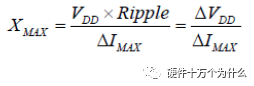

目標(biāo)阻抗公式

去耦的電源電壓,ripple為允許的電壓波動(dòng)范圍,典型值為2.5%,△Imax為負(fù)載芯片最大瞬態(tài)電流變化量。

選擇電容

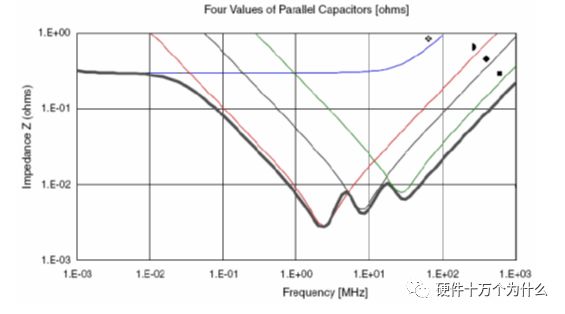

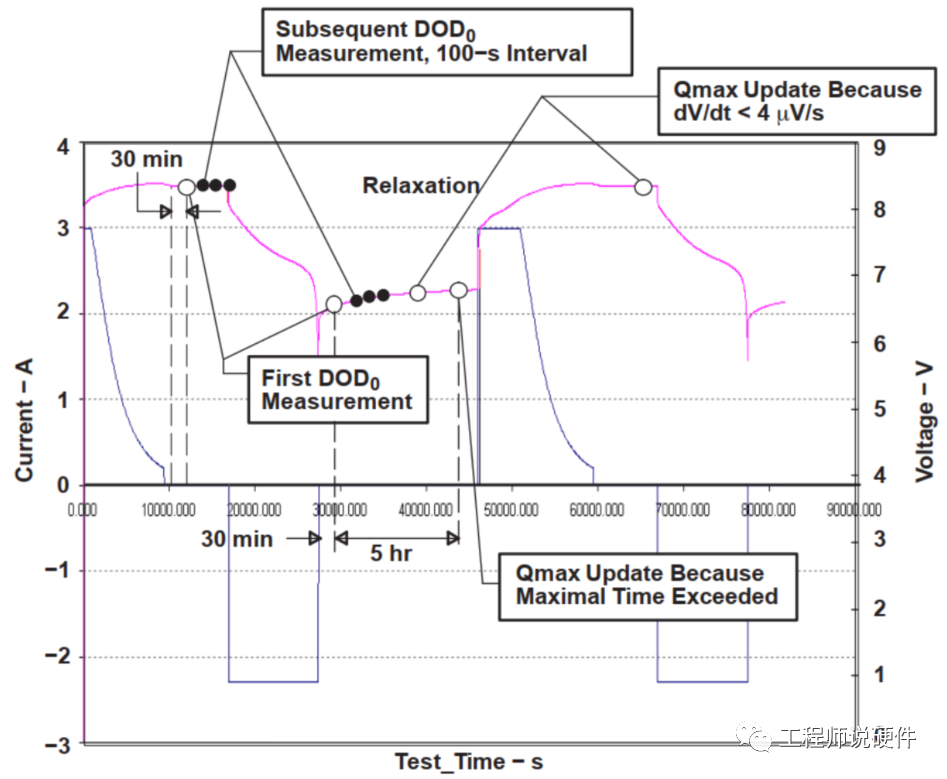

用一個(gè)電容組合的例子。這個(gè)組合使用的電容為:2個(gè)680uf鉭電容,7個(gè)2.2uf陶瓷電容(0805封裝),13個(gè)0.22uf陶瓷電容(0603封裝),26個(gè)0.022uf陶瓷電容(0402)。圖中上部平坦的曲線是680uf電容的阻抗曲線,其它三個(gè)容值的曲線為為圖中三個(gè)V字曲線,從左到右2.2uf →0.22uf → 0.022uf。總的阻抗曲線為底部粗包路線。

這個(gè)組合實(shí)現(xiàn)了在500K到150M范圍內(nèi)保持阻抗在33毫歐以下,到500M處,阻抗上升到110毫歐,從圖中看反諧振點(diǎn)控制的很低。

審核編輯:湯梓紅

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論