引言:面向收發器 (SERDES) FPGA 的PDN設計對電源有嚴格的要求,需要干凈的電壓源。雖然低功耗應用中通常采用低泄漏 (LDO) 線性穩壓器,但這一方法必須仔細的隔離電壓源。電路板設計人員在這些應用中必須全面考慮電壓源隔離和電壓源共享問題。隔離度較高時,會增加穩壓器的數量,而太多的共享則會影響性能。如果 PDN 穩壓不夠,那么,收發器的性能會受到很大影響。因此,正確的選擇穩壓器和電源配置對于實現最佳收發器性能非常重要。

在很多 PDN 設計中,創新的開關穩壓器相對于線性穩壓器有很大的優勢。而且,FPGA收發器技術不斷發展,在 FPGA 中實現穩壓器,從而不再需要使用外部穩壓器。本文檔在以下方面為穩壓器選擇和實現提供指南:

線性穩壓器和開關穩壓器比較

FPGA 電源隔離指南

推薦的單片封裝解決方案

PDN 性能實例

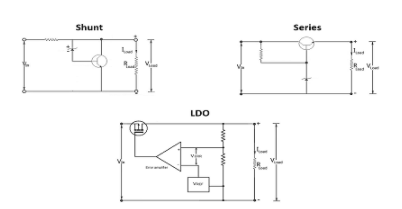

1.線性穩壓器和開關穩壓器比較

傳統上,電路板設計人員在低電流、低噪聲和電路板空間有限的情況下使用線性穩壓器,而使用開關穩壓器來提高功率,增強效率。這種指導原則在很多情況下是適用的,但是,隨著開關穩壓器設計的進步,現在它在很多應用中可以替換線性穩壓器。這一部分闡述線性穩壓器和開關穩壓器之間的不同,提供每一類穩壓器的實例,介紹開關穩壓器技術的進步。 線性穩壓器具有較低的輸出噪聲,比較容易實現,需要較少的支持元件,能夠很快的響應負載變化,而且成本低于開關穩壓器。但是,隨著功率需求的增大,線性穩壓器無法有效的輸出大電流。典型的開關穩壓器能夠有效的輸出大電流,但通常需要多個支持元件,會帶來噪聲代價。開關穩壓器設計不斷發展,現在能夠支持開關穩壓器來替代線性穩壓器。下面會詳細介紹這一新技術的各方面。

1.1 開關穩壓器設計的發展

在過去十年中,開關穩壓器經歷了很多關鍵變革。這包括最開始的 DC/DC 變壓器 IC、外部電源 FET,以及電感等很多外部支持元件。后來是微型開關電路,這些電路在微型電路板上實現,采用了 PCB 標準接口。然后發展到 DC/DC 變壓器和 MOSFETS 集成到一個封裝 ( 單片轉換開關 ) 中,只有電感還保留在封裝之外。最近的發展則是單封裝解決方案。下面詳細介紹這些發展過程。

微型 PCB 上的微型電路解決方案

微型 PCB 上的微型電路有兩個與 DC/DC 變壓器模塊相關的標準;負載點聯盟 (POLA) 和分布式電源開放標準聯盟 (DOSA)。每一標準都定義了引腳輸出接口、標準封裝大小,以及標準電接口規范和控制。這些技術的例子有 Artesyn TM Technologies PTH12060DC/DC 變壓器 (POLA 標準)、Tyco Electronics ATA010A0X3-SR 電源模塊 (DOSA 標準)。它們都需要很少的外部支持元件,引腳區面積在 1.1X0.7 英寸左右。這些模塊有助于減小引腳區面積,優化與開關穩壓器電路相關的雜散效應,如圖 1 所示。

?

圖 1. 電源模塊,POLA 和 DOSA 標準

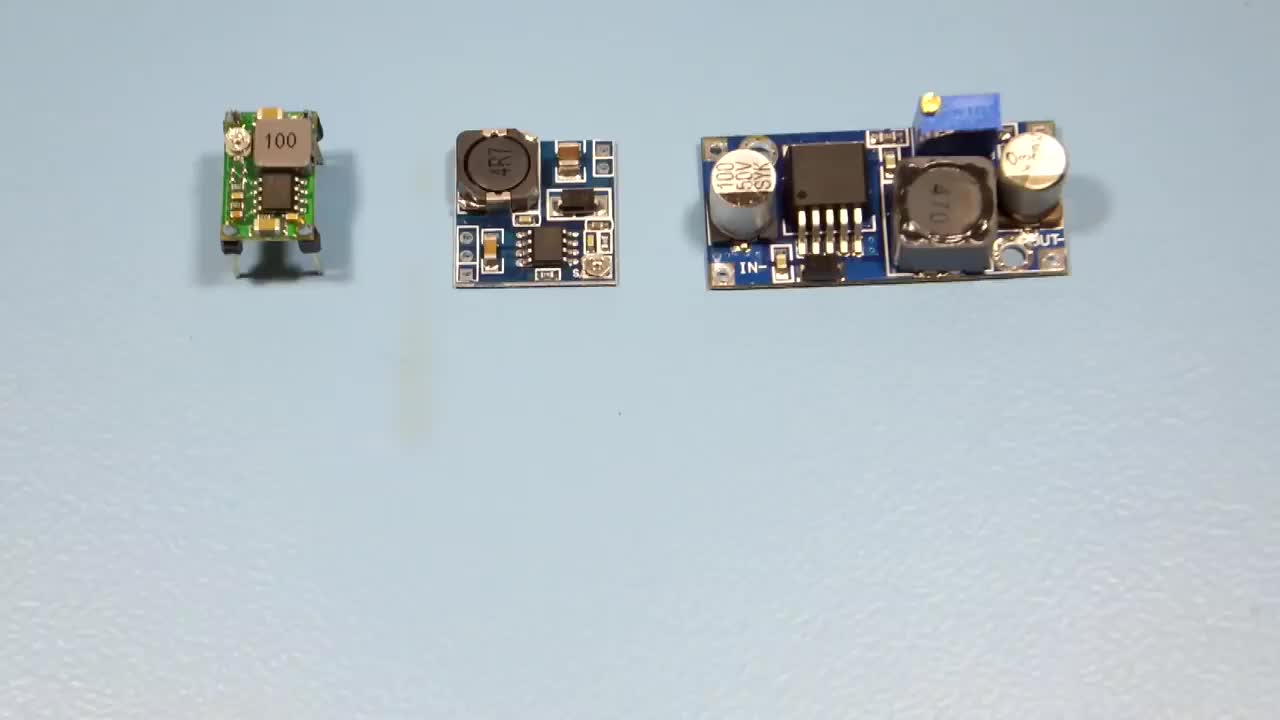

單片封裝解決方案

一些供應商現在提供開關穩壓器,在一個封裝中集成了所有電源供電元件,例如凌力爾特公司的Module 系列、Intersil 公司的電源模塊系列,以及國家半導體公司的簡單開關電源模塊系列等,如圖 2 所示。

?

圖 2. 單片封裝解決方案

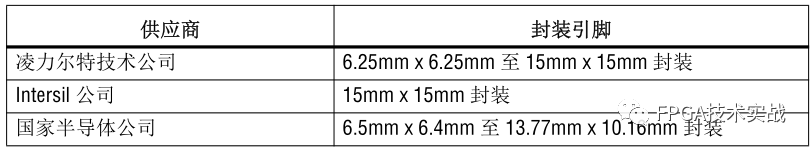

例如,凌力爾特公司的 Module 采用與開關穩壓器電路相關的所有元件,將其封裝在一個基底上。DC/DC 變壓器、MOSFET、電感等主要模塊位于獨立的基底上,彼此之間相互連接。與 POLA 和 DOSA 模塊相比,這一技術更優化,進一步減小了引腳區面積。表 1對比了每一封裝的引腳區面積。

表 1. 封裝引腳區對比

2.FPGA 電源隔離指南

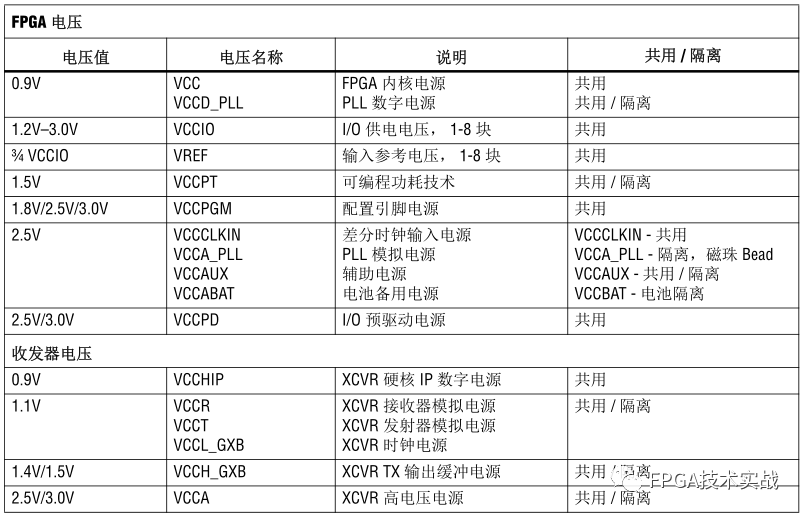

典型的 FPGA 器件含有很多電源線,甚至需要更多的電源線對噪聲敏感的 SERDES 收發器進行供電。例如,表 2 顯示了所推薦的 Altera 收發器 Stratix IV GX FPGA 器件電源線隔離方案。雖然這一 FPGA 中有很多電源線,但是,取決于具體設計,某些電源線共用了同一穩壓器。然而,由于噪聲和性能問題,需要對這些電源線進行隔離。設計人員必須嚴格按照生產商的建議進行設計,以滿足電源要求。一些對噪聲敏感的電路需要低噪聲電源。如果在關鍵區域不能提供干凈的電源,那么將影響抖動發生和 PLL功能。

表 2.Stratix IV GX FPGA 中的電源線隔離實例

2.1 鐵氧體磁珠濾波

您可以使用鐵氧體磁珠作為另一種隔離方式,幫助克服設計高速 FPGA 的高效 PDN 和多條電源線所面臨的問題。可能需要多個穩壓器才能隔離關鍵區域的敏感電源。但是,通過使用鐵氧體磁珠,多條電源線可以共用同一穩壓器,同時保持與其他電源平面的隔離。低 Q 鐵氧體磁珠在很寬的高頻范圍內都具有高阻抗特性,非常適合實現低通噪聲濾波器。設計人員應避免鐵氧體磁珠常見的不利影響,例如,電壓振鈴和反共振等。

2.2 去耦合分析

去耦合設計是 PDN 的關鍵組成。一般的去耦合方法無法滿足高速 FPGA PDN 的要求。您可以使用 Altera 的 PDN 工具進行大量的分析,實現精細的去耦合設計。PDN 工具分析每一電壓平面,在以下因素基礎上開發去耦合設計:

分布電感

電容裝配和電感

BGA 和電感

平面電容

穩壓器類型

分析中包括了電源線的所有元件,支持設計人員準確的去耦合電壓平面。

3.推薦的單片封裝解決方案

凌力爾特技術公司、國家半導體公司以及 Intersil 公司提供單片封裝解決方案,在封裝中集成了 DC/DC 控制器、電感和電源 MOSFET。供應商一般會為測試各種類型的穩壓器提供評估板。Altera 建議您在進行選擇之前使用這類電路板來評估所需電源的性能。

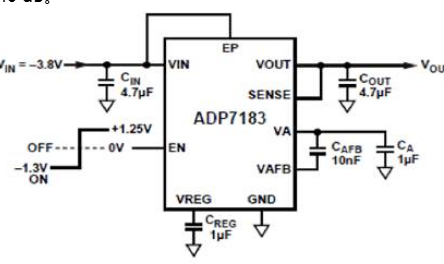

3.1 凌力爾特技術公司(ADI)

凌力爾特技術公司的 ? Module 電源是高速收發器 PDN 設計解決方案。這些集成開關電源能夠提供高效的大電流解決方案,保證與傳統開關穩壓器一樣具有較低的輸出電壓波紋以及較低的開關噪聲。利用電流模式體系結構,可以在輸出端增加額外的電容,降低波紋,而且不會影響電源的穩定性。在一個封裝中集成電源元件能夠有效的控制雜散電容和電感,從而降低了電源的 EMI 和開關噪聲。下面重點解釋了為什么這些電源適用于高速收發器:

小外形封裝

緊密耦合負載 / 線性穩壓

非常低的輸出波紋

13×C/W 至 15×C/W 熱阻

多路輸出器件

作為單片 IC 進行測試 / 特性測量

不會有電源周期失敗問題

支持各種 I/O 電平

支持各種輸出電流電平

與 LDO 設計一樣簡單

3.2 國家半導體公司

國家半導體公司的 SIMPLE SWITCHER 電源模塊是高速收發器和其他噪聲敏感信號通路IC 的電源解決方案。這些模塊為提高散熱性能和可靠性而采用了單片露底封裝技術。這些模塊集成了屏蔽電感和關鍵的信號通路控制電路,減小了雜散電容和走線電感。模塊實現了高效的同步開關穩壓器,以及簡單的線性穩壓器。開關單元全部置入封裝中,這些器件具有較低的 EMI 性能。國家半導體公司電源模塊還在每一系列的電流選項上提供引腳至引腳兼容功能,表明只需要一種設計和布板就能夠支持六種不同的電源。

3.3 Intersil 公司

Intersil 公司的 ISL8200M 是大功率電流共享 DC/DC 電源模塊,適用于數據通信、電信和 FPGA 應用。獲得專利的多相位工作電流共享技術減小了波紋電流,降低了復雜度。這種穩壓器的并行配置功能能夠提供 60 安培的電流。ISL8200M 的散熱增強緊湊 QFN 封裝能夠工作在全負載和過溫狀態下,不需要強制空氣散熱。

4.PDN 性能實例

該部分介紹 PDN 噪聲對抖動分量的影響,然后是 PDN 對 Altera Stratix IV GX 器件收發器性能影響的測試案例,它使用了各種 PDN 配置。

4.1 受影響和不受影響的抖動分量

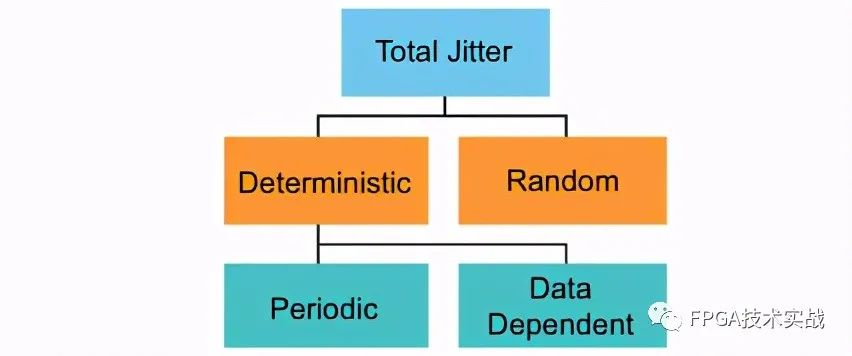

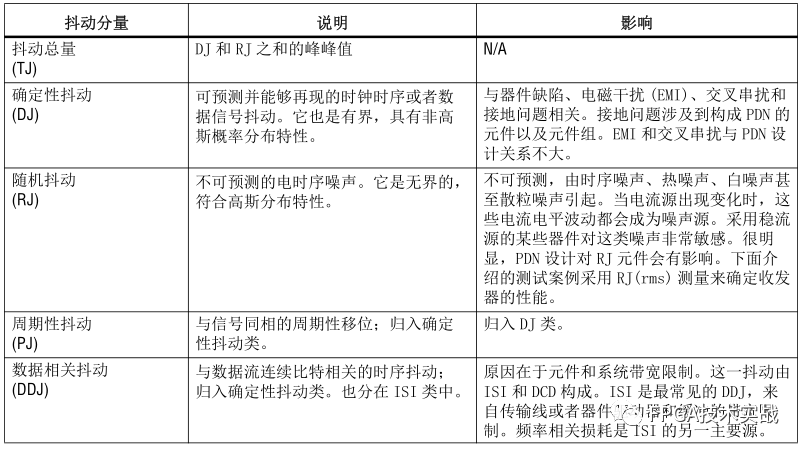

PDN 噪聲對抖動分量有較大的影響。圖 3 解釋了表 3 中的各種抖動分量

圖 3. 抖動樹 為確定 PDN 設計中受影響的抖動分量,根據其產生原因來定義每一抖動分量。例如,當周期性抖動 (PJ) 具有正弦屬性時,它通常與數據碼型干擾以及電源波動相關。PDN缺陷會影響 PJ。例如,欠額穩壓器會成為電源波動的原因。耦合較差的設計會導致電壓下陷。表 3 詳細介紹了 PDN 噪聲對抖動分量的影響。

表 3. 噪聲對抖動分量的影響

4.2 收發器性能試驗

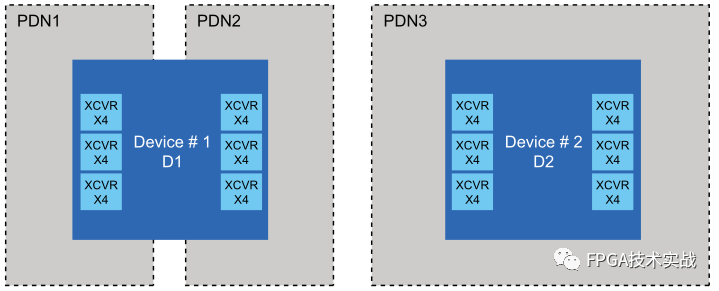

下面的試驗使用了兩塊 Stratix IV GX (EP4SGX230KF40C2) 測試板來測量收發器在不同 PDN 配置時的性能。收發器位于器件的每一側,如圖 4 所示。

圖 4.Altera 電源共用電路板圖 1 號器件在設計上每一側都有自己唯一的 PDN。2 號器件的所有側都有唯一的 PDN 設計。這種設置建立了三種 PDN 設計,共用或者隔離收發器電源線。這三種配置被稱為“PDN1”、“PDN2”和 “PDN3”。在每一種配置中,出于試驗和對比目的,設定了各類電源共享、隔離和穩壓器。

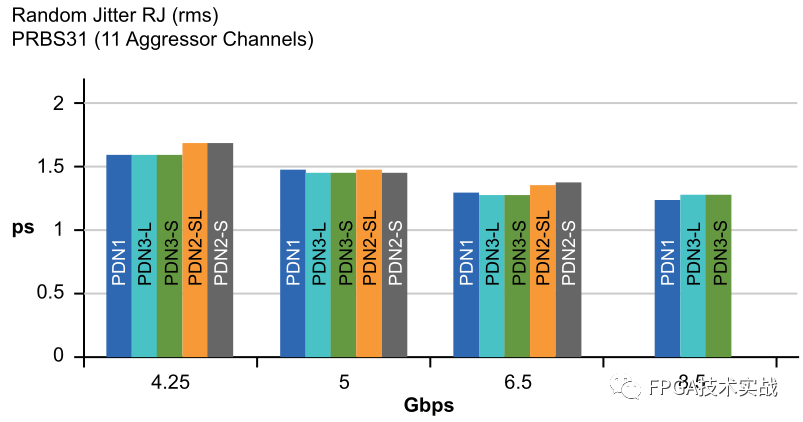

這一試驗的目的是確定共用關鍵收發器電源線效果,采用各種類型的穩壓器來驅動它們。該測試測量了被干擾收發器通道 RJ(rms) 值 ( 通過高頻碼型 - 1010),而其他所有收發器通道都運行 PRBS31 數據。針對不同的配置和 4.25Gbps 到 8.5Gbps 的多種數據速率來采集數據。RJ(rms) 參數為衡量性能提供了關鍵指標,因為這一參數對性能的影響最大。

PDN 第 1 種配置

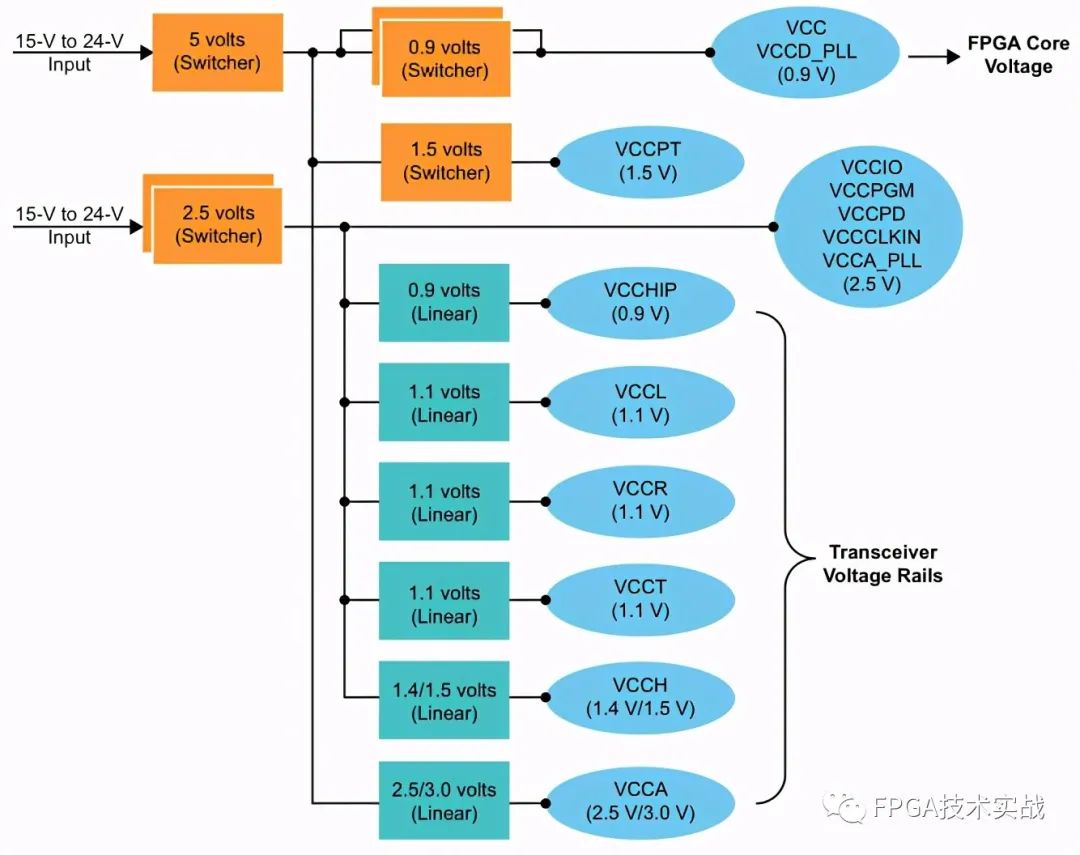

在 PDN1 中,隔離了所有六條收發器電源線,由線性穩壓器進行驅動。每一電源線都有自己的電壓平面,如圖 5 所示。

圖 5.PDN1 電源樹

PDN 第 2 種配置

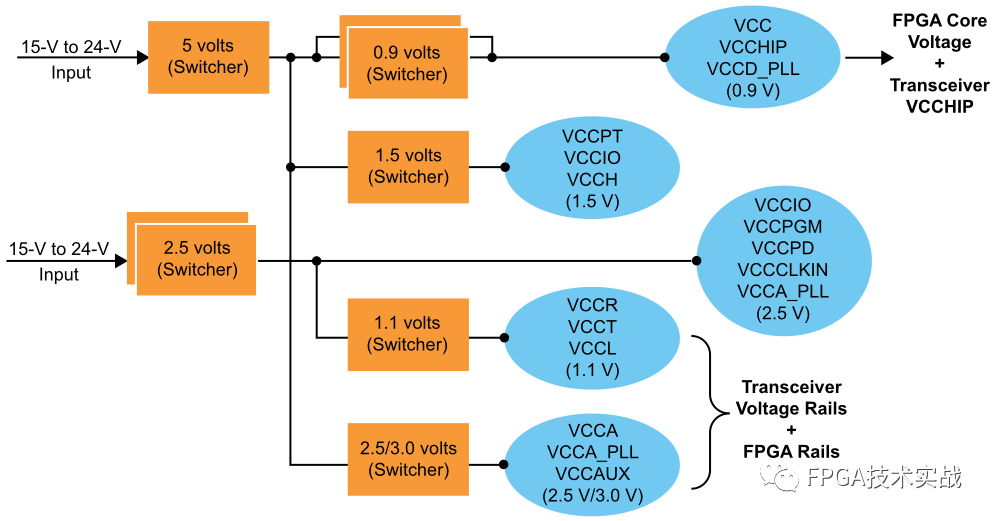

在 PDN2 中,所有收發器電源線與其他電源線共用。共用電源線有自己的電壓平面。所有電源線都由凌力爾特技術公司的 Module 開關穩壓器進行驅動,如圖 6 所示。

圖 6.PDN2 電源樹

VCCHIP (0.9V) 與 VCC (0.9V) 共用

VCCR (1.1V) 與 VCCT (1.1V) 共用,與 VCCL (1.1V) 共用

VCCH (1.5V) 與 VCCPT (1.5V) 共用

VCCA (2.5V) 與 VCCIO (2.5V) 共用

注意:由于電路板的設計約束,所以 PDN2 配置不支持 8.5Gbps。

PDN 第 3 種配置

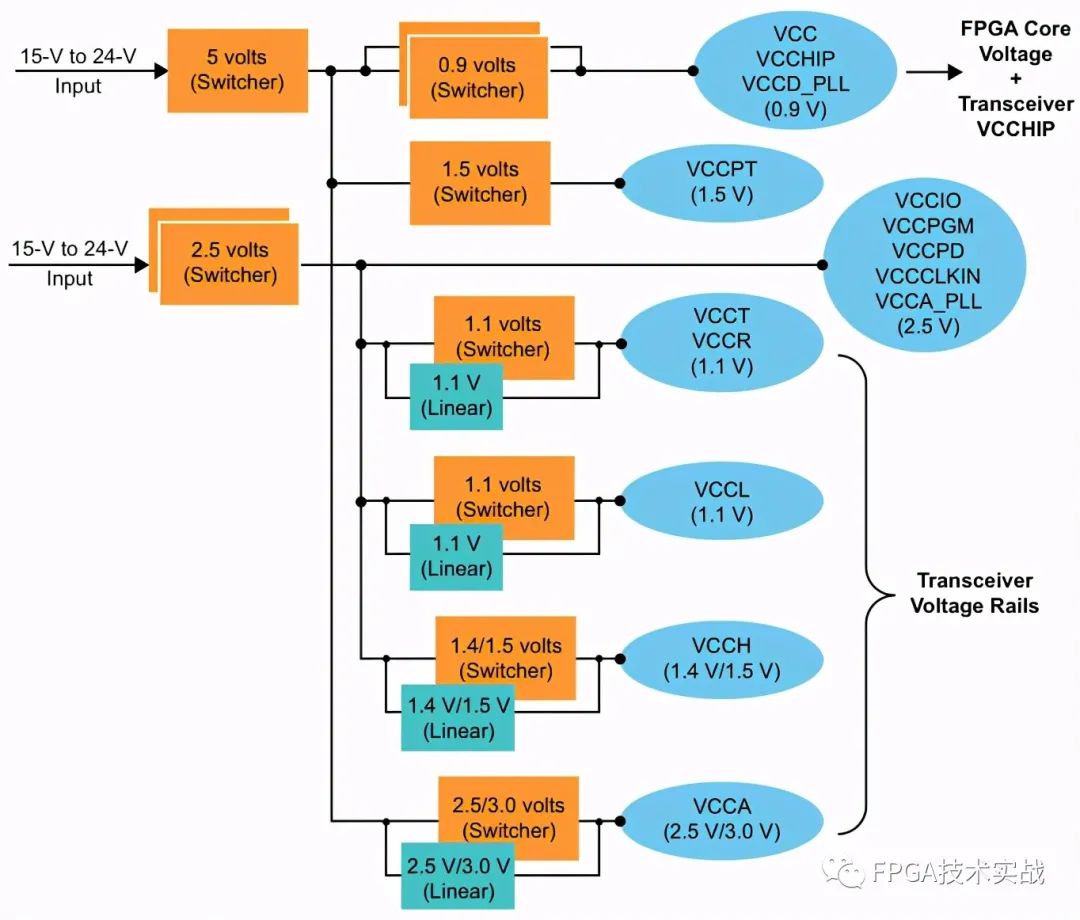

在 PDN3 中,共用兩條收發器電源線,由線性穩壓器或者凌力爾特技術公司的 Module開關穩壓器進行驅動。

VCCHIP (0.9V) 與 VCC (0.9V) 共用

VCCR (1.1V) 與 VCCT (1.1V) 共用

隔離其余的收發器電源線,有自己的電壓平面。這些電源線由線性穩壓器或者凌力爾特技術公司的 Module 開關穩壓器進行驅動,如圖 7 所示。

圖 7.PDN3 電源樹

測試案例

測試案例包括 12 個收發器通道傳輸數據。將一個通道設定為被干擾通道,其 TX 輸出接入頻譜分析儀的輸入。這一被干擾通道傳輸高頻碼型 (1010)。其他的 11 個干擾源通道都在外部環回,傳輸來自 FPGA 器件內核中的 PRBS31 數據碼型。對每一測量都復制了多次,以確保結果能夠再現。

最初的測試從 PDN1 數據采集開始,建立基線。考慮到隔離了所有收發器電源線,因此PDN1 應該得到最佳結果。然后,測試了其余配置的其他組合,對數據進行采集。采用Agilent E4440A 頻譜分析儀來測量所有數據,以皮秒單位來測量相位噪聲或者RJ(rms)。

測試結果

圖 8 總結了 5 種不同配置時采集的數據。PDN1、PDN2 和 PDN3 配置展示了隔離和共用電壓平面。PDN2 和 PND3 還提供其他功能,針對某些收發器電源線,在開關穩壓器和線性穩壓器之間進行選擇。各種配置曲線如下所示:

PDN1 - (XCVR 電源線 = 所有線性穩壓器 )

PDN3 - L (XCVR 電源線 = 所有線性穩壓器 )

PDN3 - S (XCVR 電源線 = 所有開關穩壓器 )

PDN2 - SL (XCVR 電源線 = 線性 / 開關穩壓器的組合 )

PDN2 - S (XCVR 電源線 = 所有開關穩壓器 )

圖 8.RJ(rms) 數據

如前所述,RJ(rms) 參數對總體性能的影響最大。測試案例采用不同條件處理相關測量,重點是 RJ(rms) 值,作為評估性能的標準。由于組合了電源線,改變了穩壓器類型,因此,這一試驗清楚的展示了收發器性能不受影響。

5.結論

本文介紹了設計人員怎樣通過均衡抖動余量和穩壓器數量,使用高級開關穩壓器來提高低噪聲應用的性能。從這些試驗中采集的數據表明,采用 Altera 的 Stratix IV GX器件時,不同配置的性能略有不同。這一數據涵蓋了高達 8.5Gbps 的配置。設計人員可以組合電源線,使用新的電源模塊技術,實現更簡單、更高效的 PDN 設計。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論