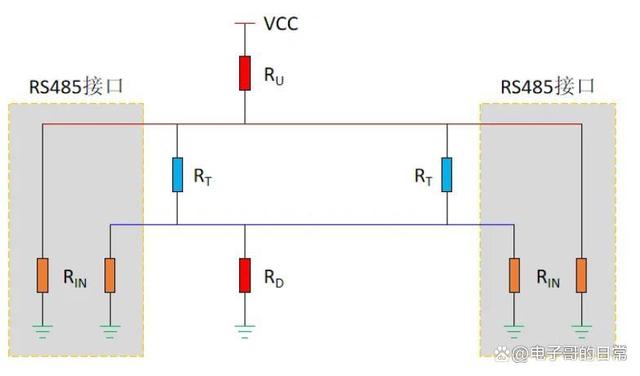

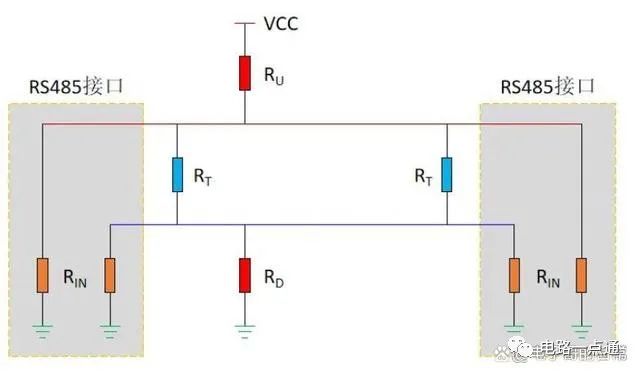

RS-485總線廣泛應用于通信、工業自動化等領域,在實際應中,通常會遇到是否需要加上下拉電阻以及加多大的電阻合適的問題,下面我們將對這些問題進行詳細的分析。

2017-01-19 11:38:40 26511

26511

RS485是一種常見的通訊接口方式,在我們的實際產品中也是多次使用。但我們平常并不會去過多考慮某一實現的細節問題,不過最近我們遇到了一個因如上下拉電阻的選擇問題而造成的通訊故障,所以在這一片中我們來討論一下RS485總線上下拉電阻的選擇問題。

2022-12-14 15:47:55 5006

5006

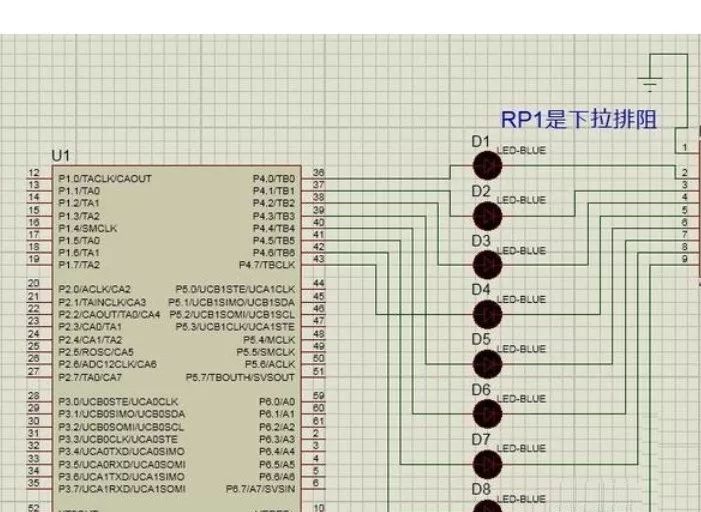

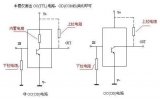

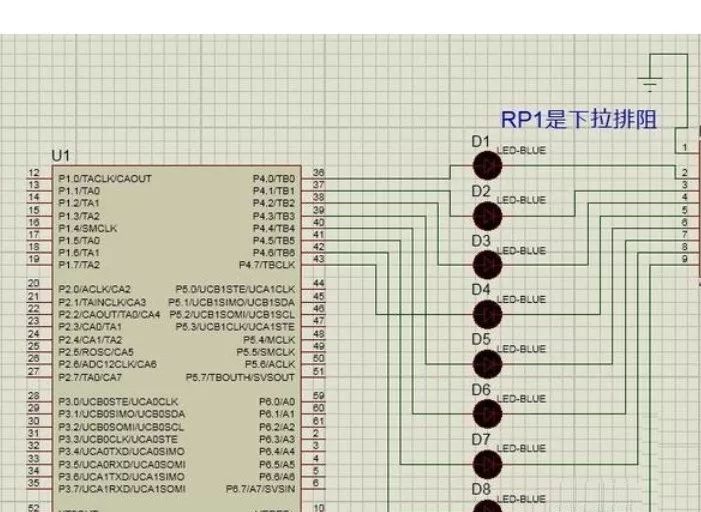

一、上下拉電阻介紹 ??上拉電阻:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平。作用:上拉是對器件注入電流;灌電流;當一個接有上拉電阻的IO端口設置為輸入狀態時,它的常態為高電平

2023-04-21 09:49:34 6875

6875 什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。那么,上拉電阻和下拉電阻的用處和區別分別又是什么呢?

2023-05-26 10:16:01 1911

1911

電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻,這兩者統稱為“拉電阻”,最基本的作用是:將狀態不確定的信號線通過

2023-06-07 15:20:05 1174

1174

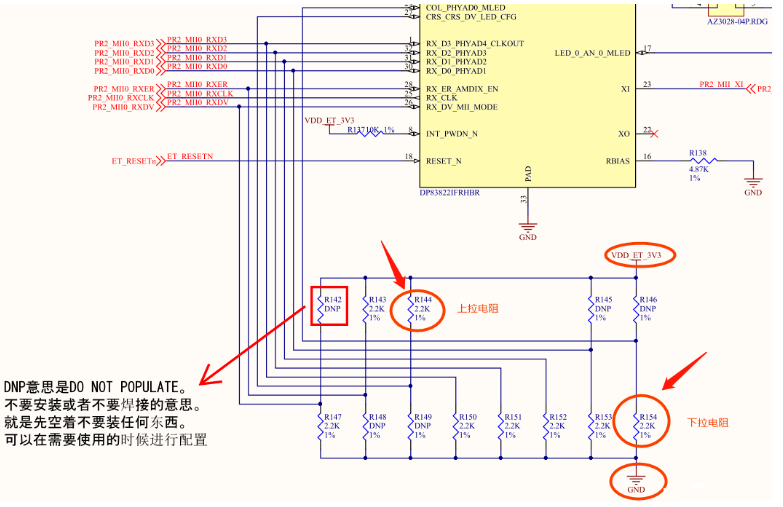

電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。

2023-10-08 16:23:42 1186

1186

之前始終對維持確定的高低電平狀態沒有足夠深的理解,既然單片機自身是有輸出高低電平的能力,為什么還需要在外部上下拉,這不是浪費能量嗎?

2023-11-06 15:37:13 611

611

作為電路中最常見的電子元器件之一,電阻可以實現限流、隔離、上下拉等不同功能。以上拉為例,IIC通信接口SDA和SCLK都需要通過電阻實現上拉輸入/輸出。那么,電阻是如何實現上下拉功能的呢?

2023-11-13 18:23:06 788

788

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2013-07-21 21:43:41

容易接受外界的電磁干擾。4、電阻匹配,抑制反射波干擾:長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。5、預設空間狀態/缺省電位:在一些 CMOS 輸入端接上或下拉

2012-03-08 14:59:41

深入淺出上拉電阻下拉電阻淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡單,就是將一個不確定的信號確定下來。通過上拉電阻將不確定的信號鉗位到高電平,通過下拉電阻,將不確定的信號鉗

2021-11-30 06:07:53

拉電阻2.0淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡單,就是將一個不確定的信號確定下來。通過上拉電阻將不確定的信號鉗位到高電平,通過下拉電阻,將不確定的信號鉗位到低電平

2022-01-14 06:50:45

上下拉電阻的作用

2015-04-18 21:21:07

器件連接時的灌電流能力不盡相同,連接上會有驅動問題,此時需要加上拉電阻,加大輸出引腳的驅動能力。 阻抗匹配長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配(并聯終端匹配),有效的抑制反射波

2019-07-27 08:38:52

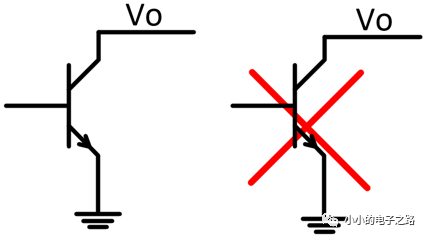

的是什么器件,如果該器件需要高電壓的話,而輸出口的輸出電壓又不夠,就需要加上拉電阻。 l 如果有上拉電阻那它的端口在默認值為高電平你要控制它必須用低電平才能控制如三態門電路三極管的集電極,或二極管正極去

2016-09-23 17:19:31

上下拉電阻的用法

2012-08-16 13:38:14

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2012-08-07 15:15:18

上下拉電阻的用途,總結一下,對很多人應有幫助

2012-10-24 17:01:13

的輸入。 -------上拉電阻是用來解決總線驅動能力不足時提供電流的。一般說法是拉電流,下拉電阻是用來吸收電流的。 上下拉一般有兩個用處:1)提高輸出信號的驅動能力、 2)確定輸入信號的電平

2018-06-28 06:21:54

因為查看數據手冊,發現AD1674芯片在轉換過程中邏輯輸出口(12位并行輸出口)輸出為高阻態,如果想獲得一個穩定的輸出狀態,能否加上10k下拉電阻?還有狀態位STATUS輸出口,能加上10k下拉電阻嗎?

2024-01-11 07:34:32

輸入輸出要加上下拉電阻嗎?

2024-01-03 06:28:17

上拉和下拉是指GPIO輸出高電位(上拉)還是低電位(下拉)。上拉就是輸入高電平,然后接一個上拉電阻(起保護作用),知道上拉就表示該端口在默認情況下輸入為高電平。下拉就相反了,指輸入低電平,然后接一個

2019-05-21 06:21:09

輸入信號的噪聲容限增強抗干擾能力【噪聲容限】6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。【EMC】7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制

2012-02-24 10:38:07

想問一下什么情況下需要加上下拉電阻?為什么需要加上下拉電阻?

2021-03-06 06:31:18

RS485多機通訊有50個接點總長度大于1000米,從2-49個機 A,B是否也需要加上下拉電阻,供電部分是50個一起供電,還是分開供電,想在我一起供電,比分開供電穩定一點

2023-04-27 17:36:40

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2011-09-19 08:55:51

、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉

2008-05-22 08:46:35

。 7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 上拉電阻阻值的選擇原則包括: 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2

2019-06-27 05:55:08

。在I2C總線等總線上,空閑時的狀態是由上下拉電阻獲得6. 提高芯片輸入信號的噪聲容限:輸入端如果是高阻狀態,或者高阻抗輸入端處于懸空狀態,此時需要加上拉或下拉,以免收到隨機電平而影響電路工作。同樣如果

2019-09-05 11:52:04

,提供泄荷通路。5、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

2016-09-27 09:20:11

一、什么是上下拉電阻?上拉、下拉電阻統一稱為拉電阻,作用是將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉)這里有人可能會疑惑?什么叫狀態不確定的信號?在數字電路中,通常有三種

2022-01-14 08:58:32

管腳懸空就比較容易接受外界的電磁干擾。

4、電阻匹配,抑制反射波干擾:長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

5、預設空間狀態/缺省電位:在一些

2023-05-18 17:30:56

上下拉電阻大小計算,一直很困惑,這些大小計算來路,還懇請各位幫忙引導~~決定因子有那些.值得大家深入,問過公司好多同事,都說不出所以然.網友1:上拉或下拉取值一般選常用容易找到的阻值基本上就可以了

2015-10-19 18:06:17

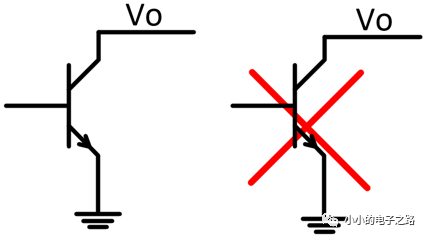

在網上找了很多關于上下拉電阻的資料,可是感覺說的還是很亂,依然很難理解。經過認真研究,現將自己所得所感寫下來希望這只是個討論的開始而絕非終結。首先,想說上拉電阻幾乎都是應運三極管電路而生的,但是本文

2011-10-25 09:53:50

`請問下nand的WEN,CEN,REN都接了上拉電阻,這是為什么,這個阻值怎么定的,還有WPN接了下拉又是怎么回事`

2017-05-12 13:33:39

干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。8、在數字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。四、上拉電阻阻值選擇原則1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻

2011-07-28 09:58:10

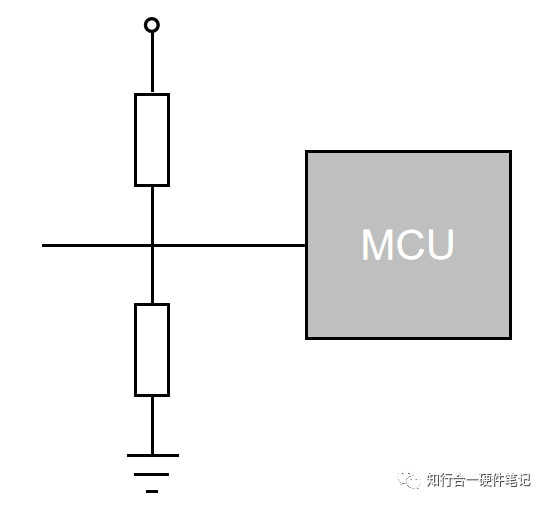

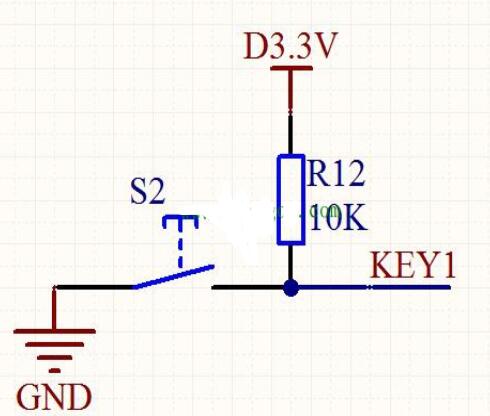

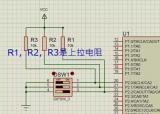

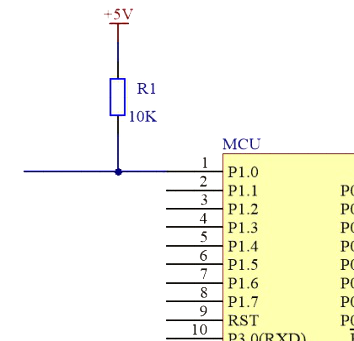

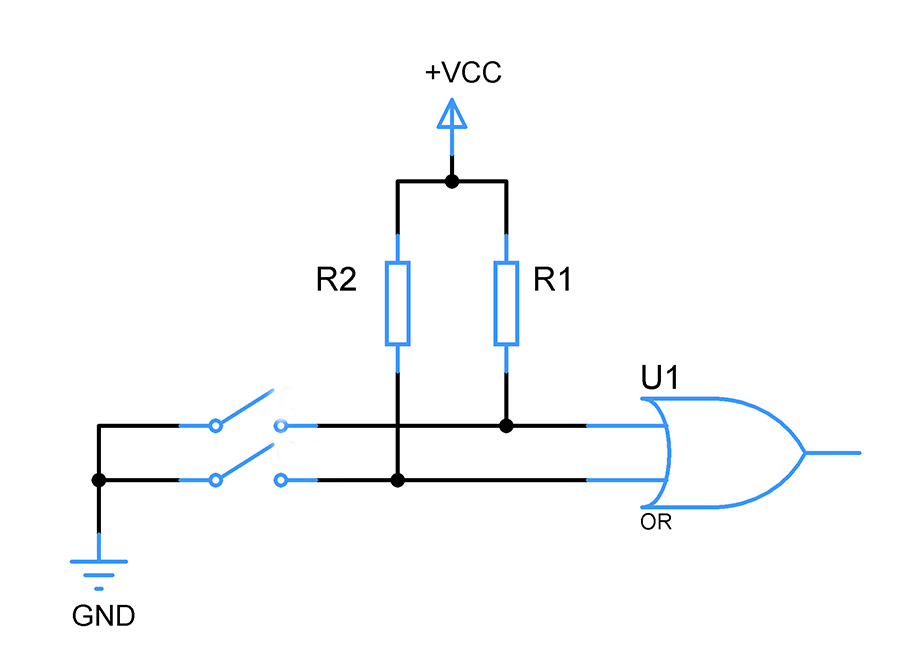

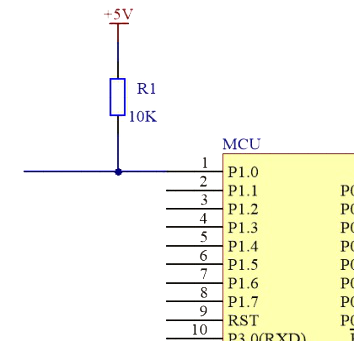

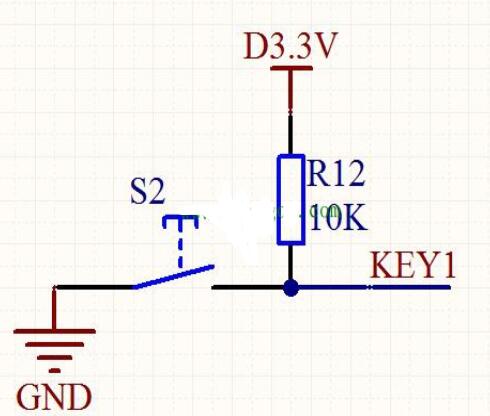

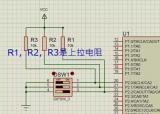

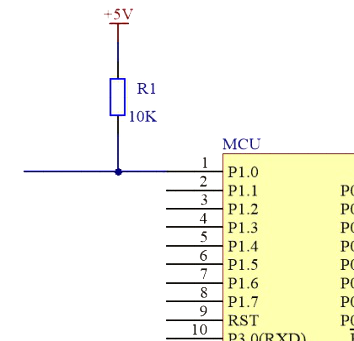

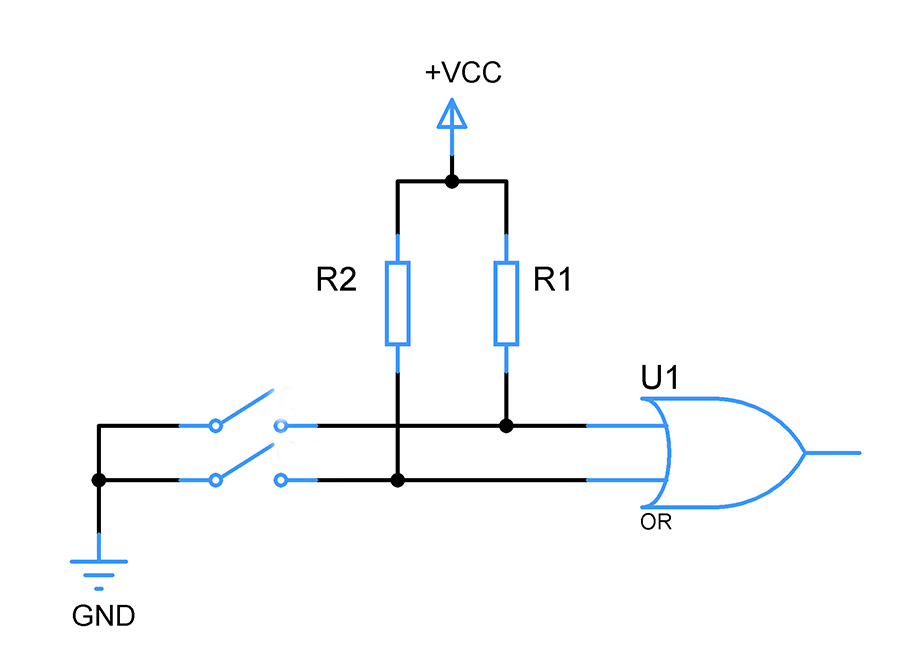

判斷上下拉電阻時,只需要看按鍵按下之前,兩端是高電平還是低電平。例如:R1這個電阻,一端接VCC,在按鍵按下之前兩端是高電平,所以它就是上拉電阻,是為了檢測低電平輸入。R2這個電阻,一端接GND,在按鍵按下之前,兩端是低電平,所以它就是下拉電阻,是為了檢測高電平輸入。...

2022-01-14 08:31:27

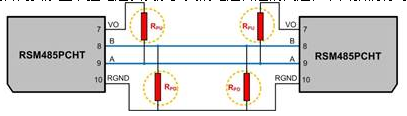

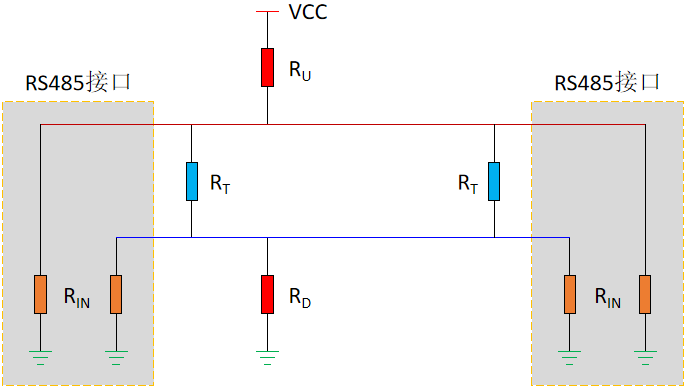

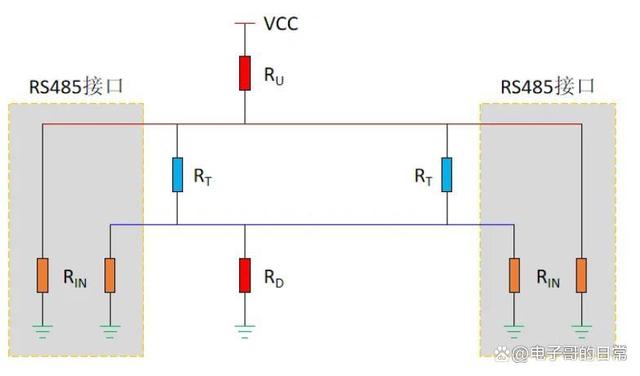

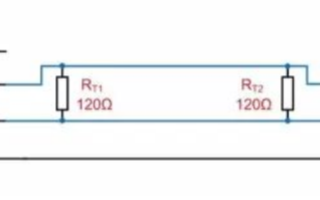

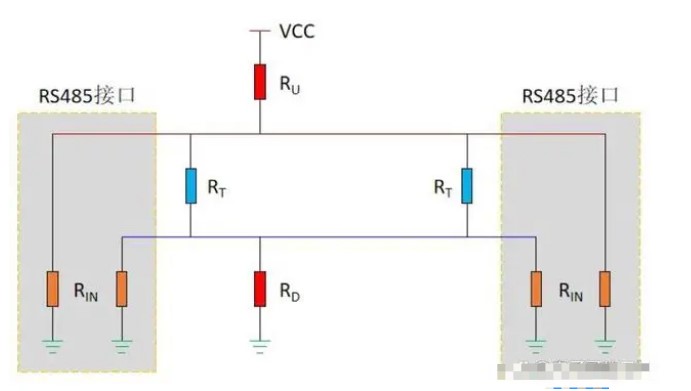

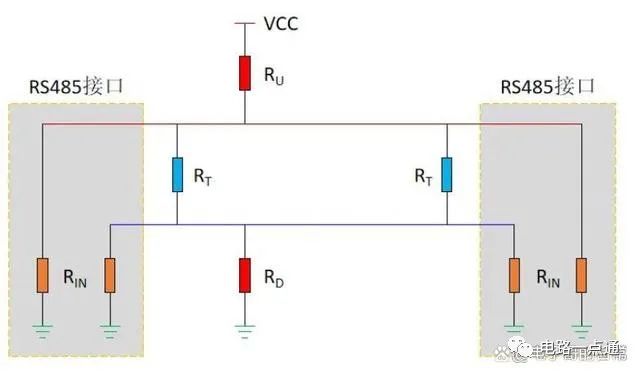

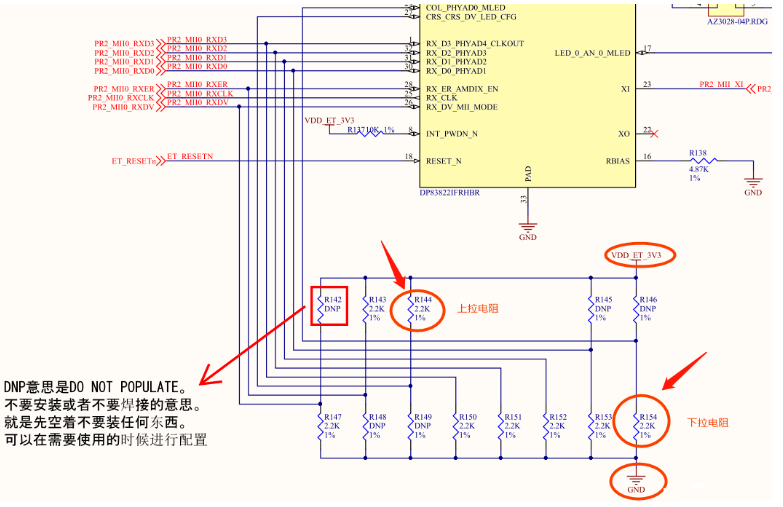

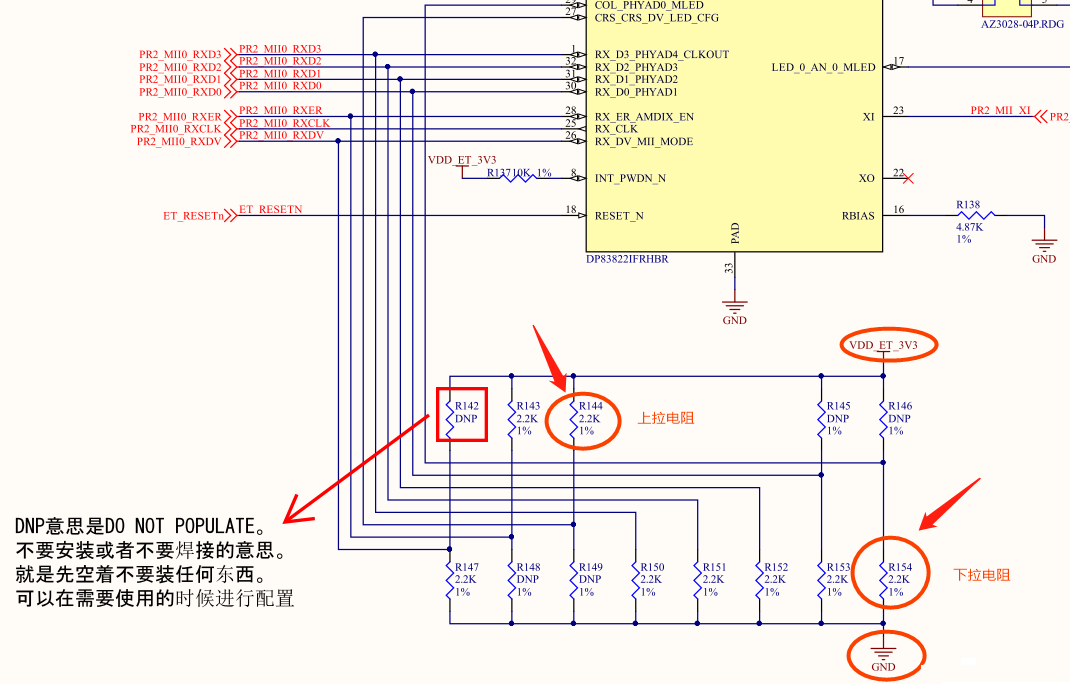

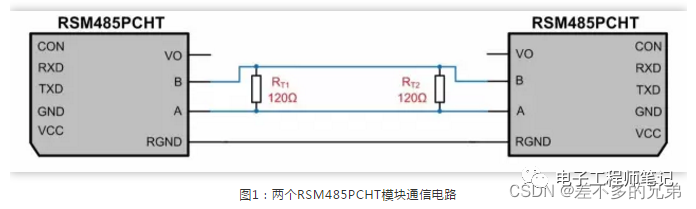

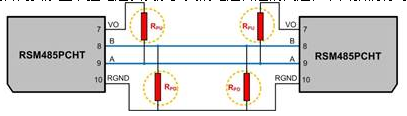

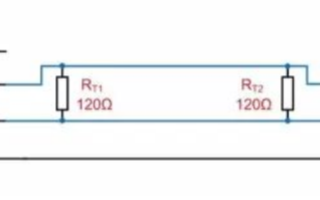

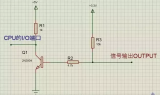

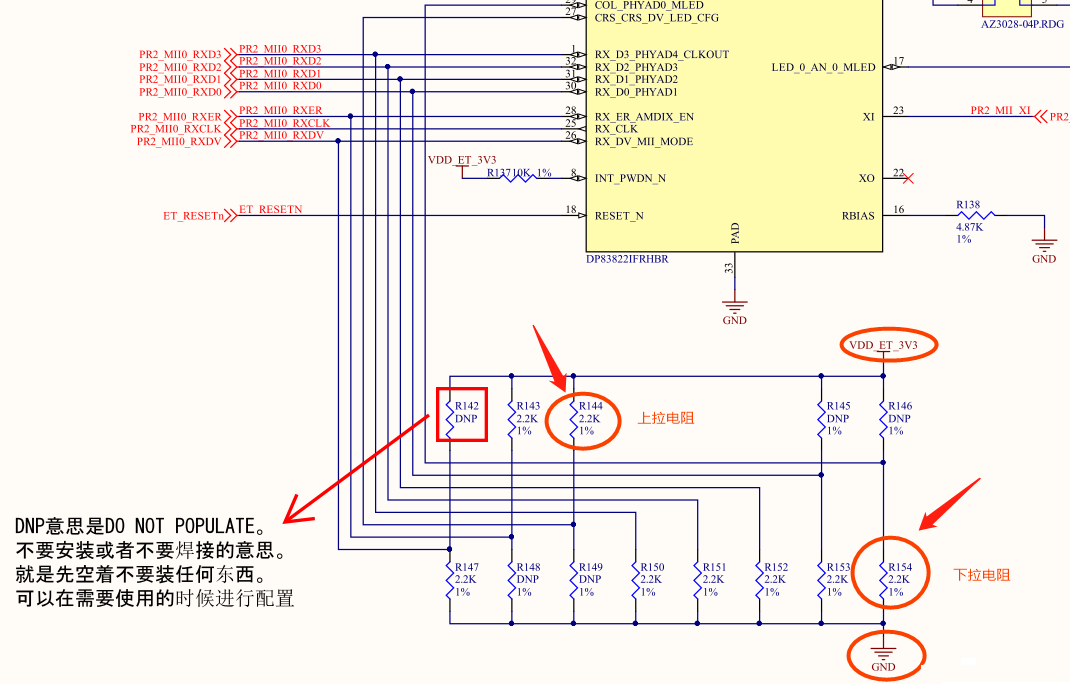

。二、什么情況下需要加上下拉電阻?當遇到信號反射問題時,通常會通過增加匹配電阻來避免信號反射,以1對1通信為例,如圖1所示。由于485總線通常使用特性阻抗為120Ω的雙絞線,因此在485總線的首尾兩端增加120Ω終端電阻來避免信號反射問題。

2019-05-21 07:10:59

已知上下拉電阻,怎么計算出AD值,下拉電阻是10k,上拉接NTC

2018-07-18 14:39:51

上拉電阻,上拉電阻時,在待機狀態下,源端常為高阻態,不加上下拉,輸入導線呈現天線效應,一旦管腳受到輻射干擾,管腳輸入狀態極易被感應發生變化。下拉電阻:平常狀態輸入表現為低電平,但輻射干擾進來后,會通過下拉電阻泄放到地,就會發生一個從 Low——Hight 的跳變,容易產生誤觸;上拉

2022-01-14 07:42:58

就比較容易接受外界的電磁干擾。www.eda365.com, S! |7 w* B( w2 r9 D4 b$ {- d8 d4 G7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配

2014-11-17 10:24:15

,那么最好下拉,否則當控制信號沒有建立的時候就會出現兩個沖突,可能燒片。如果計算機總線上面掛了一個D/A,上電復位信號要對它清零或者預置,那么總線可以上下拉到你需要的數字。至于上下拉電阻的大小,這個情況

2014-08-21 09:56:08

引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 另外,上拉電阻阻值的選擇原則包括:1.從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2.從確保足夠的驅動電流考慮應當足夠

2017-05-22 18:49:54

在學習以及電路設計中對上下拉電阻一直很模糊,我感覺這也是大家共同的問題,希望原子哥能結合具體電路圖給大家講解一下,謝謝

2019-09-12 04:36:02

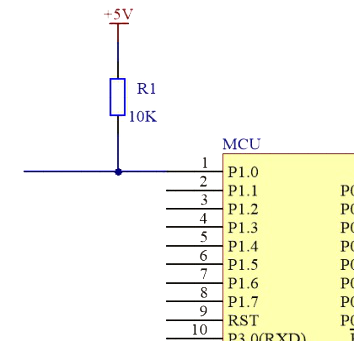

拉電阻,程序可以正常跑通,但有些資料卻強調說單片機的IO口使用時要加上拉、下拉電阻。以下就以LBQ同學的可愛問題解釋一下上下拉電阻吧。事不宜遲,馬上進入正題首先聲明一下:我們這次用的是STC89...

2022-01-14 07:09:37

為:

到這里,我們就得到了比較具有使用價值的上拉下拉電阻阻值的計算公式了。我們只需要根據實際的總線使用情況選擇n的值和電源的值就可以得到我們想要的上下拉電阻值。不過有一個問題需要注意,上下拉電阻

2023-04-27 17:03:40

請教各位,MAX485通信,每個 從機485都要加上下拉電阻嗎,要加多大合適?有的資料說可帶30個從機,485總線可帶多少從機?

2018-04-17 15:36:52

當Vccio=3. 3V時, 對于輸入腳, 它兼容TTL, CMOS電平;對輸出腳, 它是否也兼容TTL和CMOS電平?對CMOS電平, 是否需要用OpenDrain 加上下拉電阻來實現?

2019-09-03 05:55:08

IO口輸出時需要上拉或下拉嗎?

輸出時的上下位有什么意義?

2023-10-28 07:40:48

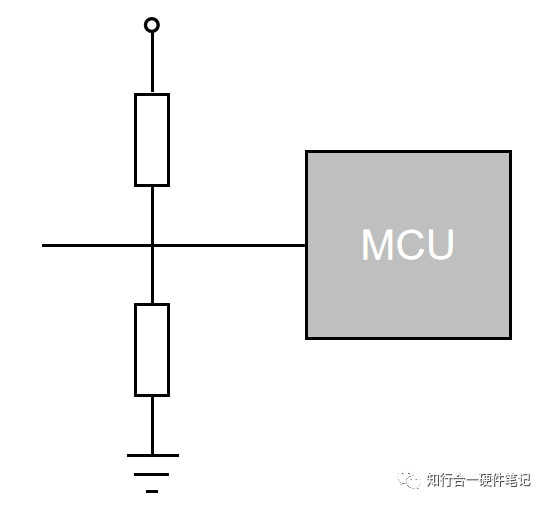

在數字電路的應用中,上拉電阻、下拉電阻起著穩定電路工作狀態的作用。圖1所示的反向器,輸入端Ui通過下拉電阻R接地,這樣在沒有高電平輸入時,可以使輸入端穩

2007-10-15 17:36:42 3210

3210 上拉電阻與下拉電阻

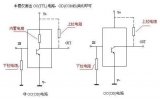

上下拉電阻: 1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),

2008-01-14 13:10:44 6297

6297 上拉下拉電阻(zz)基礎知識

一、什么是上拉電阻?什么是下拉電阻?

上拉就是將不確定的信號通過

2009-11-23 09:16:09 5029

5029 上拉電阻和下拉電阻的選型和計算,根據不同情況選擇不同上下拉電阻的方法

2015-11-30 18:20:28 0

0 關于上拉電阻和下拉電阻的入門必知,新手要學

2016-02-17 11:21:25 0

0 上拉電阻、下拉電阻、限流電阻的原理和作用

2016-11-11 18:42:28 55

55 上拉電阻和下拉電阻的作用及選擇

2016-12-15 18:39:07 25

25 上拉電阻,與下拉電阻的分析

2017-07-24 16:40:20 70

70 本文首先介紹了下拉電阻的作用,其次介紹了下拉電阻的原理以及典型電路,最后闡述了下拉電阻的選擇。

2018-08-22 17:51:37 63736

63736 上拉電阻就是將不確定的信號通過一個電阻拉到高電平,同時此電阻也起到一個限流作用,下拉就是下拉到低電平。

2018-11-02 16:22:25 8495

8495 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2018-12-24 08:00:00 15

15 RS-485總線廣泛應用于通信、工業自動化等領域,在實際應中,通常會遇到是否需要加上下拉電阻以及加多大的電阻合適的問題,下面我們將對這些問題進行詳細的分析。

2019-09-08 10:50:56 22998

22998 本文主要介紹了上下拉電阻的接線方法及作用。

2019-09-30 11:27:36 17287

17287

詳解RS-485上下拉電阻的選擇

2020-02-27 15:33:50 5869

5869

在上拉電阻和下拉電阻的電路中,經常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經常會串一個電阻?

2020-04-28 14:17:04 11546

11546

輸入端如果是高阻狀態,或高阻抗輸入端處于懸空狀態,此時需要加上拉或下拉電阻,以免受到隨機電平的影響,進而影響電路工作。同樣,如果輸出端處于被動狀態,需要加上拉或下拉電阻,如輸出端僅僅是一個三極管的集電極,還可以提高芯片輸入信號的噪聲容限,增強抗干擾能力。

2020-05-29 15:52:51 13568

13568

加上下拉電阻就是加在單片機管腳的帶負荷能力。如上拉電阻的接法就是電源正通過一個合適阻值的電阻后接到需上接的管腳即可。

2020-09-18 16:44:22 5374

5374

來源:互聯網 在電路中加上拉電阻或下拉電阻的目的是確定某個狀態電路中的高電平或低電平。 上、下拉電阻的作用 提高電路穩定性,避免引起誤動作。一些情況下按鍵如果不通過電阻上拉到高電平,那么在上電瞬間

2020-10-12 00:20:03 1714

1714 電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻。

在上拉電阻和下拉電阻的電路中,經常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經常會串一個電阻?

2022-02-10 10:43:08 2420

2420

電子發燒友網為你提供RS-485總線知識:什么情況下需要加上下拉電阻?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-03 08:41:53 4

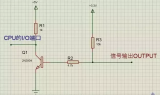

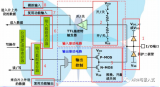

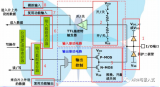

4 STM32中的GPIO 以STM32中的GPIO為例,如上圖是GPIO的結構圖。 從上圖中標號2處可以看到,上拉和下拉電阻上都有一個開關,通過配置上下拉電阻開關,可以控制引腳的默認電平,這里有三種

2021-11-02 10:11:05 11972

11972

經常看到芯片設計手冊時,芯片外圍會有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時候,有個特定的范圍?對上拉電阻和下拉電阻

2021-11-07 13:51:03 26

26 深入淺出上拉電阻下拉電阻淺談上下拉電阻思考:上下拉電阻有什么用呢?答:上下拉電阻的作用非常簡單,就是將一個不確定的信號確定下來。通過上拉電阻將不確定的信號鉗位到高電平,通過下拉電阻,將不確定的信號

2021-11-20 12:21:03 16

16 判斷上下拉電阻時,只需要看按鍵按下之前,兩端是高電平還是低電平。例如:R1這個電阻,一端接VCC,在按鍵按下之前兩端是高電平,所以它就是上拉電阻,是為了檢測低電平輸入。R2這個電阻,一端接GND,在按鍵按下之前,兩端是低電平,所以它就是下拉電阻,是為了檢測高電平輸入。...

2022-01-14 14:00:34 19

19 拉電阻,程序可以正常跑通,但有些資料卻強調說單片機的IO口使用時要加上拉、下拉電阻。以下就以LBQ同學的可愛問題解釋一下上下拉電阻吧。事不宜遲,馬上進入正題首先聲明一下:我們這次用的是STC89...

2022-01-14 14:01:34 7

7 ,信號端口優選上拉電阻,上拉電阻時,在待機狀態下,源端常為高阻態,不加上下拉,輸入導線呈現天線效應,一旦管腳受到輻射干擾,管腳輸入狀態極易被感應發生變化。下拉電阻:平常狀態輸入表現為低電平,但輻射干擾進來后,會通過下拉電阻泄放到地,就會發生一個從 Low——Hight 的跳變,容易產生誤觸;上拉

2022-01-14 14:06:35 31

31 前言:在一張原理圖中無論時上拉還是下拉都是非常普遍的,轉載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉

2022-01-14 14:07:36 22

22 (上拉下拉電阻)所謂上拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與電源VCC相連,固定在高電平;同理下拉電阻就是:將一個不確定信號(高或低電平),通過一個電阻與地GND相連,固定

2022-01-14 14:08:36 7

7 前言:RS-485總線廣泛應用于通信、工業自動化等領域,在實際應中,通常會遇到是否需要加上下拉電阻以及加多大的電阻合適的問題,下面我...

2022-01-26 17:07:50 13

13 上下拉電路一般在IC內部就已經做好,外部可以不加,如果外部添加,要與IC手冊中的上下拉特性一致,TCK和TRST引腳有可能會不同,TDI和TMS都是上拉。TDO在IC內部都是浮空,由于TDO都是連接TDI,因此可以加上拉與TDI一致。

2022-11-03 10:46:05 3002

3002 “上下拉電阻應用很簡單嗎?”那可不一定。電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。一般情況下,元器件需要上下拉的地方,加4.7K或10k,3.3K也行,甚至1K也可以,不會考慮太多。

2022-11-23 15:27:15 1509

1509

電路中有下拉電阻和上拉電阻,下拉電阻是把電阻的一端接地,把另一端的電位拉低,上拉電阻相反,電阻的一端接電源,把電阻另一端的電位拉至電源電位,那為什么需要上拉下拉電阻呢

2022-12-13 09:35:08 690

690 在這么原始的邏輯電路中就已經出現了上下拉電阻,這里面的原理也非常簡單粗暴:利用開關的閉合(電阻為0)和開啟(電阻無窮大)的特性,配合電阻,就可以輕松實現兩種電壓的輸出。

2023-02-20 09:26:14 1055

1055 下拉就是接地,上拉就相當于升壓,提高驅動能力或者穩定性。 上拉電阻是用來解決總線驅動能力不足時提供電流的問題的。一般說法是上拉增大電流,下拉電阻是用來吸收電流(抵抗干擾)。 上拉是將電壓拉高,下拉

2023-02-23 16:20:02 1234

1234 電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻。

2023-03-17 15:51:07 2538

2538

“上下拉電阻應用很簡單嗎?”那可不一定。電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。一般情況下,元器件需要上下拉的地方,加4.7K或10k,3.3K也行,甚至1K也可以,不會考慮太多。

2023-03-17 16:32:38 705

705

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2023-05-31 13:57:02 1293

1293

電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻,這兩者統稱為“拉電阻”,最基本的作用是:將狀態不確定的信號線通過

2023-06-10 14:17:53 1949

1949

上拉和下拉電阻是許多數字電路的組成部分。了解什么是上拉電阻或下拉電阻很重要?為什么將其用于數字電路?以及如何選擇這些的價值?本文將回答這三個問題,并讓您更好地了解它。

2023-06-18 15:25:17 3068

3068

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號

2023-06-29 17:04:31 7619

7619

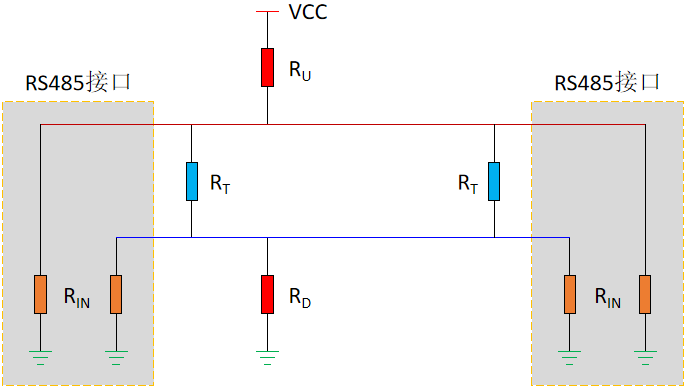

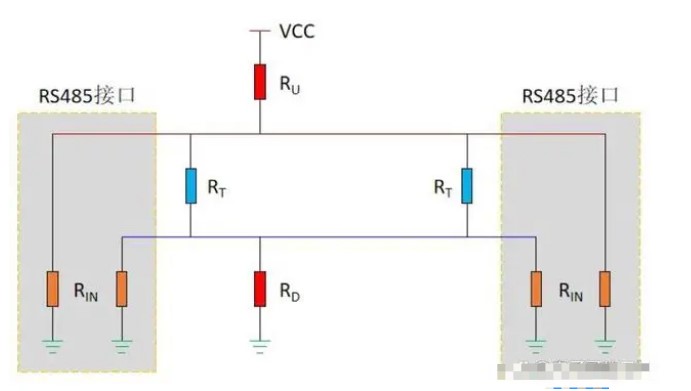

在A和B兩條線上加上下拉電阻,以及加多大的電阻合適。本文將對這個問題進行分析和解釋。485總線是如何工作的?首先,我們需要了解485總線的工作原理和信號特性。根據RS-48

2023-09-08 08:22:30 703

703

上下拉電阻應該與485收發器的輸入阻抗、終端電阻、總線長度、節點數等因素相匹配,以保證總線的阻抗匹配和信號完整性。 首先,我們針對收發器處于斷線的狀態時,此時收發器A、B電壓由RU、RT、RD和RIN共同決定。

2023-09-29 11:23:00 678

678

當使用上拉電阻和下拉電阻時,你需要理解它們的具體應用和原理以確保正確配置引腳,維持電平狀態,并避免電路問題。以下是更詳細的解釋:上拉電阻:作用:上拉電阻用于保持引腳的電平在邏輯高("

2023-10-30 08:00:54 661

661

電阻是如何實現上下拉功能的呢? 上下拉功能是指在電路中通過連接電阻來實現對信號的上拉和下拉控制。在數字電路中,上拉和下拉功能通常用于控制輸入端的電平狀態,確保輸入端在沒有外部信號輸入時能夠保持穩定

2024-02-04 09:32:18 159

159

電子發燒友App

電子發燒友App

評論