? ? ? ?一.前言

? ? ? ?造成IR違例的原因分以下三類:

? ? ? ?1.電流I大,這個和cell的選取(驅動能力,Vt類型)以及設計(翻轉率,是否同時翻轉等)相關;

? ? ? 2.電源網絡電阻比較大,可能是弱連接(缺孔,power net密度不夠等)導致;

? ? ? 3.電流和電源網絡電阻相乘結果比較大。

? ? ? ?對于后端工程師,如果說對電流大小能夠控制的措施不多,電源網絡電阻或者阻抗是可以在項目前期評估,選出比較合理的方案。本篇主要聊電源網絡背后的一些理論。

? ? ? ?電源網絡在設計的時候有兩個主要的目標:

? ? ? ?2.占用最少的繞線資源.

? ? ? ?為了讓晶體管獲得盡可能接近的供電電壓,必須:

? ? ? ?1.控制IR drop;

? ? ? ?2.控制di/dt響應。

?

? ? ? ? 二.簡化的電源網絡

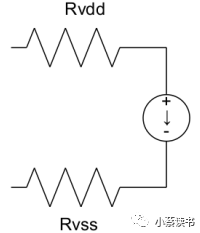

? ? ? ?為了最大限度地提高cell利用率,設計的電源網絡必須最大限度的減少繞線的congestion和整體面積的消耗。任何電源網絡都有電壓損失和電流需求。在滿足器件、電路和系統在其規格范圍內正常運行的要求的同時必須限制電壓損失。下圖中的電路演示了電源網絡中的 IR 壓降現象。

? ? ? ?Rvdd 和 Rvss 代表電源和接地網絡的電阻。電阻是金屬線(metal wire)電阻和互連(interconnect)電阻的總和。當設計電源網絡時,最小化電阻通常是首先要考慮的。上圖中的電流源是一個變量,代表了設計中物理單元的電流消耗。這個電流由AC和DC分量組成,且有效電流隨時間變化。因此,電阻兩端的電壓會發生變化,反過來,器件上的電壓也會發生變化。除了為器件提供盡可能多的電壓之外,還必須限制這種變化。

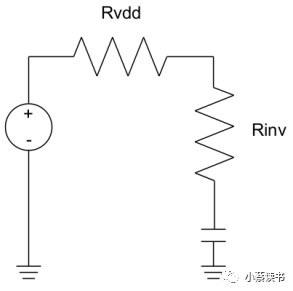

? ? ? ?下圖是一個RC電路,在其設計中包含了電源網絡電阻對瞬態電壓響應的影響。電源網絡的電阻 Rvdd 和反相器的固有電阻 Rinv 串聯,加上器件和接地網絡的集總電容。

? ? ? ?電源網絡任何電阻的增加都會導致整個電路響應的減慢,反相器的開關性能下降。優化電源網絡時,您必須最小化 Rvdd。

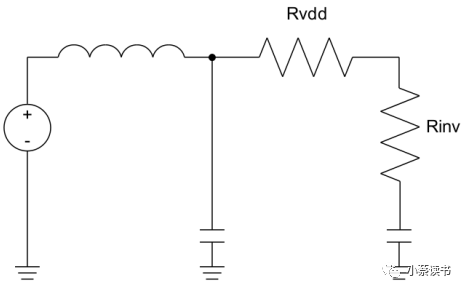

? ? ? ?除了IR壓降和反相器充電現象外,下面模型開始考慮設計中 di/dt 響應。因此,您必須考慮電感效應,這會將簡化的電源網絡轉變為復雜的電源網絡。

?

? ? ? ?三.?電壓、電容、電感、電流

? ? ? ?1.電壓注意事項

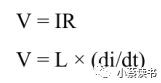

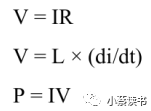

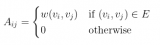

? ? ? ?以下兩個方程是計算電壓時考慮的因素:

? ? ? 電阻是電源網絡電壓損失的主要原因。電源網絡中的電阻越高,網絡中的電壓降就越大,從而導致到達給定器件的電壓更小。因此,器件必須承受足夠大的電壓,以便有足夠的電流。限制 IR 壓降的目標是針對設計的平均電流要求提供足夠的電流。

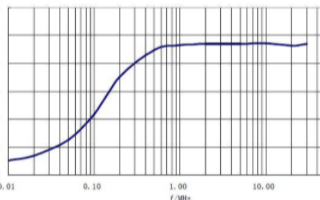

? ? ? ?還必須考慮電感效應。所有設計在信號和電源或地面網絡都具有片上電感。高頻和高功率密度設計使電感影響在亞微米技術節點上越來越重要。大信號電阻在低頻時可以支配阻抗并減輕電感效應。由于低電阻、高頻率和高電流的組合,電感效應會影響電源。

? ? ? 2.電流注意事項

? ? ? 每個設計都有電流需求的變化,即電流隨時間變化。時變電流會改變電阻器兩端的電壓。電感也起作用,但您必須考慮電流需求的變化。存在的總電流是時變電流加上靜態電流設計的漏電流。

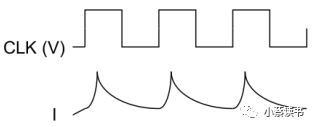

? ? ??下圖顯示了包含上升沿觸發的時序和組合元素的典型模塊的最終電流波形與時鐘的關系。時鐘上升沿對應的峰值信號電流是正在導通的開關器件的總和。

? ? ? ?必須提供足夠的電流以滿足信號切換要求。將峰值電流計算作為連續供電目標是過度設計。一個好的設計實踐是:

? ? ? ?1.滿足平均電流要求;

? ? ? ?2.以恒定電源的平均功耗要求為目標;

? ? ? ?3.在需要的地方分配裕量以滿足峰值電流和功耗的動態需求。

? ? ? ?電源網絡的設計考慮了 IR 壓降和電感效應或 di/dt。IR 壓降考慮針對平均電流要求,di/dt 考慮針對瞬時電流要求。

? ? ? ?3.電壓和電流的關系

? ? ? 必須注意電壓和電流之間的關系。以下等式顯示了電壓和電流的相互依賴性:

? ? ??電源網絡的 IR 壓降考慮旨在提供設計的平均電流要求。

?

? ? ? ?4.電容注意事項

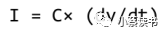

? ? ? ?電容是電荷存儲器件,它們可以提供電流。當電流從電容器放電時,電壓降為:

? ? ? ?可以在幾個主要位置找到電源和地之間的寄生電容:

? ? ? ?1.在金屬電源線和地線之間;

? ? ? ?2.在N阱和襯底之間;

? ? ? ?3.在器件之間。

? ? ? ?通常,去耦電容被添加到模塊中以提供該瞬時電流。此步驟減少了直接從電源網絡汲取的功耗。

? ? ? 5.電感注意事項

? ? ? 電感僅在存在時變電流時影響電壓。在開關活動期間存在時變電流。任何開關信號都將電流從輸入通過電源網絡傳送到輸出。此步驟創建一個電流回路。電感L與該回路的面積 A 成正比。可以通過最小化該回路的面積來最小化電感。

? ? ? 6.整體電源網絡

? ? ? ?一般整個電源網絡由二維網格組成。頂部網格是頂部兩層 M(top) 和 M(top-1) 上的粗粒度(course-grain)網格。該網格解決了 IR 壓降。下面的網格是 M2 和 M3 上的細粒度(fine-grain)網格,滿足設計的 di/dt 要求。上下網格中的每一層都包含電源和地straps。這些straps必須均勻分布。每個網格層之間的通孔的頻率取決于設計的功耗密度。

?

? ? ? 四.電源網絡怎么處理 IR Drop、EM、di/dt、電感的?

? ? ? 1.解決 IR Drop

? ? ? 一般推薦使用兩個厚的頂部金屬層來充分解決電壓 (IR) 降。這些層是 M(top) 和 M(top-1)。它們很寬,提供高電容和低電阻,這對電力網絡都是有利的。目標是用這兩個金屬層完全解決所有 IR 壓降。

? ? ? ?具有高速和高功耗密度的設計可能需要更多層來滿足 IR 壓降要求。即使使用工藝允許的最厚和最寬的頂部金屬,設計也可能需要更多層。這些設計可能需要將 M(top-2) 添加到上部網格。設計可能仍不滿足 IR 壓降要求。可以將 M(top-3) 重復添加到上格以滿足 IR 壓降要求。

?

? ? ? ?2.解決EM

? ? ? ?可以在上下網格上使用間隔緊密的窄straps,以幫助防止 EM。在典型的設計中,與較不頻繁地放置較寬的straps相比,更頻繁地放置窄straps會阻止更少的布線資源。較寬的金屬比窄金屬更適合 EM,因為寬金屬的電阻較小。如果放置許多窄straps,平行線的總有效電阻小于較寬、頻率較低的帶的有效電阻。

? ? ? ?通常,上部網格用于 IR 壓降,下部網格用于 di/dt。設計階段與 EM 指南一起確定所需straps的數量、寬度和頻率。如果這些網格是完整的,但您仍然無法滿足 EM 準則,可以執行以下操作:

? ? ? ?1.對于當幾個單元緊密放置時在高驅動單元周圍發生的局部 EM 問題,請在下部網格上添加額外的straps。這些高驅動單元的優點是引腳密度低,并且不會阻塞很多本地繞線資源。

? ? ? ?2.對于高驅動單元中的 EM 問題,放置一個簡單的totem pole。將 VIA 放置在上部網格、下部網格和可選的單元電源軌之間,從頂部網格向下。

? ? ? ?3.對于全局 EM 問題,您必須使用類似于解決 IR 壓降問題的方法解決頂部網格。為了滿足 EM 要求,如果頂部網格的層不能更窄和更緊密地間隔,則使用更多層。

?

? ? ? ?3.解決?di/dt

? ? ? ?一般建議在 M2 和 M3 上使用細粒度網格,以滿足設計的瞬時電流要求。設計可以從頂部電源網格中提取此電流。但是,此步驟可能會導致延遲,因為電流必須通過過孔進出頂部的兩個金屬層。這個較低網格的參考目標是防止邊緣率下降超過 10%。這種退化是解決 di/dt 的主要問題。提供這種較低的網格可以更快地訪問存儲在設計中的寄生電容和去耦電容中的電流。盡管較低的金屬層比頂部網格中的層更窄(寬度和厚度),但要通過的過孔更少。因此,總電阻小于從頂部網格汲取電流時的電阻。然而,下金屬層電阻可以大于上金屬層。

? ? ? ?straps之間的距離越小,di/dt 響應越好。將這些straps彼此靠近放置,以便在各個方向上快速到達更多電容位置。然而,下部網格的間距絕不能比單元本身內包含的電源軌更緊密。如果這個網格太緊,就會阻塞太多的繞線資源。

? ? ? 4.解決電感

? ? ??電感隨著電流返回路徑的面積而增加。可以通過以下方式最小化當前返回路徑的面積:

? ? ? ?1.在下部網格上均勻分布straps;

? ? ? ?2.在下部網格上緊密間隔straps。

? ? ? ?這些步驟提供了規則和附近的電流路徑以減少電感。均勻分布的straps還可以減少局部繞線擁塞。雖然寬線的電阻比窄線低,電感通常較大。

?

? ? ? ?五.電源網絡總結

? ? ? ?最有效的電源網絡由兩個電源網絡組成,一個上電源網絡和一個下電源網絡。每個網格由兩個正交方向的金屬層組成。

? ? ? ?下面總結了上面的網格:

? ? ? ? 1.解決 IR Drop;

? ? ? ? 2.解決全局EM ;

? ? ? ? 3.使用頂部厚金屬層。

? ? ? ??下面總結了下面的網格:

? ? ? ? 1.解決di/dt;

? ? ? ? 2.解決局部EM;

? ? ? ? 3.解決信號電感;

? ? ? ? 4.使用較低的薄金屬層。

?

審核編輯:劉清

電子發燒友App

電子發燒友App

評論