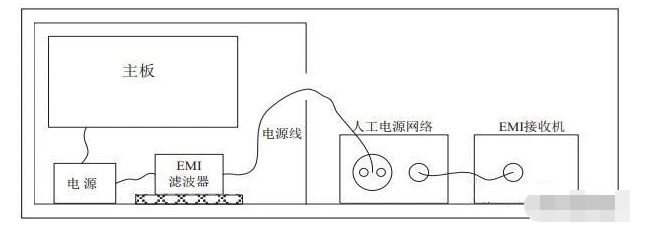

本文介紹電源濾波器的作用、原理、要求和步驟,以及一些設計的技巧和注意事項。

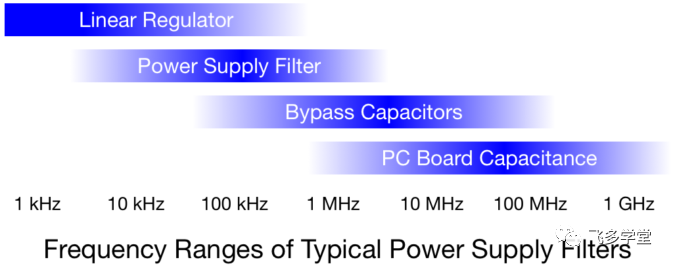

高頻紋波會直接穿過線性穩壓器。紋波來自開關電源、數字電路和無線電干擾。在頻率高于 10 kHz 時,大多數線性穩壓器開始失效。分布在芯片之間的小旁路電容在約1MHz時開始有效。由電感和電容組成的低通濾波電路,可以去除10kHz到1MHz之間的紋波。

一個好的電源濾波器可以由一個電感和一個阻尼電容組成。這被稱為LC濾波器。也有可能使用更多或更少的元件設計其他類型的濾波器。設計過程是首先是電感選型,然后圍繞它設計濾波器。如果不能設計出一個可接受的濾波器,就要找出電感的問題所在,選擇一個更好的電感,然后重試。

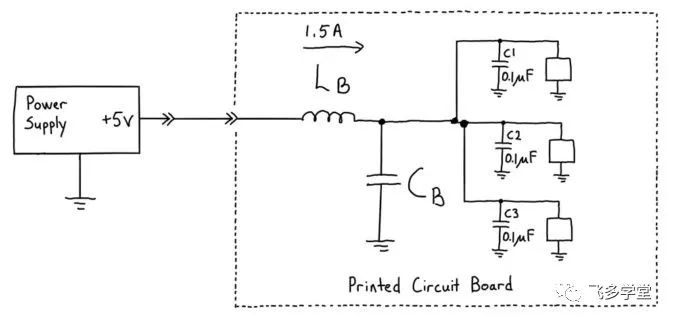

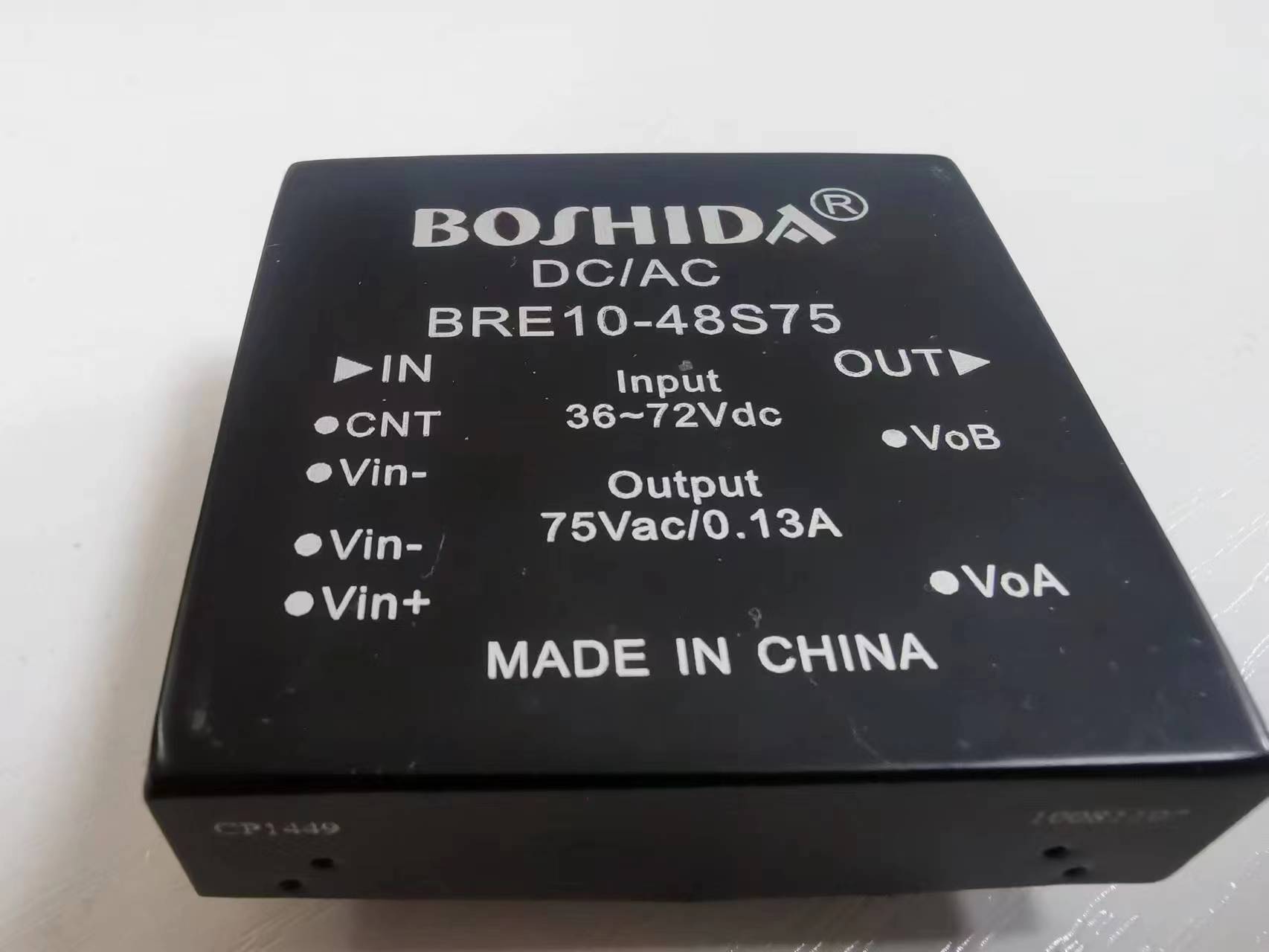

在上圖的簡單設計中,假設電源穩壓器是在板外,通過連接器輸入一個穩定的電壓。當有一個本地穩壓器時,設計更簡單,有時可以減少電源濾波器。

電源濾波器在穩壓器后面,所以它需要有一個低的直流電壓降。電感的數據表有一個直流電阻的值。電壓降大約是這個電阻乘以電流的20%多。額外的20%是為了考慮到在高溫下電感的銅線電阻的增加。

電感選型

濾波器所需的電感值不太難計算。它應該比與電源串聯的所有其他電感大約大十倍。如果電源中沒有其他的電感或鐵氧體珠,這個電感是由于電纜和印刷電路板走線造成的。計算這個電感的不太準確的近似方法是取電源傳輸的最大長度,然后乘以每毫米1nH。電源平面的電感要低得多,對于這個計算,可以忽略電源平面路徑的長度。

在這個例子中,我想使用一根 300mm 的電纜為 PCB 供電,PCB的尺寸是大約100mm X 100mm。一個寬裕的總長度是500mm,這意味著我的電源分配電感大約是500nH。為了讓電源濾波器的電感比這個大十倍左右,我選擇了一個10uH +/- 30%的電感。額外的電感是為了考慮-30%的公差。除了初始的公差之外,電感值隨著電流的增加而下降。這個電感,當流過它的電流是 2.4安培時,電感值會下降 35%。

我選擇了Bourns SRU1028系列的電感。它有低高度,自屏蔽,而且容易獲得。我通過在Digi-Key上搜索一個低成本、至少2安培電流等級的10uH電感來找到它。

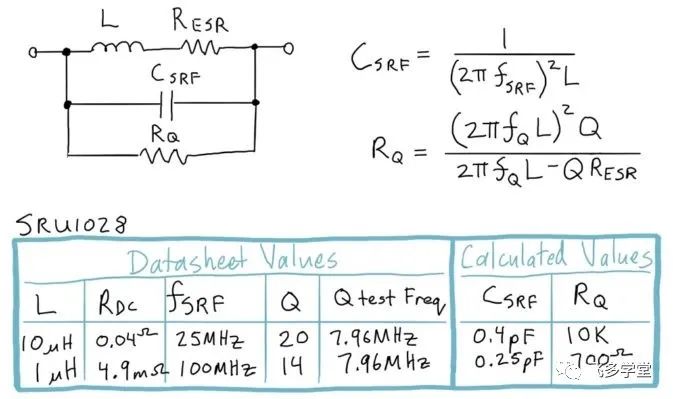

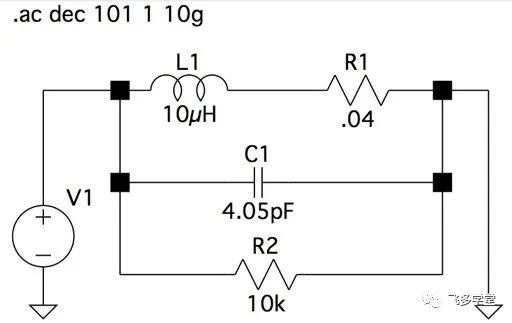

下圖是此型號的電感模型:

上圖的電感模型使用了四個元件。電感L和數據表上的L相同。串聯電阻RESR和數據表上的RDC相同。RQ和CSRF的值是根據數據表上的fSRF,Q和Q測試頻率計算出來的。

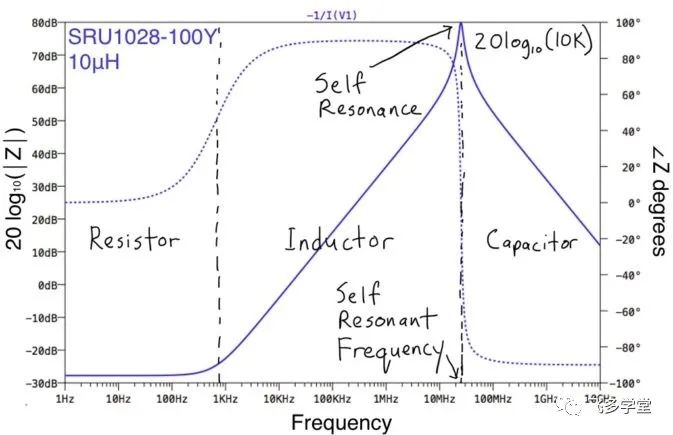

這些額外的元件使得電感具有上圖所示的阻抗特性。實線曲線是阻抗的分貝幅值,虛線曲線是阻抗的相位角(phase angle)。在1kHz以下,電感表現為一個小電阻RDC。在1kHz以上,它表現為一個電感,直到接近自諧振頻率(SRF)。在SRF附近的一小段頻率范圍內,電感表現為一個大阻值電阻,其值為RQ。在SRF以上,電感表現為一個電容CSRF。

從這里開始,使用電路仿真潤建可以節省時間。免費的模擬器LTspic使用下圖的仿真原理圖創建了上圖的電感阻抗圖。

電源 V1 是 1V 交流電源。阻抗可以用-1/(i(V1))這個表達式來繪制。

電容選型

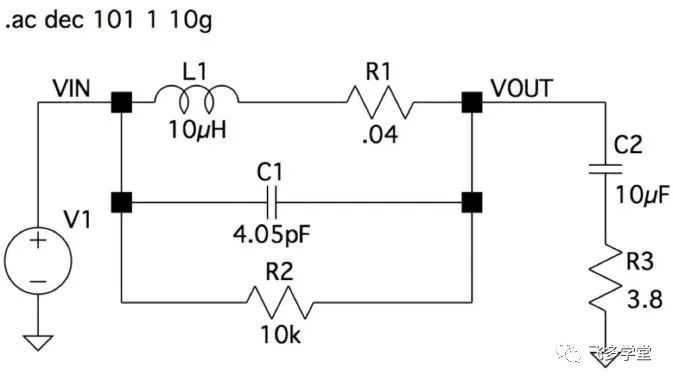

將上面的電感模型原理圖圖轉換為低通濾波器非常容易,只需在原理圖中添加一個電容即可。我選擇了Kemet電容,型號是 T491A106010A,這是一個10uF極化鉭電容,最大等效串聯電阻為3.8Ω,額定電壓為10V。

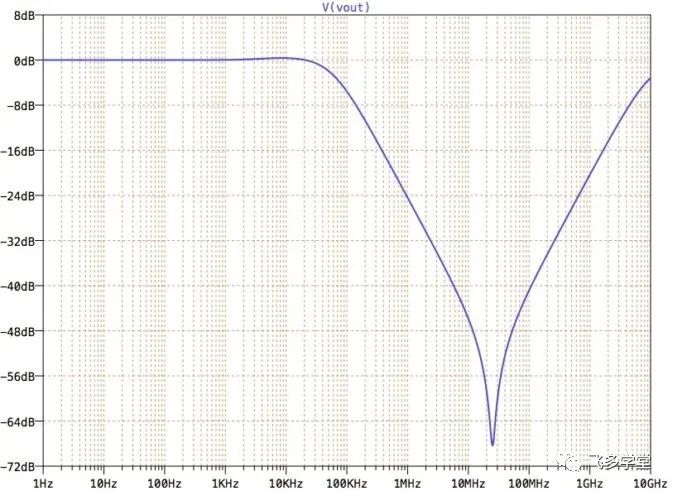

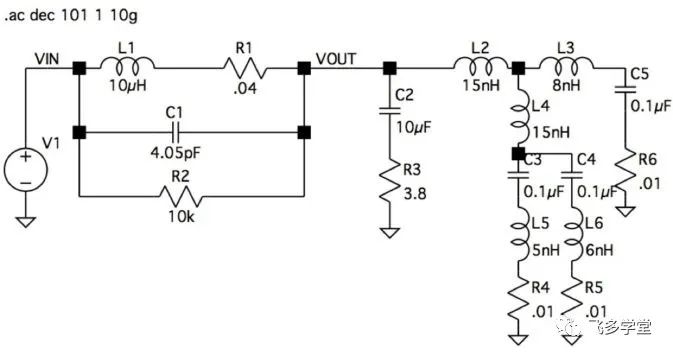

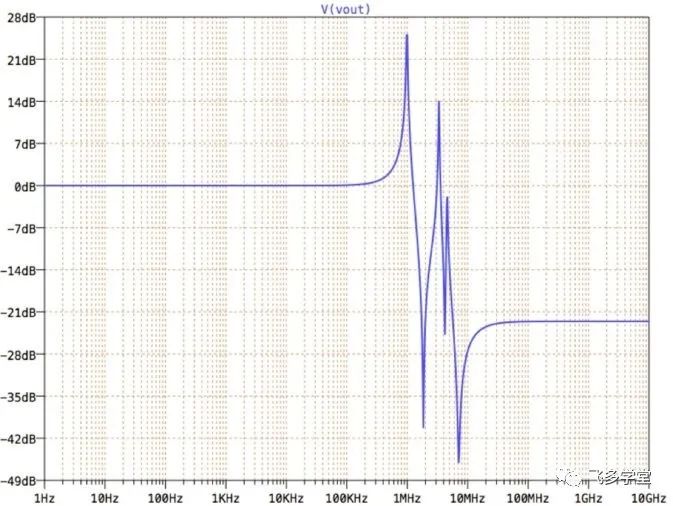

這個濾波器的頻率響應是V(VOUT)/V(VIN),但由于在仿真中V(VIN) = 1,所以我們直接看V(VOUT)的輸出曲線是一樣的。

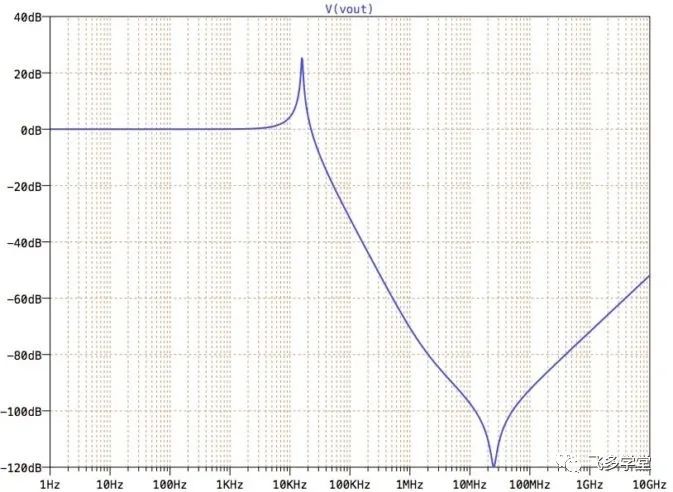

高Q值、低ESR的陶瓷電容已經在許多應用中取代了鉭電容。接下來,我嘗試了使用低ESR的陶瓷電容進行模擬,而不是使用鉭電容。

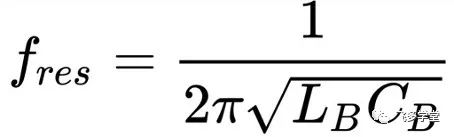

15.9kHz的峰值是LB和CB的共振。共振就好像我們唱歌時,當我們唱到某個特定的音高時,聲音會變得更響亮。在這里,LB和CB就像是一個共鳴箱子,當它們受到15.9kHz的聲音波動時,就會共振并發出更強的聲音。

這個頻率下的電源紋波會增加而不是減少。由于這種共振的頻率范圍很窄,所以在測試中很容易忽略這種共振的影響。LB和CB的值有較大的公差,而且隨著時間和溫度的變化而漂移。為了解決這個共振問題,可以增加一個串聯電阻。一個好的阻尼電阻值的初步估計是:

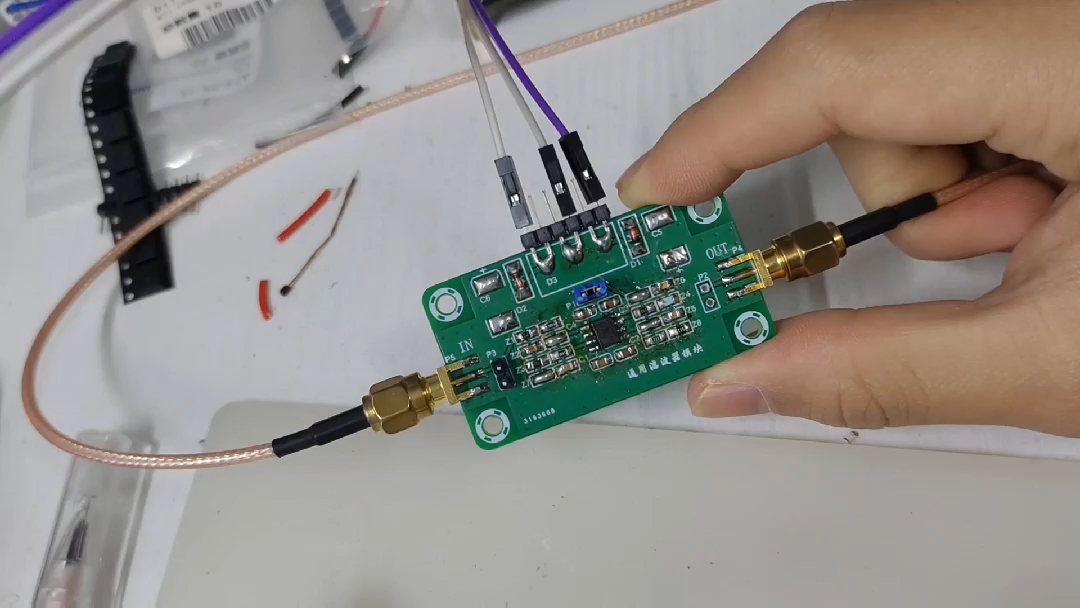

使用電路仿真軟件來找到第一個共振點,并調整電阻值來找到最佳的阻尼值。陶瓷電容和電阻是比鉭電容更可重復的設計。這是因為鉭電容的ESR可能有很大的取值范圍。

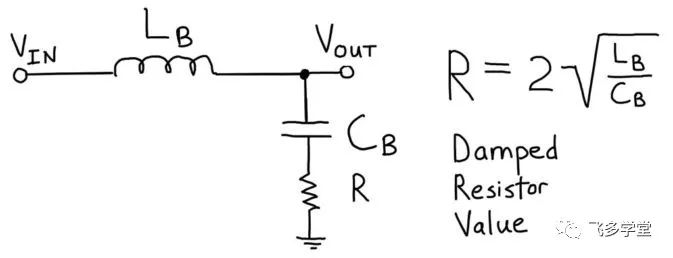

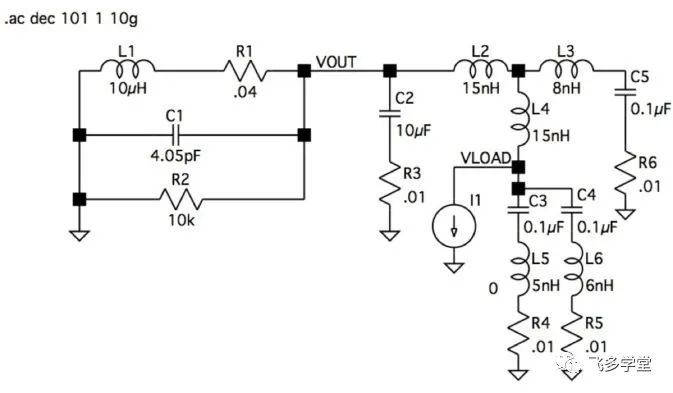

負載網絡建模

到目前為止,這個例子沒有負載阻抗或負載電流。要看看這個濾波器在電路板上的效果,模擬需要包括印刷電路板走線電感和旁路電容。在高于100MHz的頻率下,傳輸線效應進一步復雜化了模型。下一個電路例子有一個簡化的模型,代表了PC 板電源中常見的負載。你可以查看你自己的電路,用每毫米1nH的粗略電感近似來估計走線電感。更準確的模型可以用一個功率完整性(PI)CAD工具來制作。

這些替代走線的電感在電力分配網絡中表現為額外的諧振(resonances )。

當負載表現為電感和電容時,仿真波形會多出一些額外的諧振(resonances)。盡管有這些諧振,這個濾波器的性能仍然很好。濾波器的整體形狀得以保留,因為電感比小負載電感的總和要大得多,而阻尼電容比旁路電容的總和要大得多。

這個電路板和真實的電路仍然有一些區別。由于傳輸線效應,真實世界的電路在100MHz以上的頻率下會有不同的響應。另外,其他小電和電感也變得重要,特別是在500MHz以上的頻率下。

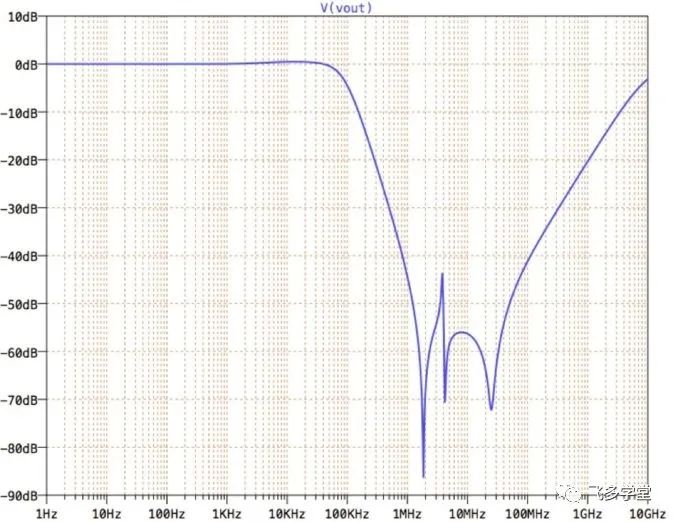

如果沒有電源濾波電路,或者使用一個大的沒有阻尼的電容,會導致像這樣的諧振:

負載電流

當我們使用電源給負載供電時時,有些負載會頻繁地需要不同電流,而這種電流會導致電源電壓不穩定。為了解決這個問題,我們需要使用一種叫做旁路電容的東西。旁路電容可以儲存電荷,當設備需要電流時,它可以提供瞬間的電流。脈動負載的一個例子是處理器進入和退出低功耗睡眠模式。

但是,有時候旁路電容會和電源網絡中的電感產生共振。這就好像我們唱歌時,聲音會在房間里反射出來,導致聲音變得更響亮。為了解決這個問題,我們需要在電源輸入處加入一個過濾器來減弱這種共振。就好像我們在唱歌時,如果我們把房間的門窗關上,聲音就不會反射出來,變得更加柔和。

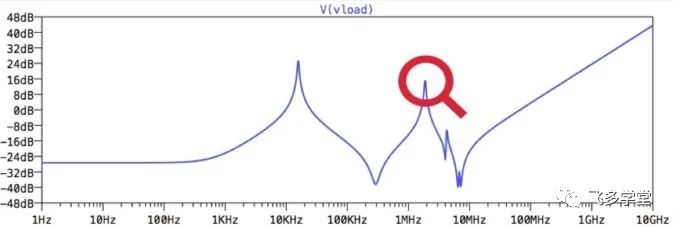

旁路電容還可以與電源分配網絡中的電感共振。在電源輸入濾波器處阻尼共振并不能保證所有由負載電流引起的共振也會被阻尼,但通常會有所幫助。為了演示潛在問題,這里是未阻尼(R3 = 0.01歐姆)版本的濾波器,其中一個負載點有一個交流電流源。

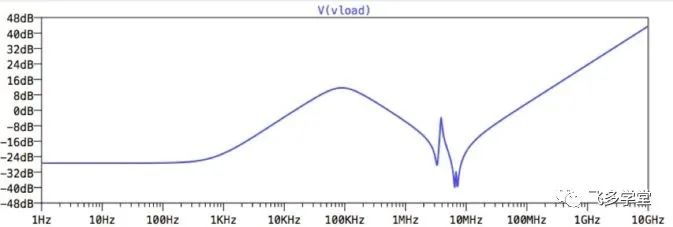

VLOAD處的阻抗為v(VLOAD)/i(I1)。由于I1中的交流電流設定為1,所以阻抗就是v(VLOAD):

上面的無阻尼共振頻率為1.87兆赫。這是一個脈沖負載會引起問題的一個頻率。

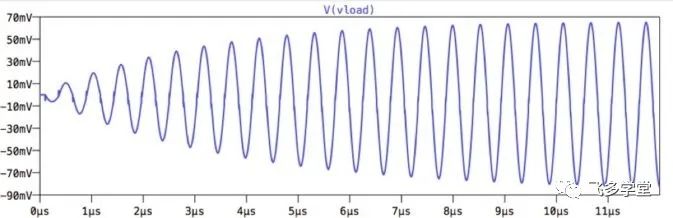

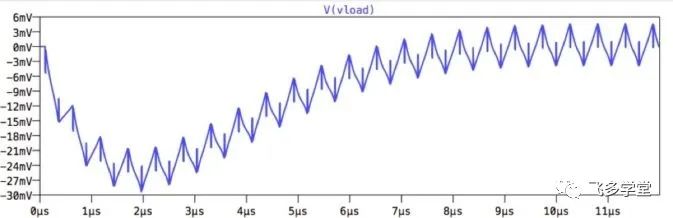

我用上面示意圖中顯示的脈沖電流源模擬了脈沖負載。這個例子顯示了幅值為20mA、周期為535ns的脈沖。當脈沖電流源的周期與共振頻率的倒數相等時,電壓擺動最大。

在這個例子中,紋波電壓的正弦波形是電力分配中未阻尼、高Q值共振的典型特征。未阻尼共振作為一個濾波器,將電流脈沖轉化為正弦電壓波形。

如果在仿真結束時電壓仍在增長,請增加仿真時間以找到最大值。更尖銳(更高的Q因子)的共振需要更長時間來穩定下來。

在睡眠模式電流脈沖的例子中,軟件的改變會導致脈沖的頻率發生變化。由于共振引起的大幅度電壓波動只有在睡眠周期與共振頻率相一致時才會發生。在開發過程中,這可能會導致一些神秘的錯誤,看起來是軟件相關的,但實際上是由硬件引起的。在生產過程中,元件的變化會使共振頻率發生偏移,導致生產問題。在使用過程中,溫度變化和元件漂移會使共振頻率發生偏移,導致產品失效。

下一個仿真波形顯示了阻尼版本,電阻R3設置為3.8歐姆。交流分析顯示,最大的兩個高Q共振已經被阻尼:

這改變了脈沖負載電流引起的形狀并降低了電壓波形。

這種三角波形是脈沖負載的典型特征。它是由局部旁路電容的充放電周期造成的。這種三角波的幅度可以通過增大旁路電容來減小。如果紋波波形看起來更像一個方波,那么它是由旁路網絡的電阻引起的,可以通過使用低ESR的旁路電容或更寬的走線來減小。開啟時的長而緩慢的脈沖是由100KHz處阻尼的低頻共振引起的。短暫的尖峰是10ns電流源邊緣的穿透,可以通過降低旁路電容路徑的電感來減小。大約4MHz處剩余的共振需要進一步模擬。

總結

通過使用正確設計的、帶阻尼的低通濾波器來避免電源分配共振。

電源濾波器的作用是去除電源上的高頻紋波,這些紋波可能來自開關電源、數字電路或無線干擾。高頻紋波會影響線性穩壓器的效果,導致電路不穩定或失效。

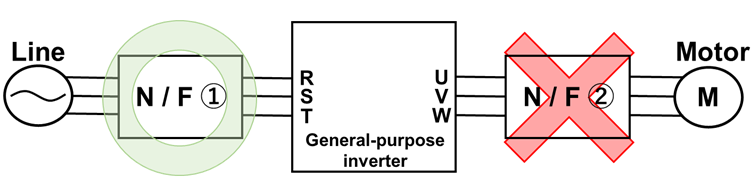

電源濾波器的原理是利用一個電感和一個電容組成的LC濾波器,形成一個低通濾波器,只讓低頻信號通過,而阻止高頻信號。LC濾波器的截止頻率和阻尼系數取決于電感和電容的值,以及串聯或并聯的阻尼電阻。

電源濾波器的要求是要有足夠大的電感值和電容值,以覆蓋10kHz到1MHz之間的頻率范圍,同時要有足夠小的直流壓降和阻尼電阻,以減少功耗和熱量。另外,還要考慮元件的公差、溫度漂移、寄生參數等因素,以保證濾波器的穩定性和可靠性。

電源濾波器的設計步驟是先根據電路的需求和條件,估算出所需的電感值和電容值,然后選擇合適的元件,并用電路模擬器進行驗證和優化。如果發現設計不合理或不滿足要求,就要重新選擇元件或調整參數,直到達到預期的效果。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論