在電源完整性方面,由于電源電壓越來越低,而電流需求卻越來越高,因此電源傳輸網絡(PDN)的設計變得非常重要,因為一個微小的電壓噪聲就會導致系統無法正常工作。另外,PDN 阻抗設計不足也會影響信號的完整性。在當前的電子產品中,為了確保良好的 PDN 設計,工程師們使用了大量去耦電容器來保證電源完整性,這些電容器在 PCB 和封裝中占據了大量位置。如何優化電容的位置和數量是工程師們經常面臨的問題。

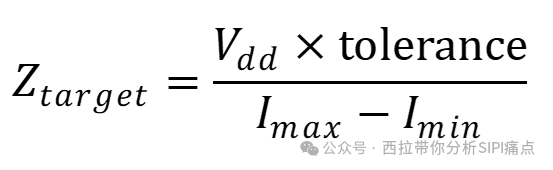

業界有很多關于去耦電容位置,容值以及數量優化相關的論文,但總體看來,論文的理論對于工程的幫助很有限,因其經常需要多次的3D Full wave仿真進行迭代和優化,對仿真時間,以及資源需求較多,因此對于工程的幫助有限。各大EDA公司也有相應的一些去耦電容優化方案,這些EDA公司所出的方案經常是基于仿真一次所獲得的S參數進行優化,這樣做的好處是優化速度快。但此等操作也有其弊端,類似陷入局部最優解,解的隨機性等等,但最重要的原因是,這些優化方式都是基于目標阻抗進行的。通常目標阻抗的定義為:

其中Vdd是供電電壓,Imax和Imin分別是最大和最小工作電流,tolerance是指器件在正常工作時所能承受的最大電壓的變化比例,比如說5%。而且目標阻抗的定義實際上是有很多假設在里面的,這個目標阻抗并不能完美的描述時域噪聲,類似SSN, Voltage Droop產生的機理, 它只是工程上一個很簡單的估算公式,所用的假設是PDN是一個純電阻,但事實上PDN 網絡設計中最重要的挑戰是電源分配網絡所產生的電感,其主要是由電流回路路徑而引起的,電感的阻抗會隨頻率升高而升高,過高的阻抗將會引起過大的電源噪聲,并且電感可以與電源網絡的寄生電容一起產生諧振,因此我們經常需要加入大量的電容來對阻抗曲線進行優化。?? ?

2 使用S2SPICE來優化PDN的電感

2.1 使用S2SPICE來抽取PDN的具有物理意義的等效電路?

如果我們可以確定電流回路路徑,那么對于PDN的設計來說,就可以對其電流回路路徑進行優化,通過降低電流回路路徑的距離來降低電感。遺憾的是,由于PCB設計的復雜性,工程師很難通過版圖來確定電流回路路徑,往往需要大量的仿真來對電流回路路徑進行確認。

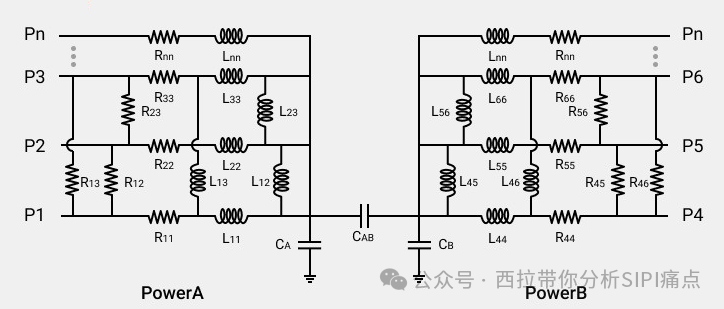

現在業界有一款特色的小工具,S2SPICE,其提出了一種對于PDN優化的新思路,能夠基于PDN的S參數生成其對應的具有物理意義的等效電路,這個提取的等效電路不僅可以用作全通路PDN時域瞬態仿真,而且提供了評估和優化PDN阻抗的一個新思路和新工具。S2SPICE提取的是一個典型的具有物理意義等效電路,如圖1所示:

?? ? 圖1:電源網絡的具有物理意義的等效電路

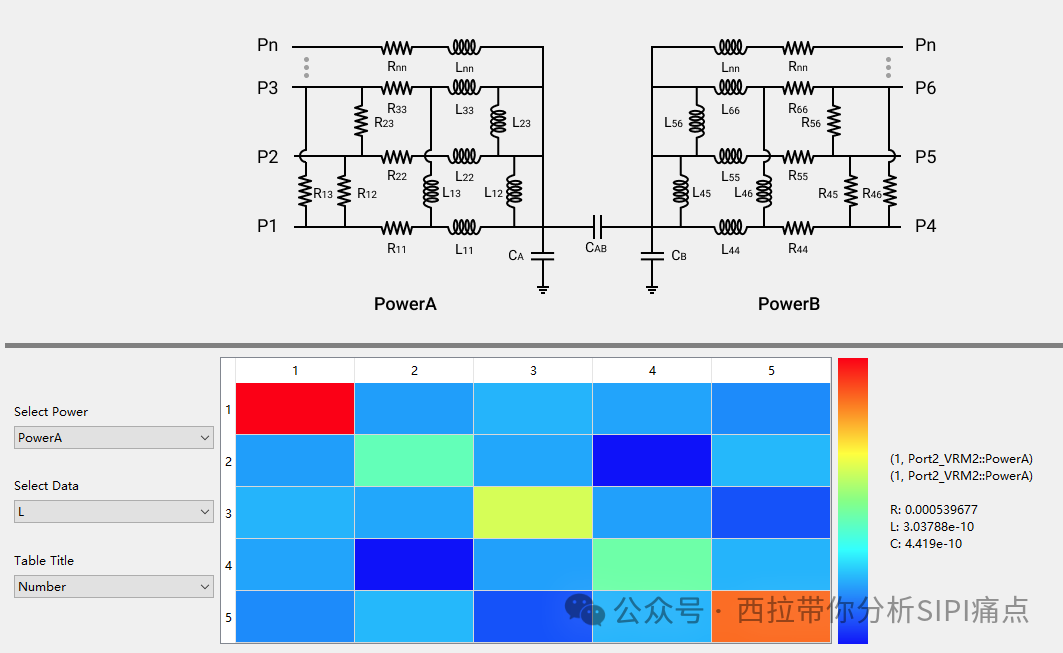

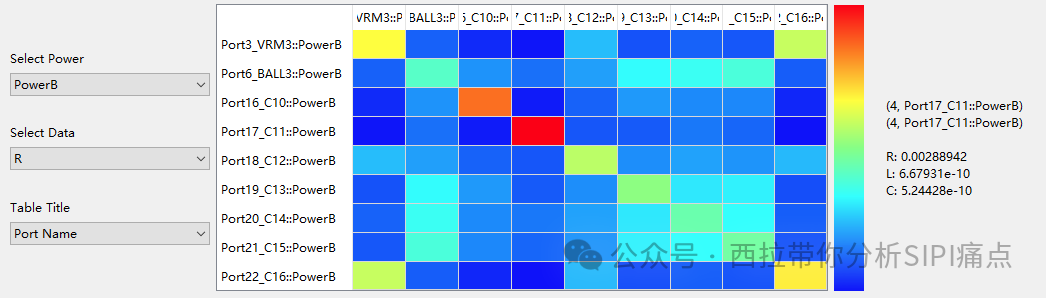

圖1展示了不帶有去耦電容的PDN等效電路網絡,其中Power A/B代表不同電源域的等效電路,P1…Pn?代表PDN仿真時的每個端口。它們可以是IC負載的電源端口,VRM的輸出端口,或去耦電容的端口。該軟件可以從PDN的S參數中提取出每個端口處的電阻以及電感。從剛剛的分析中,我們得知PDN的寄生電感對于PDN優化的重要性。因此,該軟件還集成了對于R map以及L map的顯示,可以輕松知道每個端口處的電感的大小以及其影響,以及最大最小的R, L。對于IC負載的電源端口來說,其相應的電感決定了PCB PDN對這個負載所能提供的最小阻抗的極限值,也就是決定了PCB層級下的PDN網絡的有效性;對于去耦電容端口來說,其對應的電感決定了這個去耦電容阻抗的大小,也就是決定了去耦電容的有效性。

圖 2 L map?? ?

圖 3 R map

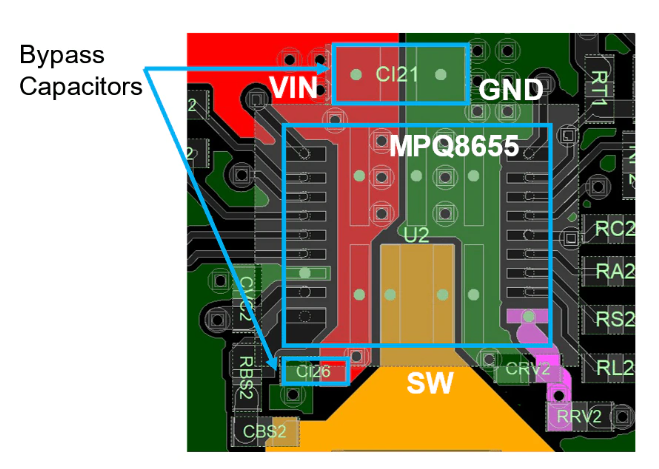

2.2 優化PDN的電感? ?

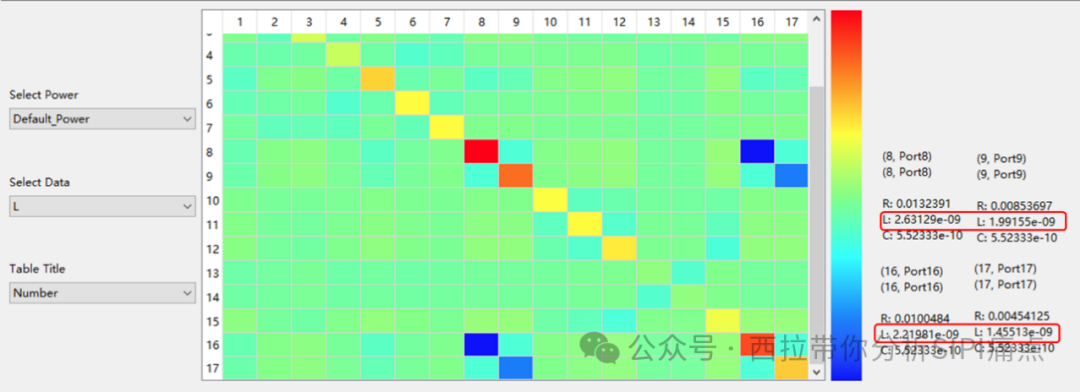

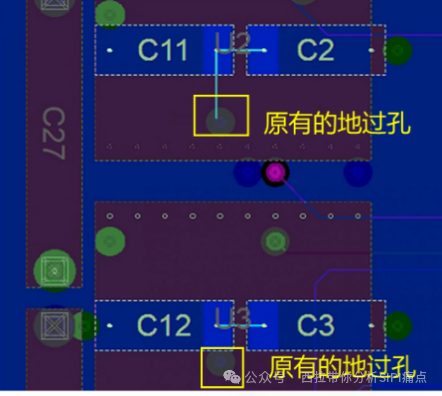

端口處電感的大小是PDN優化的一個重要指標 1:SI/PI工程師可以通過該結果來對封裝的ball map或者IC 的bump map進行重新布局,對電源和地pin腳的數量和位置排布進行優化,使較為重要的電源可以有較低的電感。 2:工程師可以通過端口的電感大小來決定在該端口附近所添加的電容類型,數量,大小等;也可以對電容處的過孔放置以及數量進行優化,越小的端口處的電感可以使電容更具有效性,因為放置電容所帶來的寄生電感ESL會和端口處的電感進行并聯,因此減少端口處的電感以及可以減少電容所帶來的寄生電感。 為此,我們準備了一個簡單的電容過孔優化案例作為示例。案例如圖4-1,原有的版圖設計將電容的地過孔放置于電容負極下方,距離電容pad較遠,并且兩個電容共用同一個地過孔,還用了很細的線進行連接,這種的連接方式并不友好,我們對原有電容處的地過孔進行了優化,在C2和C11電容負極pad處各自加入了兩個地過孔,在C3和C12電容負極pad處各自加入了一個地過孔。 先對案例原始設計進行仿真,一共17個端口,其中電容C2, C3, C11, C12分別對應第8,9,16,17個端口。仿真結果如由圖5所示,端口8,9,16,17處的電感分別為2.631nH , 1.991nH, 2.22nH,1.45nH。? ?? ? ?

圖5 仿真結果 – 優化前各個端口處的電感圖

? ?? 圖4 -1 原有的電源網絡版圖設計 ?

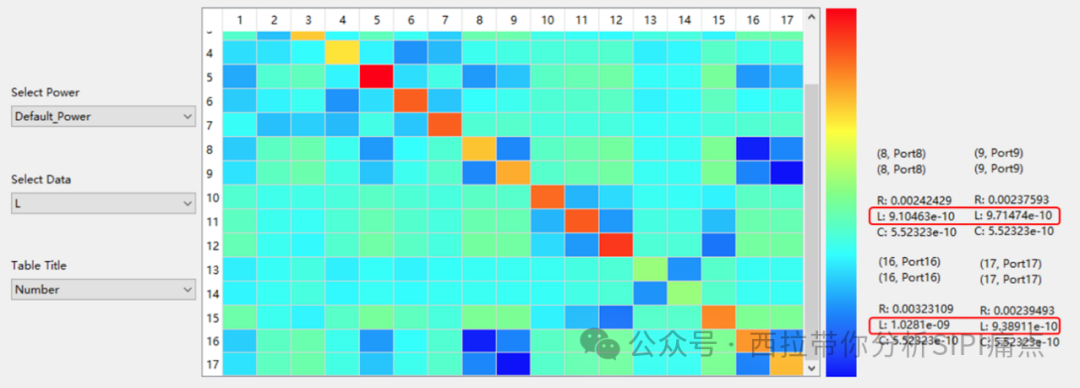

圖4 -2 優化后的電源網絡版圖設計 對優化后的設計進行再次仿真,結果如圖6 所示,可以看到紅色框標注port8(C2),port9(C3),port16 (C11) 以及 port17 (C12)處的電感比圖4中的電感小了很多。 ? ?

圖6 仿真結果 – 優化后各個端口處的電感圖 對比優化前后的結果,可以看到比較差的幾個端口電感均有明顯改善。

?

| ? | 優化前 | 優化后 |

| C2(Port 8) | 2.63nH | 0.91nH |

| C3(Port 9) | 1.99nH | 0.97nH |

| C11 (Port 16) | 2.22nH | 1.03nH |

| C12 (Port 17) | 1.45nH | 0.94nH |

?

此案例只是為了說明這種分析和優化的方法,實際的工程案例中,問題會更加復雜,要考慮的因素也更多,但是其原理基本相通 ,S2Spice可以幫助工程師快速定位問題,從而解決問題。

3 使用S2SPICE所提取的物理等效電路的限制??

3.1 PCB和封裝級的阻抗參數分析??

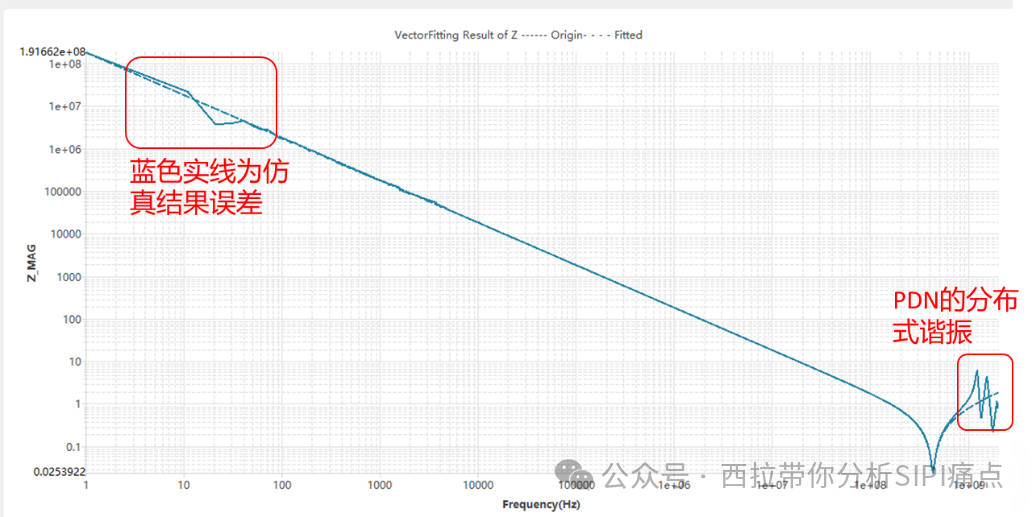

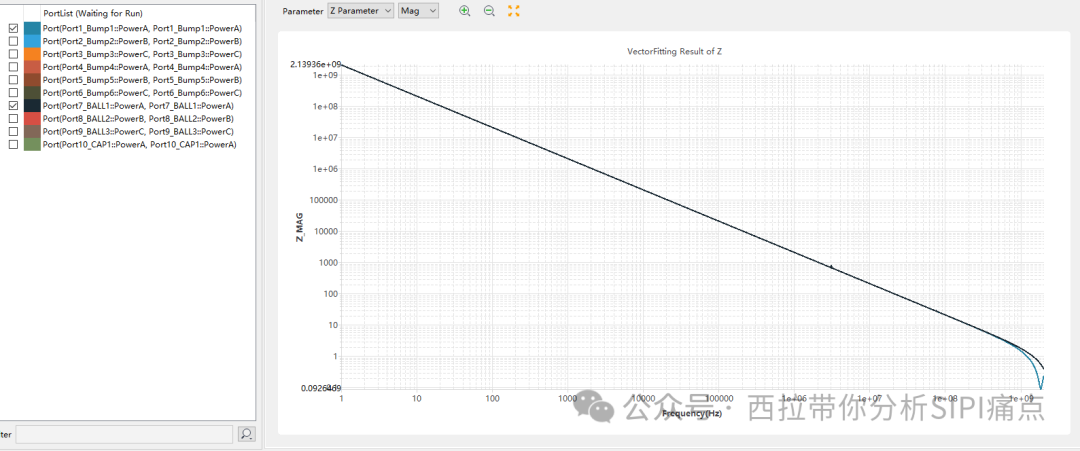

S2SPICE所提取的具有物理意義的等效電路對PDN網絡的分布式諧振無法進行處理,如圖7-1所示。也就是該等效電路對于不考慮高頻諧振的情況較為友好。而且大部分的板級PCB,并不是需要考慮特別高的頻率,因為比較高的頻率的PDN,它的噪聲是由封裝和芯片上的電容來決定的,那么到了PCB板級這邊,那我們的頻率并不需要那么高;再一個,即使對于封裝級,因封裝的尺寸也一般較小,其PDN結構(不含電容)的阻抗曲線一般在2GHz以內只有一個諧振點甚至一個諧振點都沒有,因此該諧振點較高,也可以用S2SPICE所提取的具有物理意義的等效電路來很好的描述,如圖7-2所示。?? ? ? ? ? ? ?

圖7-1:一階RLC等效電路阻抗曲線

圖7-2:封裝級阻抗曲線

抽取具有物理意義的等效電路只是S2SPICE中的一個功能,如果用戶對高頻的分布式諧振信息也很關注,S2SPICE也提供了傳統的矢量擬合的方法,也能處理大規模,大數量端口的擬合。

3.2 全通路時域瞬態仿真驗證??

PDN仿真除了頻域阻抗的仿真,最重要的一環是全通路的時域瞬態仿真。在工程實踐中,一般不直接使用S參數來做時域的瞬態仿真,因為通常會遇到不收斂的問題,使用S2SPICE提取的具有物理意義的等效電路可以有效的解決不收斂的情況。但是,S參數轉換成Spice模型的過程中,市場上的軟件很容易產生精度丟失。基于以上介紹,S2Spice在算法上做了很多創新,完美的解決了這個問題。

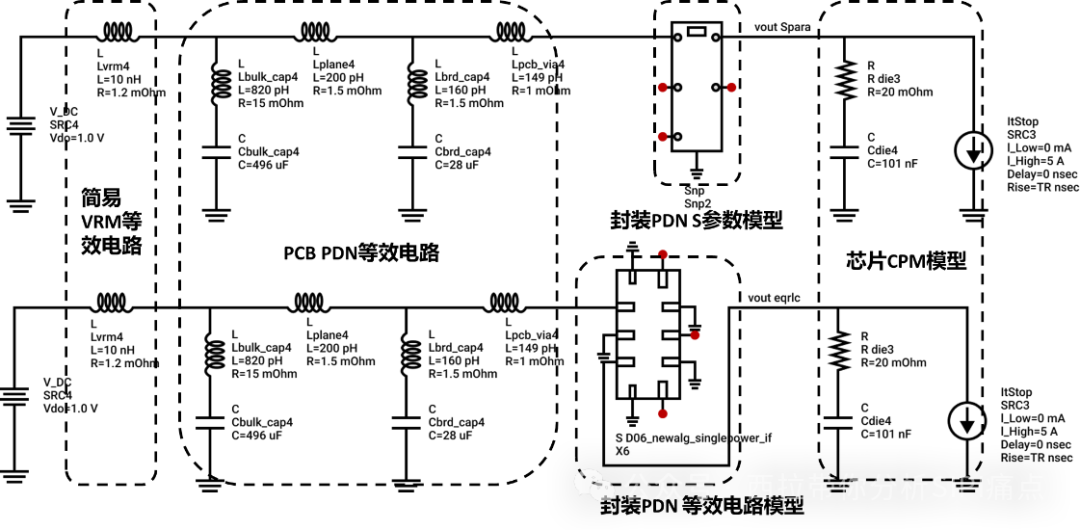

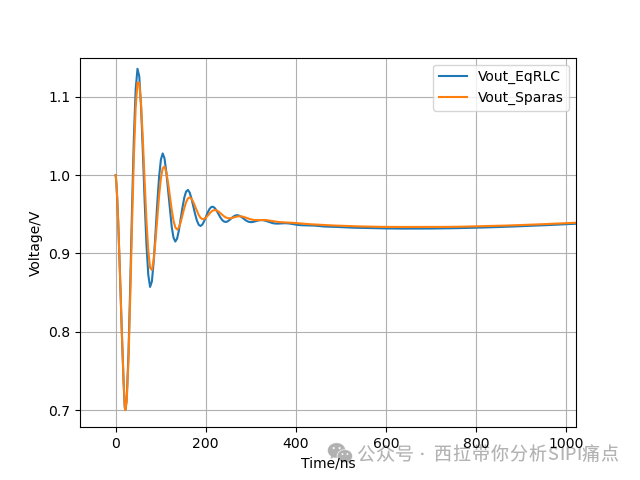

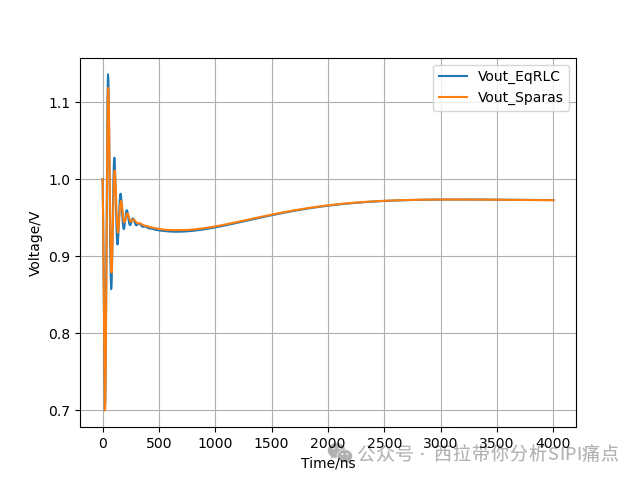

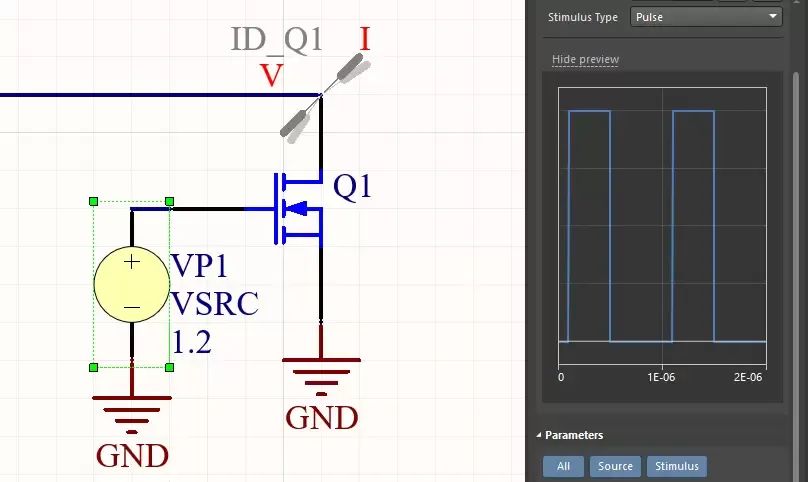

接下來,我們用一個實際案例來對比一下使用S2Spice所提取出來的等效電路和直接使用頻域S參數來進行時域仿真的結果,驗證其精度和準確度。

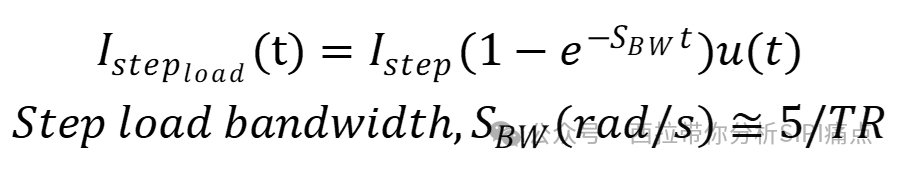

因為我們是一個封裝級別的S參數,為保證結果的通用性,特意加入了板級等效電路,芯片級的CPM模型,我們選取的上升沿TR = 20ns,如圖8所示。根據下列的公式和表格,其大致對應的step load bandwidth為39.8MHz來進行Voltage Droop分析。? ? ??

?

| TR(ns) | Step Load Bandwidth(MHz)?? ? ? ? |

| 1 | 795.8 |

| 20 | 39.8 |

| 100 | 15.9 |

| 200 | 4.0 |

| 500 | 1.6 |

| 1000 | 0.8 |

?

?

圖8-1:?Voltage droop仿真設置 ???

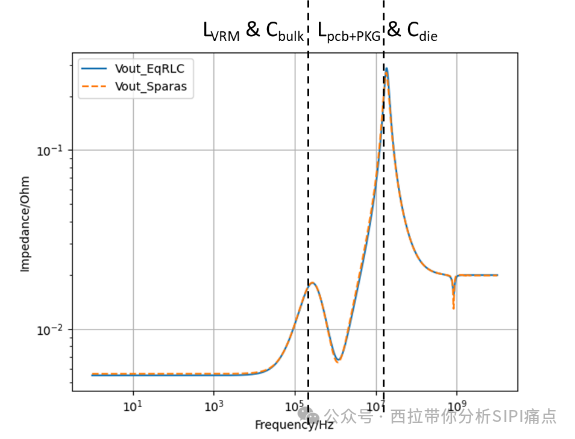

圖8 -2:阻抗曲線比對? ?? ? ? ?

??? ? ???

圖9:First Droop 和Second Droop 對比

該對比結果證明了S2Spice產生的等效電路的準確性,不論是從頻域或者時域出發,均證明了其結果的有效性。

3.3 S2SPICE其他功能? ?

S2SPICE不僅可以進行模型轉換,也集成了S參數常用的處理功能,可以支持數據的前處理,數據對比,以及數據后處理,直接查看結果,無需導出S參數用其他工具查看阻抗曲線對比。

集成了多種數據前處理模式:包含刪選頻段,端口刪減排序,重采樣,重歸一化等

集成了數據的后處理模式,可以直接看到S,Y,Z并對其做端口刪減排序,短路檢查,導出文件等操作,一站式服務

還集成了專門開發了可以抽取具體物理意義等效模型的算法以及對特殊部分進行精度強化的算法

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論