以近代CPU的視角來說,三級緩存(包括L1一級緩存、L2二級緩存、L3三級緩存)都是集成在CPU內的緩存,它們的作用都是作為CPU與主內存之間的高速數據緩沖區,L1最靠近CPU核心;L2其次;L3

2022-10-14 11:02:45 6874

6874 電源開關0和1哪個是開,具體如下: 0是關閉,1是打開。 電器開關上常見的標記符號代表的英文字母“O”是英文“open”縮寫,表示打開;“I”是英文“in”縮寫,表示關閉。 還有一種

2023-09-13 15:04:37 8867

8867 本帖最后由 一只耳朵怪 于 2018-6-22 09:54 編輯

大家好:138上DSP的ram里L1P,L1D,L2都分別有兩個,個人理解L1P,L1D默認作高速緩存,L2為程序存儲,關鍵是

2018-06-21 00:37:03

電路如附圖所示。該電路為間歇式振蕩升壓電路。BG1與L1、L2、C1等構成振蕩器。BG1為振蕩管,工作在開關狀態。L1、C1為振蕩反饋元件。L2為振蕩儲能繞組。為了方便,電路還設計了由BG3構成

2021-05-13 07:15:26

3.2V輸入,如何通過開關的長按短按控制兩個3.2V輸出口單路3.2V直流輸入,兩路3.2V直流輸出L1和L2兩個led燈珠,中間加個自復位開關,想達到一下功能:1.輸入端給電時,兩個燈珠都不亮

2018-03-12 17:39:05

那樣的話,L1 直接和 CCI 交互會很慢吧

2023-01-02 17:27:35

了中斷通知core1,數據還在core0的L2,core1訪問core0的L2來完成數據傳輸。我的疑問是:我的理解是對的嗎?core1為什么可以訪問core0的L2 RAM?

2018-06-25 06:16:40

(會頻繁訪問L2),這樣IO的時間會明顯增長(30%);

這是為什么啊,理論上外設和內核進行數據處理應該是并行的啊?各位大神,求指導……

2018-06-21 04:20:19

對于其它外設不會修改,即只有CPU進行讀寫的數據,有兩種配置方案:1.將L2 Cache配置為SRAM,數據存于L2 Cache,即數據直接放置于L2 Cache中2.配置L2 Cahce全部為緩存,將數據存于DDR2中,配置此段DDR2相應的MAP寄存器以上兩種方案,哪種方案更優?

2019-08-05 14:50:55

輸出 外部可編程限制 電流(L296P) 撬桿可控硅控制電路 遠程抑制和 同步脈寬調制 熱關機 說明 L296和296P是降壓電源開關調壓器在電壓變化時輸出4 A5.1伏至40伏。這些

2020-07-09 10:42:56

、DC-DC轉換器說明L5973AD是一款降壓單片電源開關電流限值為2A,因此它能夠提供大于1.5 A的直流電負載電流取決于應用條件。輸出電壓可設置為1.235V達到35伏。也實現了高電流水平多虧了

2020-09-15 16:58:28

本文作為“主要部件的選型”的第二篇文章,將介紹在開關電源中發揮著重要作用的電感的選型方法。電感:L1電感L1如右側電路圖所示,由輸出電容器C5和LC濾波器共同組成。L1電感值的設置要使設備在不連續

2018-11-27 16:53:22

拓撲結構。注:在最初的設計中,預留電感L1、L2,CBB電容C1、C2作為傳導測試元件,預留磁珠FB1、陶瓷貼片電容C9、貼片電阻R14、R15作為輻射測試元件;傳導測試:1、短接L2,L1=4.7mH

2021-07-09 06:00:00

有哪位朋友知道LED開關電源在正常工作時輸入端L,N線瞬間短路時會損壞開關管是什么原因?

2014-03-15 11:11:23

。2.1電源進線端濾波器在電源進線端通常采用如圖1所示電路。該電路對共模和差模紋波干擾均有較好抑制作用。圖中各元器件的作用:(1)L1,L2,C1用于濾除差模干擾信號。L1,L2磁芯面積不宜太小,以免飽和

2009-10-13 08:39:38

當開關S閉合時,Ui對L1充電。當S斷開時,Ui+EL1通過VD對C1進行充電。再當S閉合時,VD關斷,C1通過L2、C2濾波對負載放電,L1繼續充電。問:為什么S斷開時會對C1充電,而不是直接輸出,難道輸入是直流

2013-08-13 15:55:00

一個ATX電源原理圖上看見開關變壓器上副線圈L2,不知道是做啥用的,請大神分析下

2014-06-04 16:06:28

電源開關設計不起作用

2017-07-04 13:41:10

以A15為例,假設L1 cache是2way 4set的 cache type,而L2 cache的空間會比L1大很多,那么L2 cache會是什么樣的結構呢?是不是需要cache line的大小一樣?或者需要與L1相對應嗎,比如也是4set的?

2022-08-12 11:36:49

【作者】:楊兆清;【來源】:《電聲技術》2010年02期【摘要】:<正>2010年1月8日,知名音響品牌BOSE在中國推出L1 Compact音樂娛樂擴聲系統。與傳統

2010-04-23 11:15:00

C674xDSPL2有一個容量為1MB的L2 ROM,該ROM的功用是什么,謝謝

2018-08-01 08:53:56

目前從事DM8148平臺的開發工作,想請教一個問題:

通常情況下,數據從外存通過EDMA搬移到L2 cache,然后L1 cache 命中,供CPU訪問,CPU處理完數據,在通過EDMA 將處理

2018-06-22 03:35:14

? ?]],

? ?l1PMode:"32K",

? ?l1DMode:"32K",

? ?l2Mode:"128K"

]

由此可以看出L2中256K的容量

2018-06-21 04:58:12

L1和L4信號線,L2地線層,L3電源層。如果L4層上的元器件較少,是主布線層,那么將L2改為電源,L3為地,效果可能會更好些。

2019-05-24 06:01:16

L1和L4信號線,L2地線層,L3電源層。如果L4層上的元器件較少,是主布線層,那么將L2改為電源,L3為地,效果可能會更好些。 6層板:L2和L5為地線層和電源層,其它為信號層。

2019-05-21 10:19:01

S4225S/D系列芯片是開關調色溫的專用芯片,該芯片內置了400V的開關管,簡化了外圍電路結構 . 邏輯順序為L1->L2->L1+L2,其中L1和L2分別代表第一和第二路LED燈串

2017-01-11 17:56:03

嗨,U4301A PCIe 8 GT / s分析儀是否支持ASPM L1子狀態L1.1和L1.2跟蹤(LTSSM流程)? 以上來自于谷歌翻譯 以下為原文Hi, Does U4301A PCIe 8

2018-11-02 09:39:24

最近在學習ZIGBEE的過程中產生了這么幾個疑惑,望高人指點。1、圖中L1的作用是什么?2、為什么要用到兩個晶振?3、四腳的無源晶振怎么畫原理圖和PCB,圖中晶振只有兩個引腳而實際卻是四個?

2019-04-09 04:43:16

的L1就繞在骨架的最里層,其下端(變壓器的②腳)為起始端,其上端(變壓器的①腳)為電源(300V直流)供電端,然后繞制反饋線圈L2和輸出線圈L3,這樣做的好處是反饋及輸出線圈與V1集電極(有較高的脈沖電壓)之間的分布電容將大大減小,有助于提高性能。

2021-05-12 07:12:32

L2沒有到外部DDR的總線,是不是必須要使用IDMA

2018-06-21 11:07:11

大家好:我對于C6678的L2 SRAM(0x00800000)以及各個core私有的L2 SRAM(core 0::0x10800000,core1:0x11800000),存在些疑問,想請教

2019-01-09 10:48:30

諸位高手:小弟使用的是C6747,資料上說這款芯片上有好幾個RAM,包括L1、L2和shared RAM,而L1、L2又分別有兩塊地址與之對應,不知有何區別,而shared RAM與L2又有何區別?sharedRAM 的訪問速度如何,可配置為Cache么?望乞賜教。

2018-08-07 07:31:27

功能。輸出可在 3 種狀態之間切換,分別為L1 導通、 L2 導通和 L1、 L2 共同導通。特點:·內部集成兩路 40V700mΩ調色開關·最高輸入電壓可達 25V·三種色溫模式·超低靜態電流 10uA,支持長時間狀態保持

2020-08-07 09:14:09

與制作元器件清單見下表。L1、L2、L3分別繞在H7×4×2mm3的磁環上,L1、L2繞6匝;L2繞1匝。L4、L5繞在H31×18×7的磁環上,L4繞用Φ=0.1mm的高強度線繞340匝;L5用

2008-10-07 08:58:15

WARNING L1: UNRESOLVED EXTERNAL SYMBOL

SYMBOL:_SENDCHAR

MODULE:main1051.obj (MAIN1051

2023-10-08 07:21:14

最近看6678手冊知道每個核都有自己的L1 L2 SRAM ,這沒問題,但是看2.3節的Memory Map Summary ,發現除了core 0 到core7的 L1,L2地址,還有一個

2018-06-21 17:19:29

的,只能輸入的是偏移延遲和偏移損失。但是自定義校準套件的指令明確表明這些標準存在L0,L1,L2系數。我們想知道為什么8720ES不可能輸入短標準的那些系數,或者僅僅輸入偏移延遲和偏移丟失信息就足夠

2019-05-20 08:02:10

關于cache配置的問題,在L1或者L2中可以配置為cache或者SRAM,請問cache的配置與什么有關?有一些參考資料么?謝謝沒有搞清楚應當如何配置cache,以及配置多大的cache,求指導!!!

2018-07-25 09:24:32

您好,我使用的芯片是C6748,使用DSP/BIOS。C6748的L1P L1D L2都可以部分配置成緩存或RAM。DSP/BIOS中默認設置L1P L1D為cache,L2全部為RAM。請問,在

2018-08-02 06:54:06

在文檔EVLCMB1-90WADP中,L2是簡單的電感還是變壓器?如果它是變壓器,那么匝數比是多少?以上來自于谷歌翻譯以下為原文 In the document EVLCMB1

2019-01-23 06:08:00

練習:利用定時器使L1每秒閃爍(亮0.5秒滅0.5秒),L8亮五秒滅五秒。關閉蜂鳴器。#include "reg52.h"***it L1 = P0^0;***it L

2022-01-12 07:22:47

我想測量這3個相位線(三相到380-440V)這三個相同的50Hz頻率的正弦波信號。對這三條線進行零交叉,如+VE和VE半周期。我想測量這三個信號之間的相移。相角L1相為0°,L2相為120°,L

2019-10-18 06:45:19

嘗試USB2.0部分,則有失敗:事業的發展現在開始測試:L1暫停/恢復測試(配置索引0)開始時間:Mon 8月1日14:54∶36 2016測試設備的LPM L1兼容性測試…USB版本的設備是2.10

2019-06-27 09:09:50

請問,用I.MX6UL開發板OKMX6UL,使用Linux的情況下,如何獲取CPU中L1/L2的Cache狀態和大小;如何禁用和使能Cache?

2022-11-29 06:37:16

接L1和L3(不用區分火線和零線),然后L1C接到L1,L2C接到L3; 三相電接L1、L2和L3,然后L1C接到L1,L2C接到L3; 當然還要接地。試運行 用miniUSB...

2021-09-17 06:55:48

各位大神,我想求助一個電源開關電路,用來控制交流220V電源的開關,電路要求如下:1、電源開關為觸摸式。2、需要打開電源時,手指觸摸開關3-5秒電源接通。3、需要關閉電源時,手指觸摸開關一下就可以

2015-12-26 15:33:25

描述用于 Commodore C64 BN/E 250469 的 L1 過濾器更換用于 250469 板的原始 L1 線路濾波器(可能是Tokin D-08C2)已停產。此適配器板可讓您使用現代 Laird CM4545Z131B-10 作為替代品。PCB

2022-07-29 06:18:26

感謝,進來的朋友。本人請教幾個問題。L1,L2,L3估計是3V-5V電壓的小燈.1.當電流從1線進入時,L2與L3燈會亮嗎?如果不會亮,電流是否從M3(二極管)通過了,為什么不從L2、L3通過。還是

2015-11-02 22:29:27

如圖所示,一個升壓電路,想要請教一下1,C137/C138的作用是什么?大小怎么選擇?圖中有兩個,去掉一個是不是也沒關系?2,L1/L2的大小怎么選擇?3,網上看很多BOOST電路,是沒有L2的,那儲存能量的電容主要是C140還是C139? 電容該怎么選擇?4,怎么提高輸出功率?

2022-08-09 15:09:20

目前從事DM8148平臺的開發工作,想請教一個問題:通常情況下,數據從外存通過EDMA搬移到L2 cache,然后L1 cache 命中,供CPU訪問,CPU處理完數據,在通過EDMA 將處理

2018-07-24 06:57:47

想把L2空間一部分設置成緩存,緩存大小為64kb,把DDR上最開始的16M設置成cacheable,我是這樣配置的:L2CFG=0x2h;L2INV=1;MAR128=0XFFFFFFFFh;不知

2018-08-02 07:44:50

有哪位大神解讀一下,L2當中的1M的ROM怎么使用,沒有找到相關的文檔!

2019-07-24 06:40:32

創龍技術支持工程師您好: 我使用C6748實現圖像處理,需要完成CACHE的優化。圖像處理的圖片為64K,想將L2分配為128Kcache與128K 內部RAM使用。問題1:128K的內部RAM存儲

2019-10-21 08:21:50

在調試6670時,發現L2的地址有0x0080 0000,每個核也有自己的L2地址,像核0 有0x1080 0000。難道每個核有自己的L2,另外有一個L2?如果是這樣的話,這兩種L2有什么關系嗎? 謝謝啊

2019-01-04 11:30:22

各位專家好:請問在內存保護機制中 L2MPFAR 寄存器保存的是地址是不是相對于L2 SRAM的偏移地址?如果是,那么這個 L2 SRAM 是Local SRAM 還是 CorePac L2 SRAM?

2019-01-10 11:37:07

在C6655的memory map summary中這兩個地址有什么區別00800000 008FFFFF1M Local L2 SRAM10800000 108FFFFF1M CorePac0 L2 SRAM還是對于單核來說就是一樣的東西,而是使用的場合不一樣?

2018-07-24 08:10:12

最近在TMS320F2812上實現1024點FFT,分配空間時出現了RAM不夠的情況,因為段DRAMH0的可用空間不夠,編譯一直提示段.ebss分配失敗,所以想利用L0、L1這兩段空間,不知道可以?(主要是L0、L1是受CSM保護的,不知道能不能進行分配)

2018-08-20 07:23:45

方法”等于L1,其中啟用了PHY。1 -如果PHY禁用,CPU如何從USB總線重新喚醒?2——是否可以使用API進入L2掛起模式?這對于節省一些MW和達到2.5mA的總懸浮電流是非常有用的。謝謝達克斯

2019-10-14 07:38:23

小弟費解了很久的電路。 L1 L2 L3是三相電源輸入端, 系統供電是由L1 L2通過變壓器整流得到。4N25 是個光耦(原理圖估計是抄板的來的) 。 光耦輸出的信號由單片機檢測。 產品是個三相電機控制系統。 那該電路到底是什么功能呢?過零檢測? 相序檢測?

2019-09-16 13:48:48

的工作過程。假定這是一個理想器件組成的電源。L2遠大于L1,從L2左側看,可以認為流過L2、C2、RL的輸出電流是一個恒流源,電流I0。諧振角頻率:ω0=1/√L1C1 。特性阻抗:Z0 =√L1/C1

2018-05-22 10:09:39

函數的功能就是使能L1-Cache。L1-Cache由兩部分組成,L1 instruction cache與L1 data cache。可以看下面Cortex –M7的組成框圖。

2016-08-12 11:55:36

L1 可級聯,信號限制器L1 信號限制器采用分立式混合設計,采用薄膜制造工藝以實現精確的性能和高可靠性。此設計使用肖特基橋式四極管和反并聯二極管,可在寬帶頻率范圍內提供一致的限制電平

2023-02-02 13:33:12

L1可級聯,信號限制器L1 信號限制器采用分立式混合設計,采用薄膜制造工藝以實現精確的性能和高可靠性。此設計使用肖特基橋式四極管和反并聯二極管,可在寬帶頻率范圍內提供一致

2023-04-19 16:54:48

低功耗發射器,設計用于抑制不需要的GPS信號。該器件為GPS應用提供緊湊、高性價比的雙工器解決方案。Qorvo QPQ1061 L2低損耗GPS SAW濾波器采用1

2024-02-26 23:02:04

Qorvo QPQ1063 L1/L2低損耗GPS SAW雙工器Qorvo QPQ1063 L1/L2低損耗GPS SAW(表面聲波)雙工器優化用于抑制無用的GPS信號。QPQ1063為支持的波段

2024-02-26 23:23:54

Qorvo QPQ1028雙用途GPS L1/L2雙路濾波器Qorvo QPQ1028雙用途GPS L1/L2雙濾波器為低功耗發射器提供出色的功率處理能力。QPQ1028設計用于抑制雜散信號,無需

2024-02-26 23:27:17

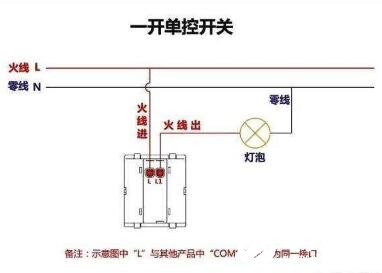

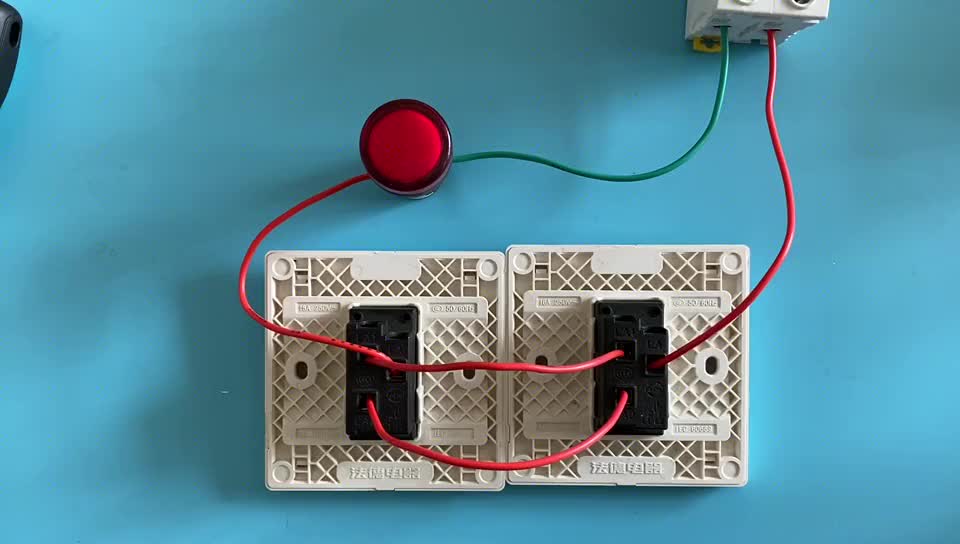

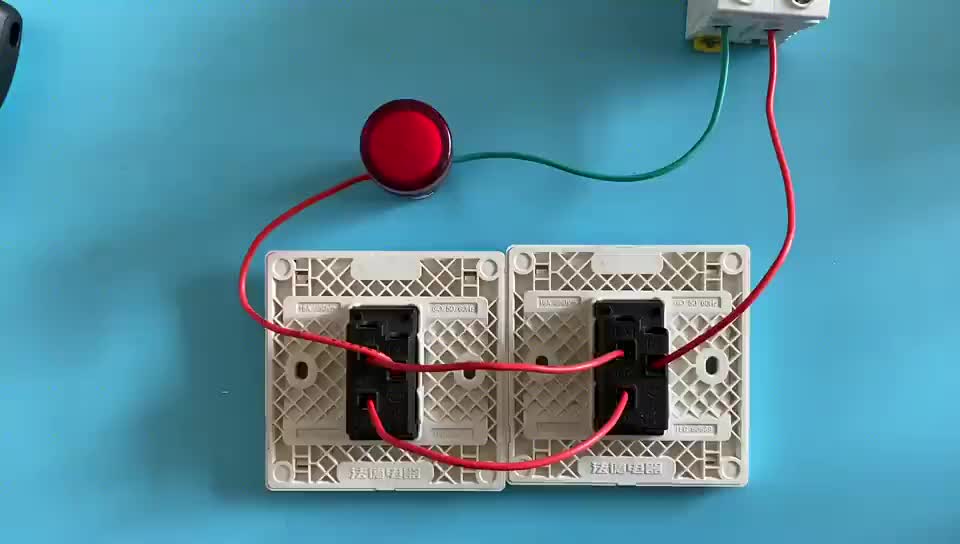

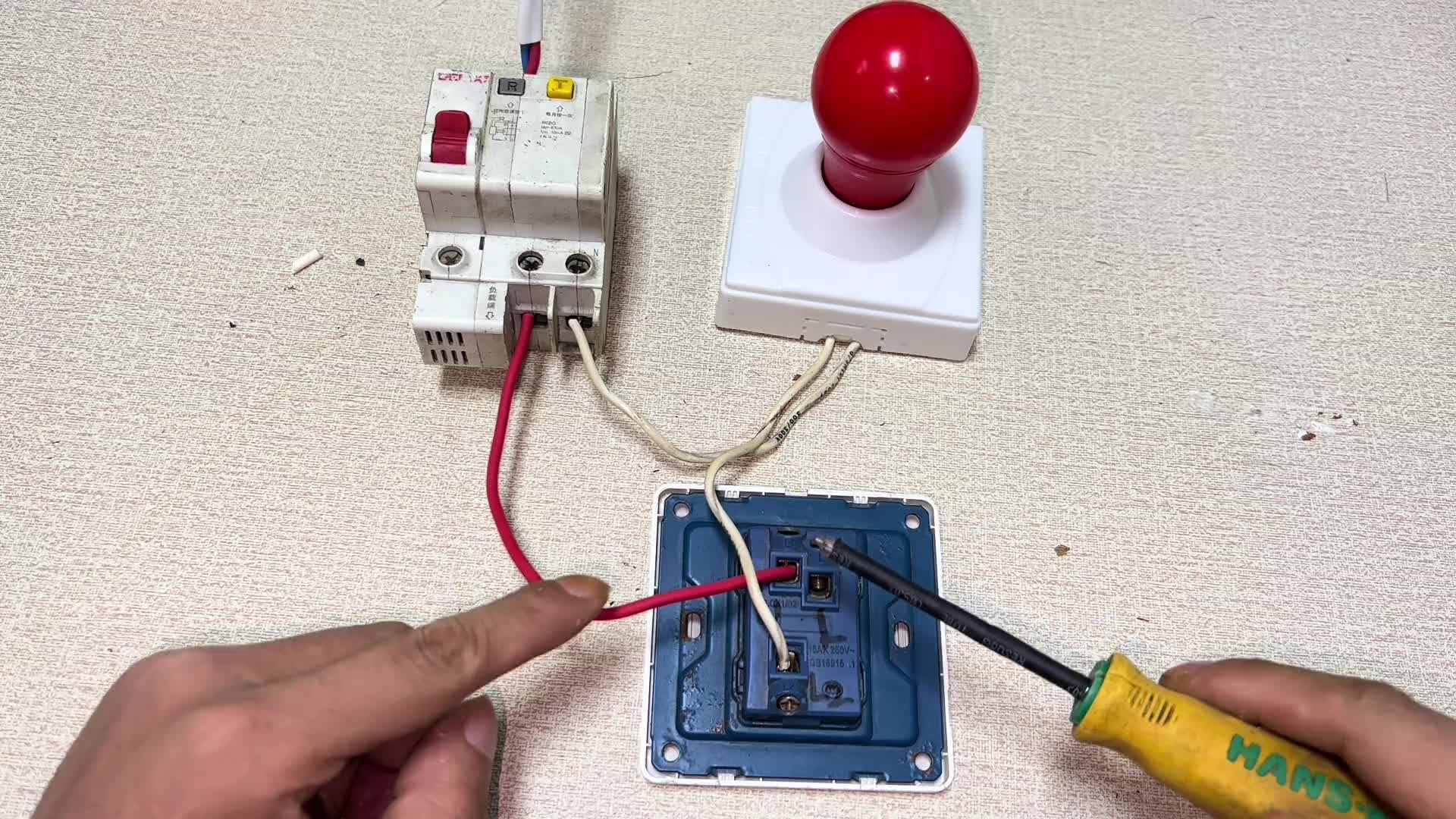

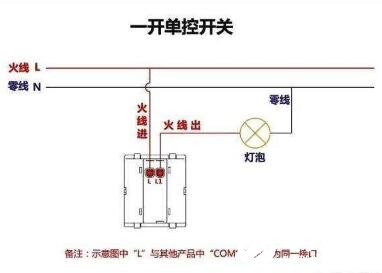

如果只是控制一盞燈,只需要火線接入L,從L1或者L2中某一個端子引出火線接入電燈,電燈的另一個端子接入零線,這樣形成回路就能夠實現開關控制電燈。

2020-01-16 11:29:00 114929

114929

從卡式電源開關的原理和結構可以看出,卡式電源開關與普通面板開關相比。

2020-07-05 10:38:11 1638

1638 日常生活中,我們長看見開關的背面有三個接線柱,分別是l l1 l2,那么這三個接線柱分別是什么意思?如何接線呢?

2022-01-29 15:18:00 48497

48497 電源開關是電子元器件的一種,它可以控制電路的通斷,其中常見的電源開關包括單極開關、雙極開關、三極開關和觸摸開關等。目前主要的電源開關品牌有富士電機、施耐德電氣、ABB、歐姆龍等。

2023-07-14 14:25:23 3419

3419

電子發燒友App

電子發燒友App

評論