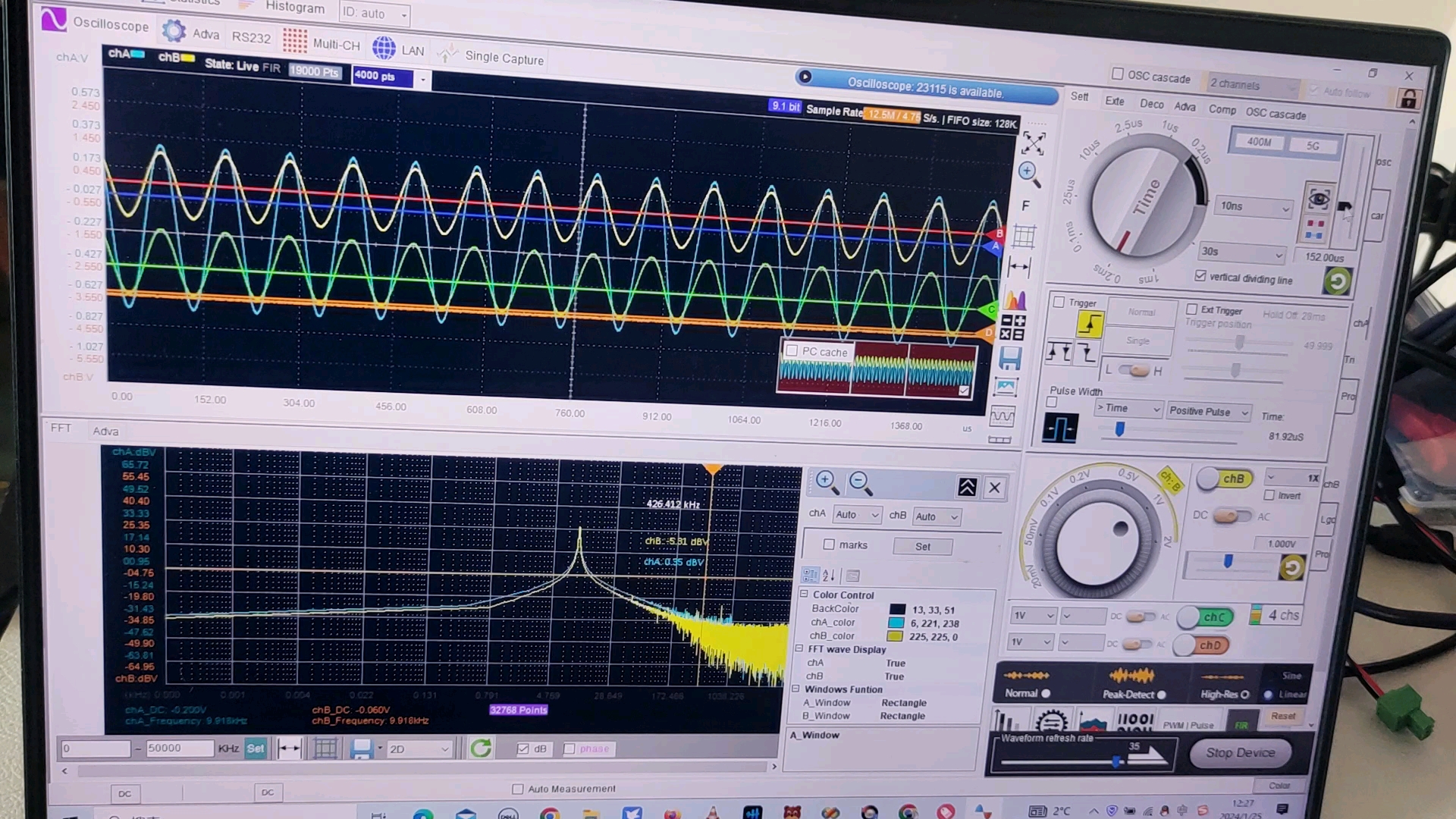

摘要:介紹了基于單片機系統的精密時鐘發生電路對高頻信號(1MHz~80MHz)進行等效采樣的方法,設計并實現一個模擬帶寬為1Hz~80MHz的簡易數字示波器。

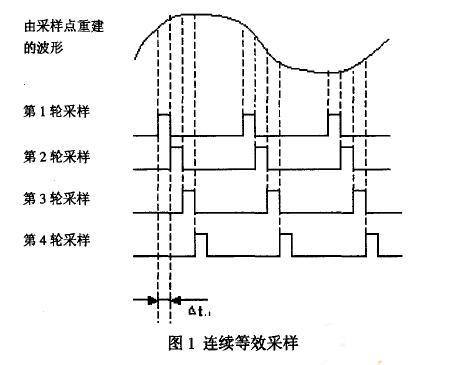

在數字示波器技術中,常用的采樣方法有兩種:實時采樣和等效采樣。實時采樣通常是等時間間隔的,它的最高采樣頻率是奈奎斯特極限頻率。等效采樣(Equivalent Sampling)是指對多個信號周期連續樣來復現一個信號波形,采樣系統能以擴展的方式復現頻率大大超過奈奎斯特極限頻率的信號波形。

1 總體設計

由于所設計的示波器輸入頻率范圍較寬, 本系統采用了等效和實時兩種采樣方式。若輸入頻率小于1.25MHz,選用實時采樣;反之,選用等效采樣。根據輸入頻率確定時鐘芯片的輸出及分頻數。當輸入頻率高于1kHz時,利用可編程頻率合成芯片SY89429V產生基準時鐘;當輸入頻率小于1kHz時,由單片機提供40kHz的基準時鐘。然后根據輸入頻率的大小對基準時鐘使用不同的分頻數,從而產生采樣時鐘。

本系統采用了等效和實時兩種采樣方式。若輸入頻率小于1.25MHz,選用實時采樣;反之,選用等效采樣。根據輸入頻率確定時鐘芯片的輸出及分頻數。當輸入頻率高于1kHz時,利用可編程頻率合成芯片SY89429V產生基準時鐘;當輸入頻率小于1kHz時,由單片機提供40kHz的基準時鐘。然后根據輸入頻率的大小對基準時鐘使用不同的分頻數,從而產生采樣時鐘。

2 硬件設計

2.1總體設計

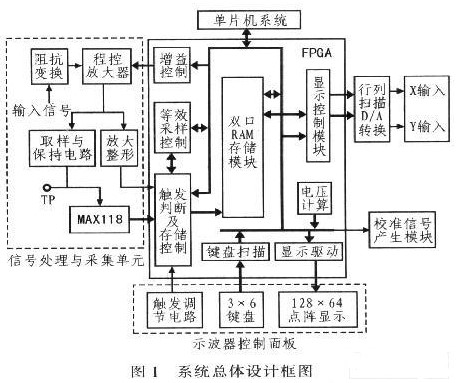

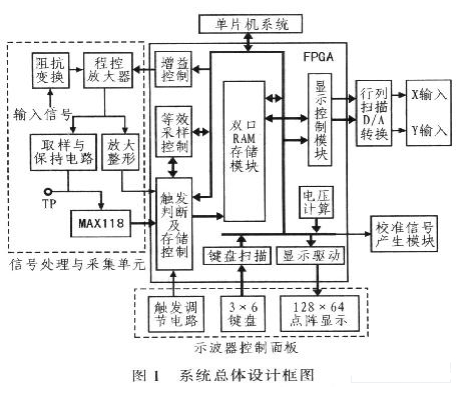

本系統在硬件上可分為五部分:控制器、測頻及鍵盤控制、波形采樣、程控時鐘和液晶模塊。系統功能如圖1所示。

(1)控制器

控制器部分任務較重,通過兩片89C52(MCU1和MCU2)來完成。其中,MCU1負責采樣、數據處理以及程序時鐘和液晶的控制工作;MCU2完成測頻、DAC輸出和鍵盤接口處理功能。兩單片機通過串口通信。

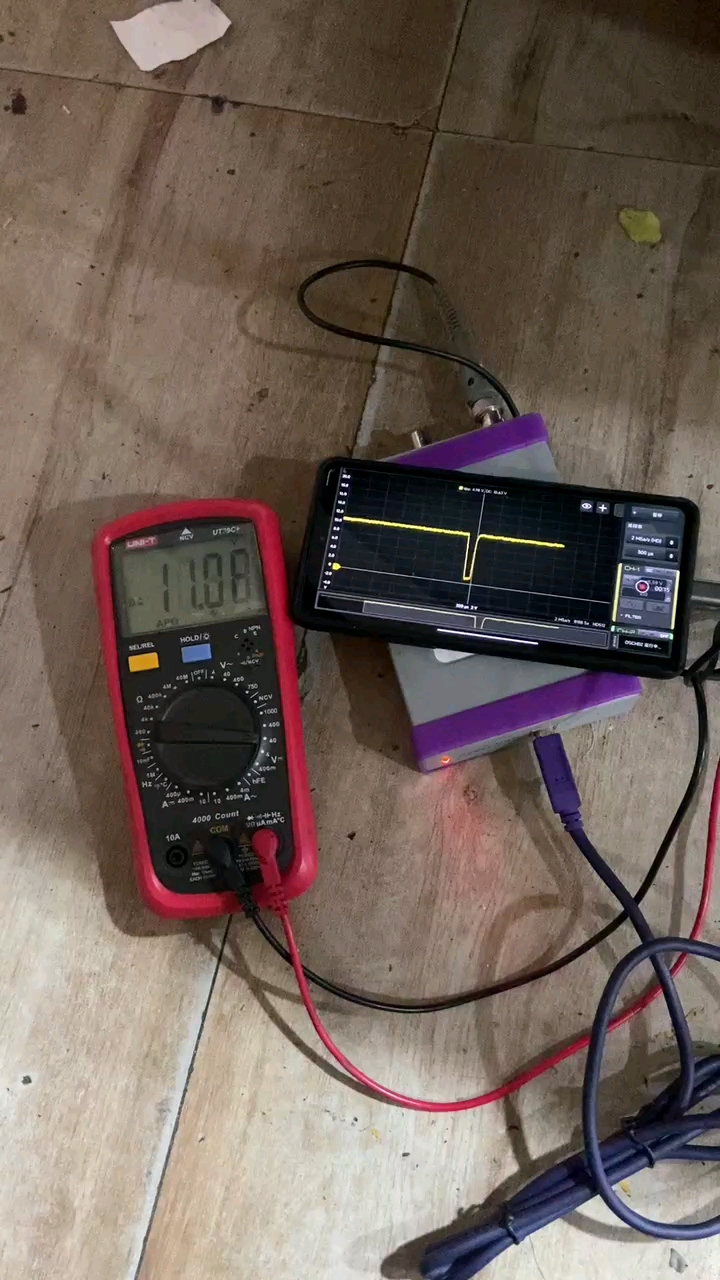

(2)測頻模塊

本系統輸入信號的頻率范圍較寬(1Hz~80MHz),隔度范圍較大(0.1V~2.2V),整形電路采用高速比較器TL3016實現,其參考電壓由MCU1對輸入信號采樣獲得。整形后的信號經程控分頻器送至MCU2測頻,精度可達四位有效數字。

(3)波形采樣模塊

該模塊由40MSPS的模數轉換器TLC5540、靜態存儲器CY7C128A-20和可編程邏輯器件ispLSI1016E-80組成。

在程控時鐘和程控分頻器的控制下,CLPD產生存儲器地址,將高速ADC的采樣數據以程控頻率寫入靜態RAM。寫滿256個點后,將靜態RAM的控制權通過數據選擇器轉交給MCU1,由MCU1進行數據處理,并送液晶顯示。

(4)程控時鐘電路

程控時鐘電路是本系統實現等效采樣的關鍵,其核心是可編程頻率合成芯片SY89429V。SY89429V的輸出時鐘范圍是25MHz~400MHz,步進值0.125MHz~1MHz。它內部采用高頻鎖相環結構,對干擾很敏感,在硬件上采取了一定的抗干擾措施保證其穩定工作。

(5)液晶顯示

液晶部分由點陣液晶顯示器EDM160160、液晶控制器SED1335、SRAMHM62256、負壓發生器和背光交流驅動電路發生器組成。

2.2 等效采樣的實現

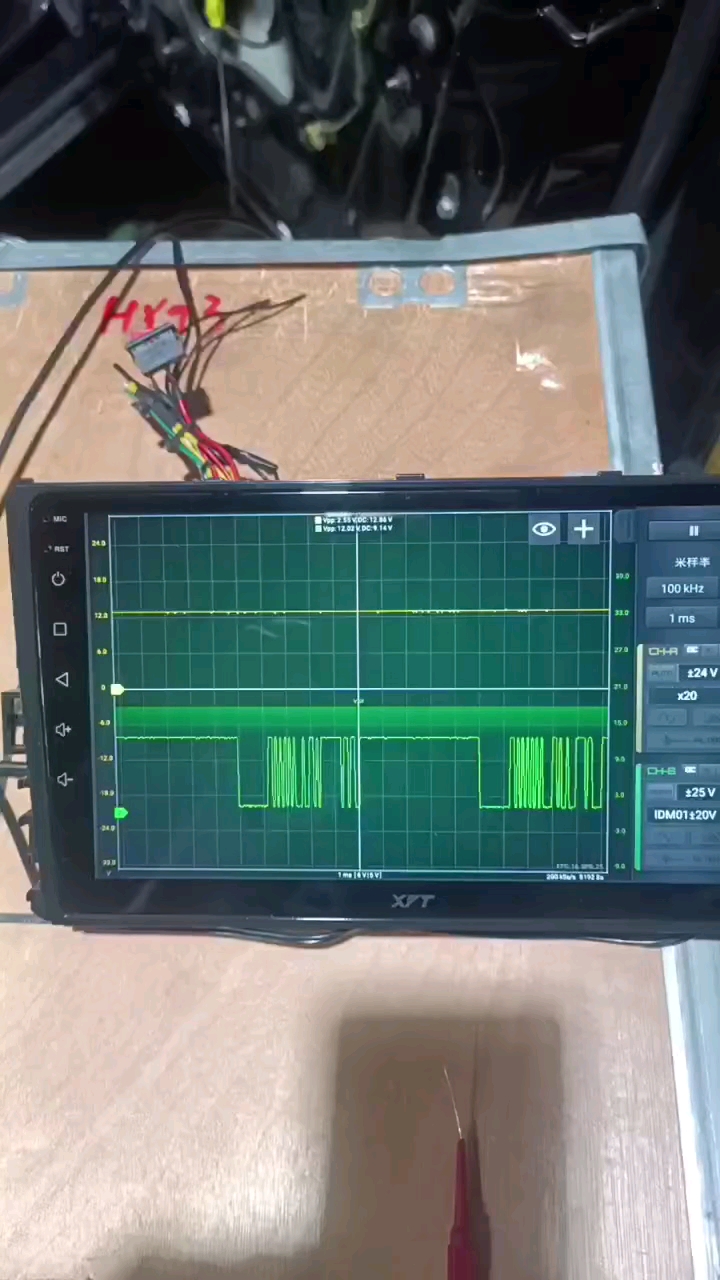

等效采樣是本系統的關鍵和創新點。主要采用以芯片SY89429V為核心的精密時鐘發生電路,控制高速ADC對高頻信號進行循環間歇式采樣。

實現等效采樣的系統框圖如圖2所示。

等效采樣的輸入頻率是1.25MHz~80MHz。為了使復現的波形盡量精確,系統設計在1.25MHz~40MHz信號范圍內每周期采一樣一個點,在40MHz~80MHz信號范圍內每個周期采一個點來復現波形。即采樣頻率范圍要在1MHz~40MHz之間,并有可控的小步進值。

SY89429V的輸出頻率為25MHz~400MHz,需要外加分頻電路將低低頻部分擴展。同時,本系統選用的ADC為TLC5540,其轉換速率是5MSPS~40MSPS,低端采樣率會受到限制,可以采用控制RAM寫入速度的方式來控制采樣速率。綜合考慮,采用CPLD器件,將SY89429V芯片TEST輸出的FOUT頻率經過程控二分頻器,一方面提供給ADC作為CLK工作頻率,另一方面再經過程控二五十進制分頻器控制RAM寫入速度,作為低端信號的采樣頻率。

3 軟件設計

3.1 總體軟件流程

總體軟件流程如圖3所示。MCU1接收MCU2的測頻結果,并將幅值信息傳遞給MCU2,由MCU1根據輸入頻率確定采樣方式,并控制精密時鐘發生電路為ADC提供采樣時鐘。一次采樣完成后,由MCU1處理采樣數據并送LCD顯示。

3.2 實時采樣的實現

實時采樣中,為了使采樣得到的波形盡量精確,系統將1.25MHz以下的信號分為三個頻率范圍,在每個頻率范圍內由程控時鐘電器產生某一固定的基準時鐘,結合相應的分頻數進行采樣。具體設置如睛:輸入頻率為1Hz~1kHz,由單片機提供40kHz采樣時鐘;輸入頻率為1kHz~1MHz,由芯片SY89429V提供40MHz采樣時鐘;輸入頻率為1MHz~1.25MHz,由芯片SY89429V提供50MHz采樣時鐘。

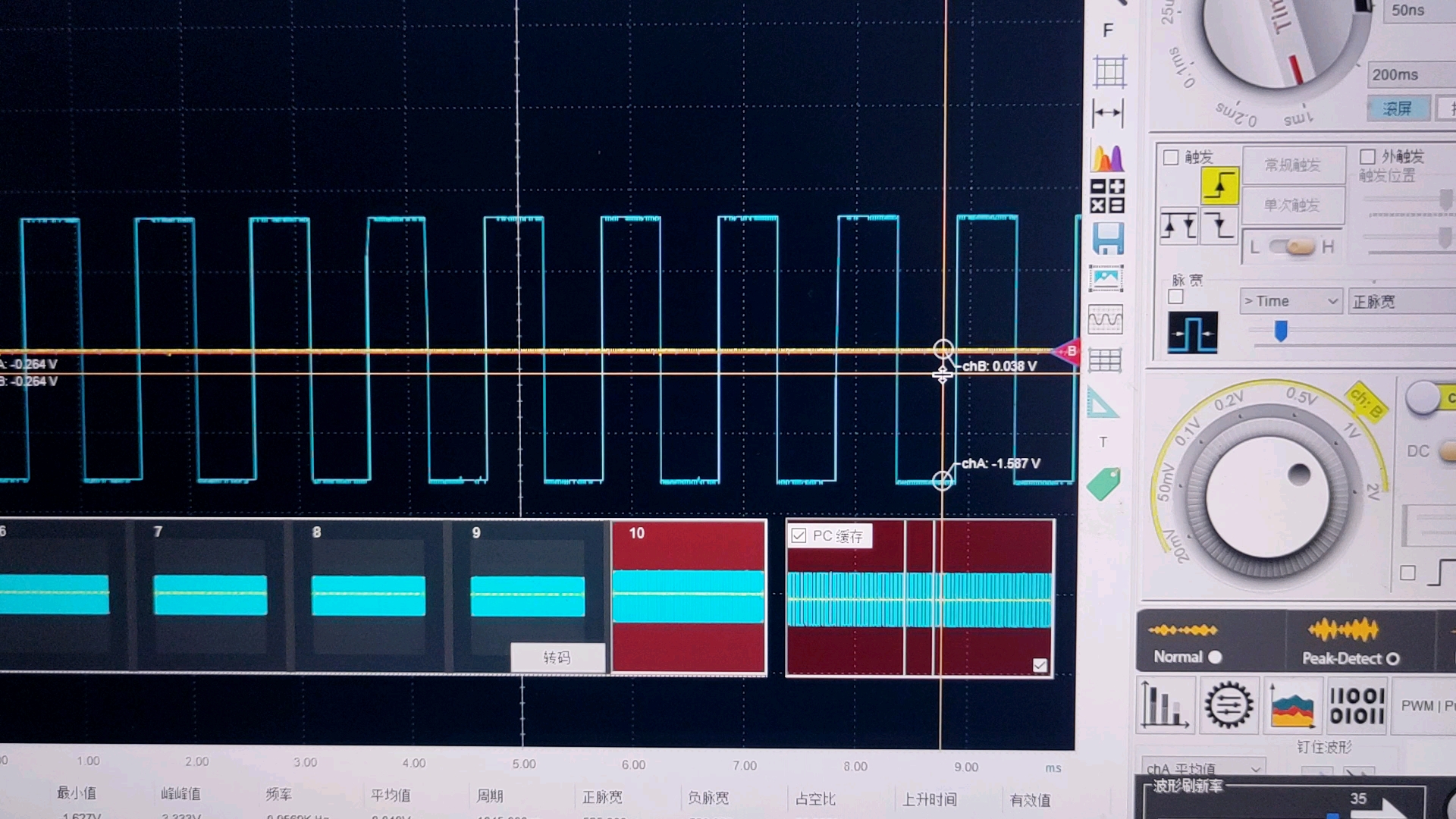

3.3 等效采樣的實現

由于可編程頻率合成芯片SY89429V在本系統所使用的25MHz~50MHz頻率范圍內,步進值始終為0.125MHz。為便于數據處理,軟件設計過程中可以將所有的實際頻率轉換成以0.125MHz為單位的代值,即除以0.125MHz。

系統中所采用的模數轉換器TLC5540的轉換速率為5MHz~40MHz,當輸入頻率小于40MHz時,采用每個信號周期采一點的方法;當輸入頻率超過40MHz時,采用兩個信號周期一點的方法。

下面以輸入頻率在1.25MHz~40MHz之間的情況為例,輸入頻率大于40MHz的情況可以類推得到。

將輸入頻率fin轉換后的代值(以后簡稱代值)記為dfin,根據輸入頻率設定芯片SY89429V的頻率字SY(只取整數,用于控制輸出信號的頻率),經過n分頻后產生采樣頻率。根據等效采樣的原理,采樣頻率與輸入頻率相近(對于輸入頻率為40MHz~80MHz的情況,采樣頻率與輸入頻率的二分頻接近),二者頻率代值的差值記做da,則SY可以表示為:

SY=(dfin-da) ×n (1)

這時復現一個波形所需的采樣點數為:

d=(dfin-da)/da (2)

本系統選用的液晶為160×160點陣,將x軸上40個點所表示的時間定義為一格時基,記作A,則液晶屏幕上顯示的周期個數為:

N=160×da/(dfin-da) (3)

由此,時基可以表示為:

A=N/(4×fin)=40×da/[fin×(dfin-da)] (4)

一個波形的采樣點數也可以用時基和輸入頻率來表示:

d=40/(A×fin) (5)

筆者利用本文介紹的算法,實現了等效采樣,能夠地1MHz~80MHz的周期信號進行波形復現,效果令人滿意。這種簡易示波器在人機界面上為用戶提供手動和自動兩種工作模式,性價比高,有廣闊的市場空間。

- 波器設計(5501)

相關推薦

51單片機差分采樣

單片機AD采樣周期

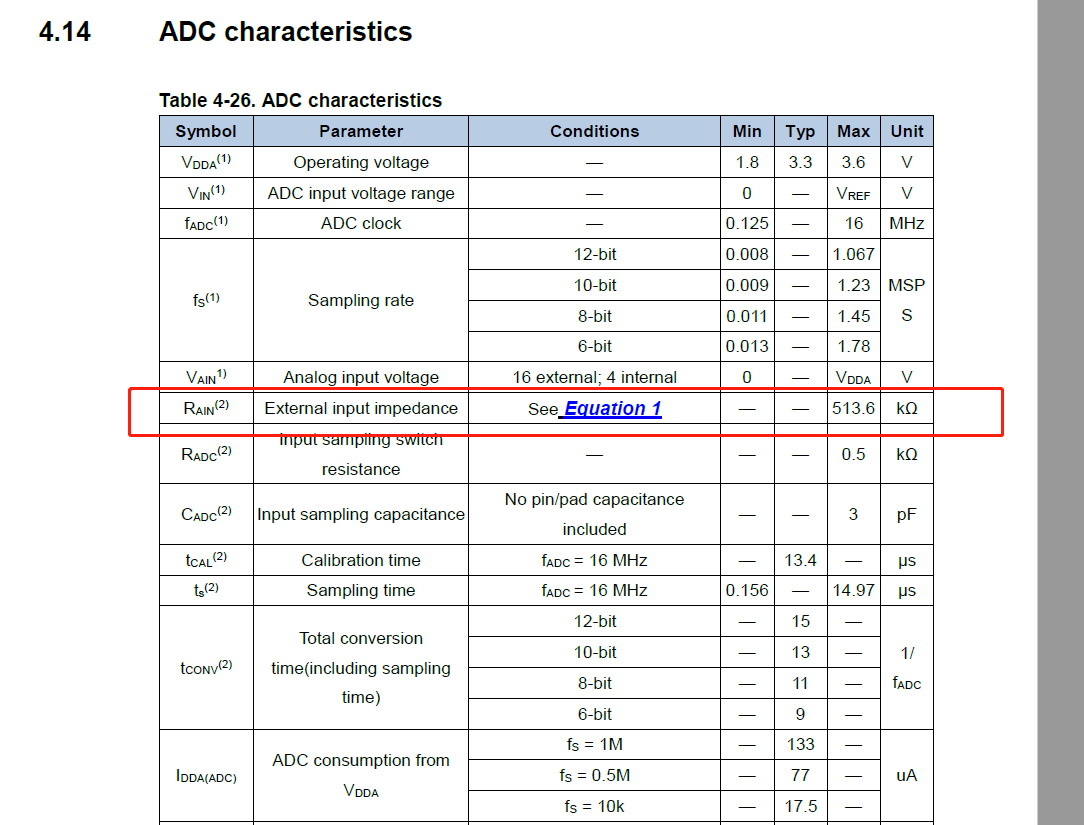

單片機ADC的采樣頻率和采樣速率是不是同一個概念?采樣頻率、速率要遠遠大于被采樣的信號頻率和速率?

單片機是如何采樣ADC值的?

單片機是如何對電流進行采樣的

【AC620 FPGA試用申請】等效隨機采樣的數字存儲式示波器

【Longan Nano申請】基于高速單片機的示波器設計

制做一個數字采樣示波器

基于51單片機的簡易數字示波器制作

學習單片機的采樣流程

怎么在proteus中用示波器仿真單片機的輸出波形?

怎樣去測試STM32單片機ADC采樣速率問題

用單片機做PID控制時采樣時間的選擇

基于單片機的等效采樣示波器的設計

42

42【PADAUK】應廣單片機 PMS150C系列 代燒錄

應廣單片機 PFS154系列 代燒錄

【PADAUK】應廣單片機 PMS134系列 商業級 燒錄

【PADAUK】 應廣PMS152E系列 應廣單片機

【PADAUK】 應廣PGS152單片機EEPROM芯片

【PADAUK】應廣單片機 PFC151系列

8位FLASH單片機HR7P169BFGSD

8位FLASH單片機HR7P169BFGSF

九齊MCU單片機 NY8B072A SOP20 NY

NY8B062M型號單片機,臺灣九齊AD單片機,技術支持

NY8A050D單片機,AD單片機,九齊代理

基于EDA技術的等效采樣的設計實現

19

19基于單片機和FPGA的簡易數字存儲示波器設計

1159

1159

示波器的采樣率和存儲深度

7129

7129基于FPGA的等效采樣存儲示波器設計

126

126基于AT89S52單片機的簡易數字示波器設計

9678

9678

基于單片機和FPGA的數字示波器的設計

277

277采樣示波器原理結構

947

947

利用單片機和FPGA器件實現等效和實時采樣方式的數字示波器設計

2265

2265

采用EDA技術的等效采樣方案介紹

6715

6715

如何使用51單片機進行簡易示波器的設計

14

14采用實時采樣和等效采樣相結合實現數字示波器的設計

2001

2001

實時示波器與采樣示波器區別

10285

10285STC12C4052ADSTC單片機ADC采樣C程序

51

51單片機如何采樣電流

74

74單片機采樣學習記錄

1

1基于FPGA的等效時間采樣原理的實現

537

537

示波器設置采樣次數

624

624什么是示波器的實時采樣率?什么是示波器的等效時間采樣?

920

920示波器采樣時間怎么設置 示波器的采樣率有什么意義?

2206

2206單片機采樣電壓問題 單片機的供電電壓過低對單片機AD采樣有影響嗎

1581

1581單片機如何直接采樣互感器

429

429示波器實時采樣與等效采樣有何區別

319

319示波器測單片機輸出波形怎么測

620

620采樣示波器和實時示波器的區別

423

423等效時間采樣示波器與實時示波器的對比,有什么不同?

321

321 電子發燒友App

電子發燒友App

評論