摘 要:介紹了聲納脈沖偵察模塊的測向測距原理、硬件設計及其實現。聲納脈沖偵察模塊硬件電路以數字信號處理器為核心,通過可編程門陣列實現邏輯控制,再配以適當的片外存儲器及其它外圍電路,從而構成一個嵌入式系統。通過對設計需求的分析,提出了設計思路,給出了設計的具體方案。本模塊已通過各項指標測試,工作穩定、性能優良。

測定水下以及水面目標的位置是聲納系統的重要任務,目標的位置由目標的弦角(或方位角)和距離決定。聲納脈沖偵察模塊作為聲納偵察系統的一部分,擔負著測向和測距的任務。聲納脈沖偵察模塊通過測定三路信號的時延差以及時延差的差來測定目標的方位和距離。

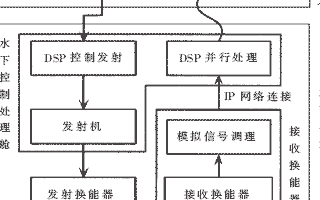

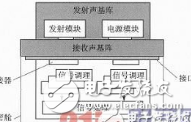

隨著電子技術的發展,水聲設備也加速了更新換代的步伐。水聲設備的發展方向應該是現代化、小型化、智能化,一些原來用硬件實現的功能可以由軟件來完成,這為功能的更新和發展提供了極大的便利。正是順應這一趨勢,作者結合實際進行了聲納脈沖模塊的改造。如圖1所示,聲納脈沖偵察模塊可以分為兩大部分:模擬部分和數字部分。現只就聲納脈沖偵察模塊數字部分的設計進行闡述。下面介紹聲納脈沖偵察模塊的測向測距原理、硬件設計及其實現。

圖1 聲納脈沖偵察模塊系統框圖

1 聲納脈沖偵察模塊測向測距原理

目前,被動測距聲納主要有兩種類型:共形陣和拖曳式線列陣,它們都是直線陣。共形陣在艦艇殼體上配置三對(左、右舷側各三個)子陣。陣元的布放可分為對稱陣和非對稱陣。對稱陣的三個陣元在直線上等間距布放,非對稱陣的三個陣元的間距之比是1:2。對于三元陣來說,對稱陣和非對稱陣的測向、測距原理是相同的。由于陣型的差異,非對稱陣和對稱陣在測距計算、距離模糊的范圍、時延測量誤差對測距誤差的影響等方面也存在差異。

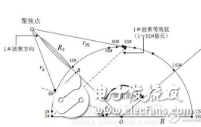

下面以非對稱陣為例給出測向測距原理[1~2]。如圖2所示,設三元非對稱陣首中陣元的間距為d,目標方位角為θ,目標到各陣元的距離分別為r1、r2、r3,其中,r2為要測定的目標距離r。

圖2 三元非對稱陣測向及測距模型

在極坐標系中,設目標的坐標為S(r,θ),三個陣元的坐標分別為1:(d,0),2:(0,0),3:(2dπ),聲速為c,目標信號到達各個陣元的時延差分別為τ12、τ23、τ13。其中,τ12表示陣元1、2接收信號的時間差,τ23表示陣元2、3接收信號的時間差,陣元1、3接收信號的時間差τ13為τ12和τ23兩者之和。稍加分析和推導可得到在遠場的目標方位的近似公式為:

2 設計需求分析

2.1 聲納脈沖偵察模塊的主要任務

聲納脈沖偵察模塊需要完成的任務主要為:在搜索狀態下實時檢測聲納脈沖的到達,并快速測量聲納脈沖的頻率和目標的方位;在跟蹤狀態下,進一步解算出目標的距離以及聲納脈沖的重復周期,給出置信度。

2.2 輸入輸出接口

聲納脈沖模塊的輸入信息包括:左右舷的艏、舯、艉共六路已放大濾波的陣元信號;存儲在EPROM中的陣長、水聽器陣基線和艦艇的艏艉線之間的夾角和誤差修正表;實時測得的水中聲音的傳播速度;跟蹤命令。輸出信息包括:搜索狀態和跟蹤狀態顯示信息;解算出的頻率、方位、距離等數據;故障自檢結果。

2.3 軟件對硬件的要求

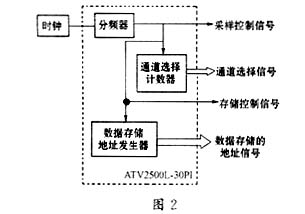

按照偵察模塊功能要求,系統軟件的工作主要由三個進程構成,如圖3所示。系統平時工作在實時檢測進程;一旦檢測到聲納脈沖,系統就進入數據存儲進程,將由模/數轉換器輸入的數據存入存儲器;完成數據存儲之后進入數據解算進程,解算之后的結果輸出給顯控臺,然后重新進入檢測進程。上述過程將一直循環往復。

圖3 系統工作進程圖

2.3.1 實時檢測計算量

在實時檢測進程中,外部六路陣元輸入信號由模/數轉換器進行同步并行采樣。根據系統要求,每路采樣頻率為1MHz。數字信號處理器在進行實時檢測時要對數據進行降采樣處理,使采樣頻率降為100kHz。數字信號處理器對其中的四路信號(左右舷的艏艉通道)進行實時自適應線譜增強(ALE)運算,以檢測聲納脈沖。根據算法分析,計算單路ALE約需要300個指令周期,四通道共需1200個指令周期,若采樣頻率為100kHz,則數字信號處理器的運算能力應大于120MIPS。

2.3.2 數據存儲量

當檢測到信號時,數字信號處理器開始將六路數據中的三路(左舷或右舷的艏、舯、艉陣元)存入數據存儲器中。存儲單元的大小是由解算所需的最大數據量、系統的采樣速率、三路信號間的最大延時等因素決定的。假設陣長D=45m,取聲速c=1500m/s,則在±60°扇面內,艏艉陣元之間信號到達的最大延時為:

Dsin60°≈26(ms) (3)

若系統的采樣速率為1MSPS,系統解算數據至少需要30ms長的樣本,則在數據存儲過程中至少要存儲的數據量(從信號到達時刻算起)為:

(26ms+30ms)×3×1MSPS=168Kword (4)

2.3.3 數據解算運算量

數據存儲完畢后,數字信號處理器開始進行參數的解算。解算內容主要包括:粗測時延、頻率估計、相位估計、目標跟蹤關聯等。數字信號處理器在解算過程中不再響應外部的中斷,此時是系統工作的盲區。根據聲納使用要求,這個盲區越小越好,這意味著主處理器的運算速度越大越好。據粗略估計,若要求盲區為100毫秒,則160MHz的處理器是能夠完成任務的。

2.4 輸入信號動態范圍

根據環境噪聲譜級的分析,系統背景噪聲的動態范圍不超過42dB,再考慮到信噪比要大于13dB,系統輸入的動態范圍應大于55dB,則ADC的精度應該不低于10比特。

3 硬件設計方案

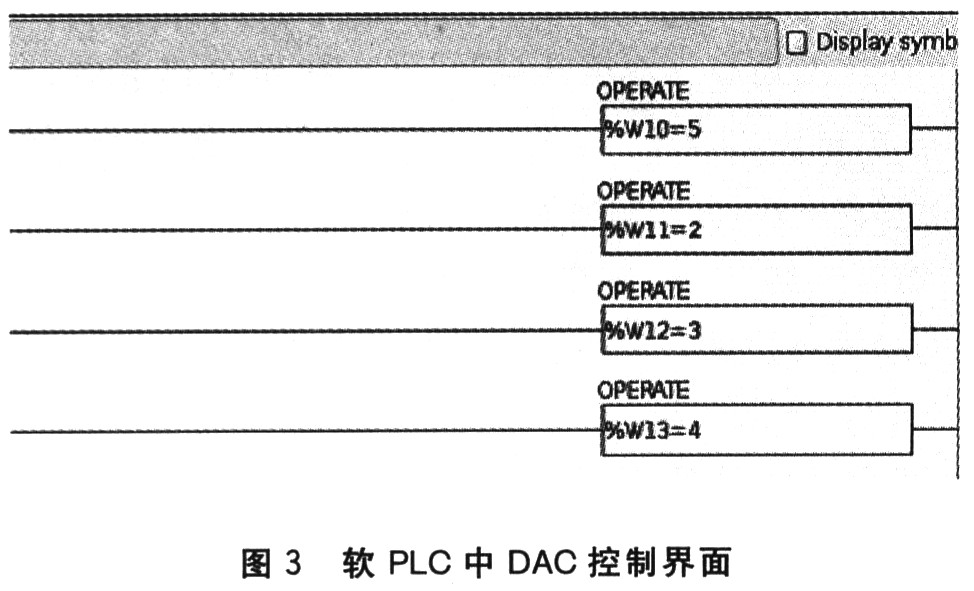

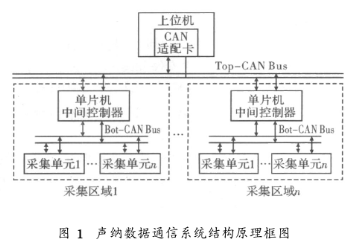

本系統硬件電路采用模塊化的設計方案,如圖4所示。按照功能大致可以分為四個大的模塊:模/數轉換模塊、邏輯控制模塊、數字信號處理器模塊、數據存儲模塊。下面就各個模塊的功能及實現方法進行詳細介紹。

3.1 模/數轉換模塊

模/數轉換模塊的功能是完成信號從模擬形式到數字形式的轉換。如圖4所示,模/數轉換器通過邏輯控制芯片與數字信號處理器相連接。模/數轉換器的轉換需要的時鐘由邏輯控制芯片對數字信號處理器的時鐘輸出信號進行分頻得到。

圖4 系統硬件框圖

由前面的分析可知,模/數轉換器的轉換速率需要在1MSPS以上,轉換精度不能低于10比特。這里選用TI公司的THS1206,其主要特性為:精度為12比特;總的采樣速率為6MSPS;可四路同步采樣。其它特性可參見參考文獻[3]。

3.2 邏輯控制模塊

邏輯控制模塊的功能包括模/數轉換器的設置;模/數轉換器數據的輸入接口;9比特聲速數據的輸入接口;1比特的控制線輸入接口;1比特的故障自檢信號接口;靜態RAM與主處理器的接口。在邏輯控制芯片上實現了一塊雙口數據RAM,用以實現解算數據的存儲。本系統中的邏輯控制芯片選用Altera公司的FLEX10K系列器件中的EPF10K10AI144-3,其主要特性如下:邏輯門數為10,000,最高工作速率為125MHz。其它特性可參見參考文獻[4]。

3.3 數字信號處理器模塊

數字信號處理器是本系統的核心,由它完成各種控制、檢測和解算等。數字信號處理器在實時檢測過程中實現對信號的檢測。當檢測到聲納脈沖時,系統轉入數據存儲進程,這時數字信號處理器負責進行數據存儲的控制;當數據存儲結束時,系統進行數據的解算,數字信號處理器從片外RAM中讀取數據,完成解算,并負責將結果輸出。本系統選用TI公司生產的TMS320VC5416-160芯片,其主要特性如下:指令周期峰值運算速度達160MIPS;128K×16的片內RAM;16bit定點DSP;8M程序/64K數據存儲空間。其它特性可參見參考文獻[5]。

3.4 數據存儲模塊

數據存儲模塊由靜態RAM構成,完成數據的存儲。根據數據存儲容量,選用Cypress公司生產的CY7C1041BV33-Z15芯片,其最快存儲速度為15ns。其它特性可參見參考文獻[6]。

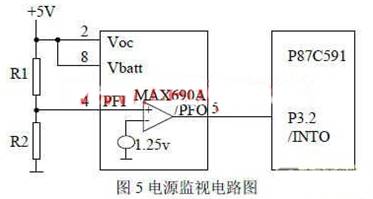

另外,其它部分還包括:邏輯控制芯片初始化所需的EEPROM;存放數字信號處理器工作程序的EEPROM;電源管理模塊,用以實現電源的管理;一片EPROM,其中存有陣長、水聽器基線與艦艇艏艉線之間的夾角和誤差修正信息。

4 系統的工作流程

首先是數字信號處理器引導自己的程序,對其內部進行各種設置、對各種寄存器進行初始化及內部自檢,同時邏輯控制芯片引導程序進行初始化。初始化以后進行板級自檢,由TMS320VC5416完成。自檢的內容包括:片外的靜態RAM(CY7C1041)、片外的EPROM(2716)、模/數轉換器(THS1206)等是否工作正常。完成自檢后,將自檢的結果通過邏輯控制芯片輸出。板級自檢之后的工作是讀入聲速參數及從EPROM(2716)中讀進所需的參數。上述工作完成之后,系統就進入如圖3所示的工作進程中。

5 實驗結果

在實驗室里,用電信號目標模擬器測試聲納脈沖偵察模塊的性能,輸出結果顯示在顯控臺。表1和表2分別給出了方位和距離測量實驗的結果。實驗結果的測量條件為:6級海況,信噪比為20dB,聲速為1500m/s,目標距離為15km,起始方位為30°,每秒遞增0.2°,脈寬為200ms,脈沖重復周期為4s。顯控臺上頻率的顯示只精確到0.1kHz,而實際測頻誤差小于1%,所以對4kHz、8kHz、12kHz的信號進行頻率測量時,顯示的測量值分別為4.0kHz、8.0kHz、12.0kHz,誤差為0%。

| 頻率 | 右舷 | 左舷 |

| 4.0(kHz) | 0.40° | 0.26° |

| 8.0(kHz) | 0.28° | 0.25° |

| 12.0(kHz) | 0.27° | 0.27° |

| 頻率 | 右舷 | 左舷 |

| 4.0(kHz) | 3.88% | 3.03% |

| 8.0(kHz) | 5.02% | 2.21% |

| 12.0(kHz) | 3.5% | 4.6% |

脈沖偵察模塊是以TMS320VC5416為核心數據處理單元,以FLEX10K10A作為邏輯控制單元的硬件處理系統,具有可靠性高、結構簡單靈活、適應性強、運算能力強的特點。該聲納脈沖偵察設計方案經過實驗室的各項性能指標測試,達到了某型聲納技術條件規定的各項要求,工作穩定、性能優良。

電子發燒友App

電子發燒友App

評論