新型雷達數字電路便攜式自動測試系統設計

基于對ICT測試、功能測試局限性的深入探討,以及對邊界掃描測試技術的研究與實踐,本文提出了“MERGE(組合)”邊界掃描測試模型的建立方法,并基于此方法,構建了數字電路便攜式自動測試系統,實現了對新型雷達數字電路的高速、準確的測試。系統具有硬件設備小巧、便攜,性能穩定、可靠,故障隔離率高等優點,適合于戰地級實時維修保障,是大型在線測試、功能測試平臺的有效補充,較好的解決了測試設備受制于人及戰時應急搶修等問題。

雷達,作為一種重要的軍事武器裝備,在軍事上將其形象的比喻成作戰指揮員的“眼睛”,在維護國家安全及領土完整中發揮著舉足輕重的作用。但隨著數字電路設計及制造技術的發展,特別是CAD設計軟件的進步及完善,單一的測試方法如ICT(In-Circuit Test)測試、功能測試等已無法滿足新型雷達數字電路測試及故障診斷的要求,邊界掃描測試將成為今后雷達裝備數字電路故障診斷發展的主流技術。

自動測試系統實現

“MERGE(組合)”測試模型的建立

IEEE 1149.1標準明確的規范了邊界掃描構建原理及相應的測試方法。在故障診斷過程中,可利用VLSI芯片自帶的邊界掃描結構及相關測試指令,有效的實現對VLSI芯片引腳固定型、開路、橋接等故障類型的檢測。但待測試的數字電路模塊通常包括邊界掃描器件和非邊界掃描器件,本文提出的MERGE測試模型可通過已有的邊界掃描結構實現對非邊界掃描芯片的測試,能夠拓展邊界掃描的測試范圍,提高TPS的故障覆蓋率。

基于邊界掃描測試技術的基本原理,構建測試系統過程中創造性的提出了“MERGE”結構測試模型,基本思想如圖 1所示。其中,B部分為待測數字電路BUT(Board Under Test),A部分為獨立于BUT外的邊界掃描擴展卡,該擴展卡可看作是一塊符合IEEE 1149.1邊界掃描設計規范的數字電路。首先,集中將一個完整的數字電路BUT分為如下幾個部分:非邊界掃描芯片簇(U1),邊界掃描芯片簇(U2),混合芯片簇(U3)。在這里“簇”的概念即將多個器件統稱為一個“簇”,簇的范圍可以根據具體電路規模來進行劃分,可以小到單獨的一個IC或UUT(Unit Under Test),也可大到一個完整的BUT 。

(1) MERGE非邊界掃描芯片簇(U1):非邊界掃描芯片是整個BUT網絡中一個有序的子集,是具有特定功能的電路。在MERGE理念中,通過對非邊界掃描芯片簇建立單獨的功能模型,將其作為邊界掃描芯片間的一個中間級信號傳輸模型,MERGE到邊界掃描鏈路,結合EXTEST邊界掃描指令,通過Capture IR→Shift IR→Update IR→Capture DR→shift DR→Update DR等相應操作,達到通過邊界掃描鏈路實現對非邊界掃描簇測試的目的。 (2) MERGE混合芯片簇(U3):混合芯片簇指既含有非邊界掃描芯片,又含有邊界掃描芯片的混合電路(還可以含有一些中間級的模擬電路)。MERGE的思路與(1)類似,模型的驗證可通過將一組確定的測試矢量集APPLY至MI(Model Input),經過確定的時間延遲,通過在MO(Model Output)將采集到的響應信號與寄存器中存貯的期望值相比較的方法實現測試。

(3) MERGE BSEC(邊界掃描擴展卡),通過BSEC實現對BUT邊緣電路中非邊界掃描芯片簇或不含邊界掃描芯片的BUT進行邊界掃描測試。測試時,將待測BUT作為非邊界掃描簇或混合邊界掃描簇,而將BSEC當作邊界掃描芯片簇,通過MERGE方法,將BUT、接口電路、邊界掃描擴展卡電路虛擬成為一個含邊界掃描芯片的BUT,具體實現與(1)、(2)類似。

測試系統硬件設計

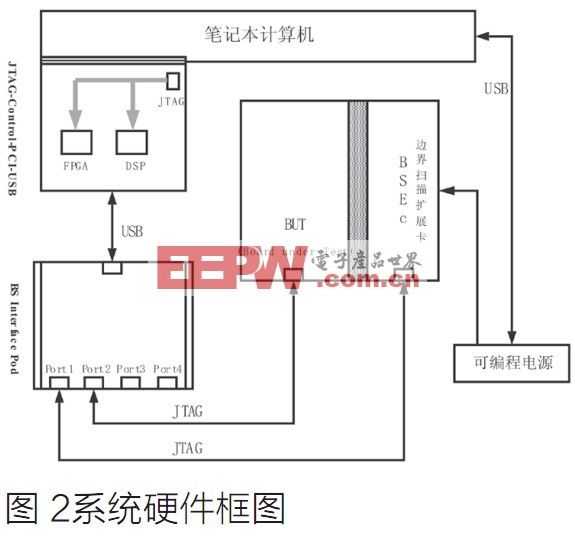

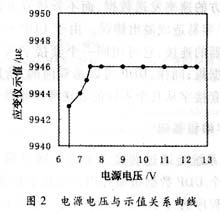

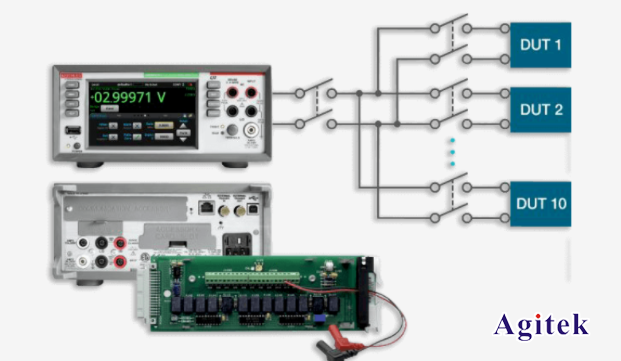

為了減輕系統整機的重量,便于運輸及攜帶,本測試系統前端設備采用筆記本計算機作為主體來完成系統功能的實現和人機界面的交互[3],同時內配GPIB-USB模塊、JTAG-Control-PCI-USB控制器,分別控制可編程電源(Agilent 6600)及BS Interface Pod模塊。整個硬件設計的核心為BSEC、JTAG-Control-PCI-USB控制器及BS Interface Pod模塊。其系統硬件框圖如圖2所示。

邊界掃描擴展卡

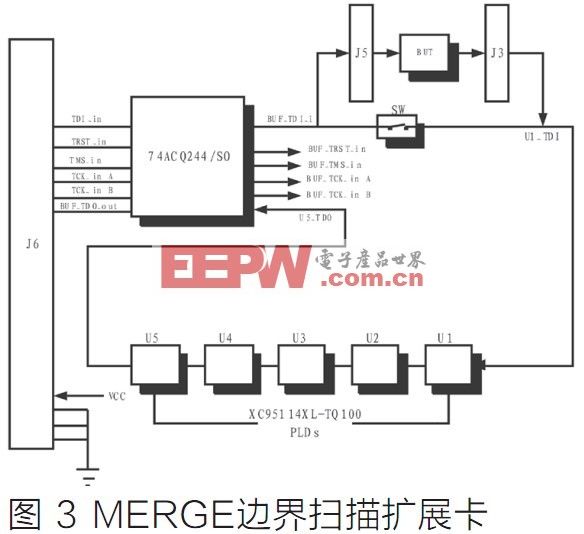

MERGE邊界掃描擴展卡采用符合IEEE 1149.1邊界掃描標準的可測試性設計方案,應用5片XILINX公司的XC95144芯片構建完整的從TDI至TDO的邊界掃描鏈路,其中掃描鏈路的上游電路及下游電路采用74ACQ244對信號進行緩沖及整形,以增強上游電路的扇出能力,同時整板的邊緣連接器采用了牢固可靠、抗腐蝕的歐式Eurocard結構形式的連接器,保證測試信號穩定、可靠。原理圖如圖 3所示。

JTAG-Control-PCI-USB控制器

JTAG-Control-PCI-USB控制器是測試系統筆記本記算機與被測試單元(BUT)進行信號控制的主要部件,實現工控機并行控制指令和數據向符合邊界掃描測試協議的串行指令和數據的轉換。電路采用DSP+CPLD的電路設計模式,DSP芯片采用TI公司的TMS320LF2407A,運行速度可高達40MIPS、具有至少544字的在片雙訪問存儲器DARAM、2K大小的在片單訪問存儲器SARAM,32K的片內程序存儲器FLASH;CPLD選用ALTERA公司的MAX7000S系列的EPM71285,其集成度為600~5000可用門、有32~256個宏單元和36~155個用戶自定義I/O引腳、其3.3V的I/O電平與DSP芯片端口電平兼容、并可通過符合工業標準的I/O引腳JTAG接口實現在線編程及調試。JTAG-Control-PCI-USB控制器是PCI/IEEE 1149.1標準的主控單元,當與BS Interface Pod結合使用時,控制IEEE 1149.1標準自適應測試總線及與之相適應的離散信號。同時,該控制器還可控制施加到測試總線上負責JTAG-Control-PCI-USB控制器與BS Interface Pod進行通訊的低電壓差分信號(基于TIA /EIA-644及IEEE 1596.3標準)。BS Interface Pod模塊

BS Interface Pod模塊,作為測試輸入/輸出信號傳輸的中間級模塊,主要實現JTAG-Control-PCI-USB控制器與BUT之間測試通道的擴展和信號的同步與緩存。FPGA(Altera公司,EP20K160EBC365-1)是本電路設計的核心,其功能是將前級JTAG-Control-PCI-USB控制器發出的不同的控制信號轉換成UUT測試終端能夠識別的TAP控制信號,保證TDI、TCK、TMS、TRST準確施加到UUT的測試端,同時將采集到的TDO信號返回給測試前端控制模塊。74LVC125(Buffer)則用來完成信號暫存,輸出級的74LVC125還可增強信號的扇出能力。整個BS Interface Pod模塊采用抗EMI(電磁干擾)屏蔽封裝,前面板預留4個20Pin的JTAG控制端口,另外設計了一個電源指示燈,用于上電確認。

測試系統軟件設計

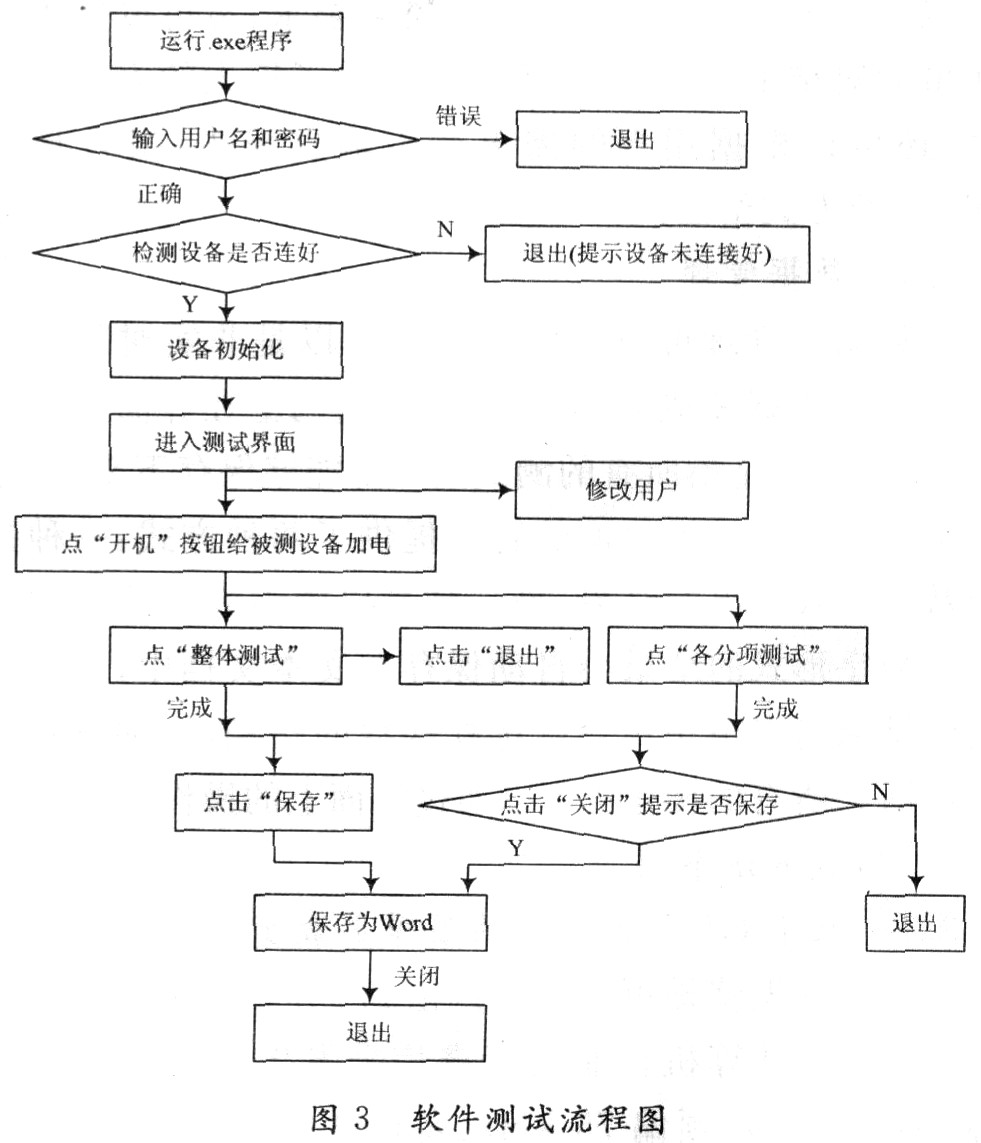

系統軟件在Windows XP環境下采用Visual C++6.0及National Instruments公司的LabWindows 6.0集成開發環境完成。Visual C++ 6.0能夠提供豐富的Windows程序開發功能,靈活性強、編程效率高;LabWindows 6.0提供了多種接口協議、豐富的控件及儀器驅動程序,其支持虛擬儀器技術的特性是其它開發環境無法比擬的,同時它提供了豐富的軟件包接口,為軟件開發提供了極大的方便。

軟件設計采取了軟件模塊化及自頂向下的設計原則,首先根據MERGE原則劃分電路模塊,將測試程序分割成不同的測試模塊,其次采用宏的方式構建標準的測試模塊并優化模塊接口,然后將其它待測模塊與該模塊接口進行有效鏈接,再分別進行編譯及調試,最后一起進行合并構建完整的測試體。在開發過程中,將該軟件分為若干模塊不但減少了軟件的工作量,而且對于函數的公共部分進行了類的封裝,提高了模塊的復用性,同時提高了軟件本身的可測試性。

測試優化

為減少ATE在故障診斷中誤判的概率,系統采用加權偽隨機向量關系生成、插入間隔刷新測試矢量優化測試矢量和測試過程。

(1) 加權偽隨機測試矢量生成:加權偽隨機測試矢量生成能夠利用較短的測試碼長度(即較短的測試時間)達到較高的測試故障覆蓋率。為了縮短測試碼并改進故障覆蓋率,這種測試矢量生成方式可以調節在輸入端產生0或1的概率,有效檢測到難檢測的故障。在偽隨機測試碼中,每個輸入端產生0或1的概率為50%。

(2) 插入式間隔刷新:由于數據線具有一定的電平保持特性,因此對于一組數據總線I/O而言,在BS-Cell處于讀狀態時(如處于Update狀態),Cell單元的Output Enable Control Cell處于有效狀態,測試矢量通過BS-Cell施加至I/O數據總線,如果下一個時鐘節拍,BS-Cell處于寫狀態(如處于Capture狀態),由于數據線的電平保持特性,則有可能在此時間,BS-Cell所Capture回讀的數據為上一個時鐘節拍的Update數據,造成測試不穩定。解決的辦法是在每一次讀狀態結束后,系統根據讀狀態的間隔時間,隨機產生一組與上一組測試矢量不同的數據,命名為*data,對I/O總線進行間隔刷新。

實驗結果及分析

現以某新型雷達點跡處理數字電路為例進行系統功能驗證。整個電路采用DSP+FPGA的設計架構,其主要芯片包括:5片DSP(ADSP21060)、2片FPGA(Atlera Flex EPF10K系列)、8片雙口RAM(QFP封裝),其他E2PROM、HC244(SOP封裝)、HC245(SOP封裝)等。電路設計復雜,芯片多,PCB布局布線密度大,采用ICT、功能測試TPS開發難度大。

利用本邊界掃描自動測試系統,結合MERGE方法,對上述電路板進行TPS開發實驗及故障診斷,測試結果如圖4所示。

插入模擬故障(U8-6 stuck to 0),重新仿真:掃描鏈測試→PASS→B-Scan器件簇測試→PASS→NB-Scan器件簇測試→Failed (Report: Pin(s): U3-25,R26-2,U8-6,R26-1 possible stuck at low,the BS nodes is U31-21(R/W))。

上述仿真結果表明,融合MERGE方法所構建的基于邊界掃描的板級自動測試系統,自動化程度高,故障隔離準確有效。

電子發燒友App

電子發燒友App

評論