目標板通過一個50針接口與接收機相連,通過RD_REQ、RD_PMT、RD_EN、RD_CLK四根控制信號線進行,從接收機內部開辟的存儲空間讀取數據。

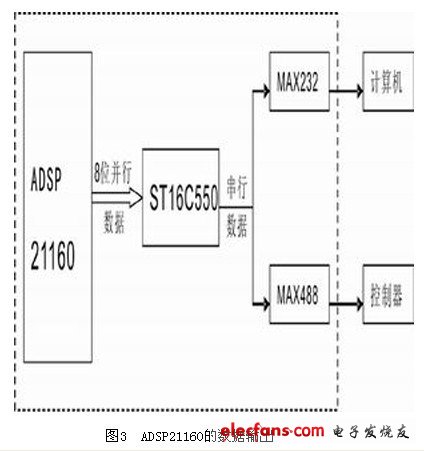

在本系統的設計中,其中間運算數據均采用32位浮點數,輸出結果截取8位有效數字,通過并串轉換器(ST16C550)轉換成串行數據,再分成兩路,一路經過MAX488轉換成差分數據輸送的外部控制器,另一路經過MAX232轉換電平,連接到計算機,實現了系統要求的功能,如圖3所示。

結語

ADSP21160 功能強大,但在電源配置上稍顯復雜。本系統利用2.5V電源輸出作為3.3V的輸出使能,成功的解決了這一問題。另外,在達到系統要求的基礎上,為降低設計難度,對時鐘和數據線都進行了特殊的設計。時鐘采用片外中低頻(20MHz),片內倍頻到最大頻率(80MHz)的設計,降低了PCB板對中高頻布線要求;數據線通過懸空0位地址,將片外線寬從64位降低至32位,大大降低了ADSP21160周邊的線密度,從而大大降低了PCB板的布線難度。

用戶評論

共 0 條評論