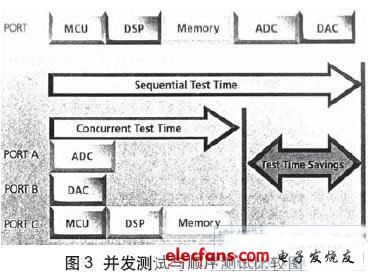

在大規模器件(如無線基帶SoC處理器)中,有無數個模擬芯核,并行地測試這些芯核需要大量的模擬資源。若按4個測試點,全并行、并發測試式計算,需提供28個數字化儀,這在當前的ATE系統中還難以實現。

一種新型模塊體系結構

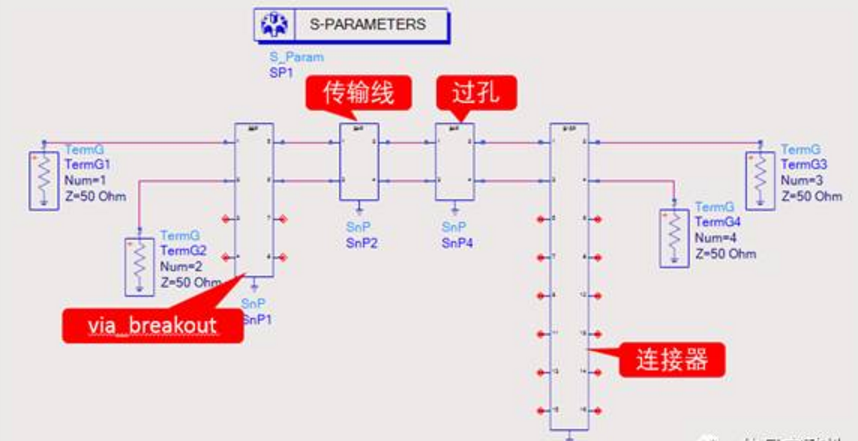

測試當前消費品器件中使用的各種模擬芯核,需要高度并行,低開銷的解決方案。若在每個模塊中組合幾個模塊功能,能相應地減少每個模擬模塊的占用空間,這樣,就有更多的空間留給必需的數字模塊。一個內置8個獨立Arb或數字化儀單元的模塊具有靈活地配置的優點:或只用作數字化儀單元,或是數字化義與Arb單元的組合。

降低消費類器件測試的COT不僅要解決ATE測試系統的并行測試方案,還要減少并行測試帶來的ATE開銷。多芯核是當前SoC消費類器件的主要特征,在對ATE硬件進行體系結構改進時同樣要考慮上面兩個因素,這樣才能得到最佳的測試解決方案。

用戶評論

共 0 條評論