可測試性定義為:產(chǎn)品能及時準確地確定其狀態(tài),隔離其內(nèi)部故障的設(shè)計特性,以提高產(chǎn)品可測試性為目的而進行的設(shè)計被稱為可測試性設(shè)計。

2014-12-18 16:31:25 678

678 損耗。(5)利用轉(zhuǎn)換器的并聯(lián)結(jié)構(gòu)來減少固定損耗。第一種方法對于降低開關(guān)損耗極為有效,但問題是因峰值電流和峰值電壓所導致的固定損耗將會增加。第二種方法是為解決該問題而開發(fā)的有源緩沖器(Active

2015-12-18 10:50:32

是人們在應(yīng)用該芯片時必須解決的關(guān)鍵問題。本文提出了一種簡單易行的測試方法,并在基于ADSP21062的雷達信號處理系統(tǒng)調(diào)試中獲得了成功,驗證了該方法的可行性。

2019-07-19 08:16:35

摘要:為了實現(xiàn)對非相干雷達的接收相參處理,基于數(shù)字穩(wěn)定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設(shè)計了一種基于FPGA的DSU硬件實現(xiàn)方法。實驗結(jié)果表明

2019-06-28 08:27:33

中,數(shù)字信號處理系統(tǒng)經(jīng)常要進行高速、高精度的FFF運算。現(xiàn)場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數(shù)字信號處理算法的物理結(jié)構(gòu)。用FPGA實現(xiàn)FFT處理器具有硬件系統(tǒng)簡單、功耗低的優(yōu)點

2019-07-03 07:56:53

越來越力不從心。 以FPGA為代表的可編程邏輯器件以其工作穩(wěn)定、速度快、靈活的可編程能力等特點,獲得了越來越廣泛應(yīng)用。本文提出了一種基于FPGA的振動信號采集處理系統(tǒng);該系統(tǒng)具有實時性高,糾錯能力強等

2019-07-01 06:11:15

摘要:針對現(xiàn)有小型無人機導航系統(tǒng)的解算速度慢、多處理器核心臃腫可靠性差的缺點,實現(xiàn)了一種僅使用單一FPGA作為數(shù)據(jù)處理核心的小型高速導航解算系統(tǒng)。該系統(tǒng)對飛機運動方程組和導航方程組進行并行化分

2019-07-03 06:57:34

可實現(xiàn)醫(yī)療資源共享,提高邊遠地區(qū)的醫(yī)療水平,因此具有特別旺盛的生命力。HHCE系統(tǒng)提供一種對于家庭、社區(qū)醫(yī)療、出診醫(yī)生有效便捷的醫(yī)療監(jiān)測解決方案,具有心電信號監(jiān)測功能的監(jiān)測器是HHCE系統(tǒng)的重要

2019-07-08 08:09:54

遇到的問題1. 編碼器信號,用來計量長度,如果需要同時測量當前實時速度,在不增加接口的情況下,實現(xiàn)較為準確實時的測速2. 簡單的M法速度,對于低速信號,測量精度較差,實時性也不高。測速方法之前

2021-09-13 07:08:01

,是獲取地面信息的重要手段,因而在軍用和民用領(lǐng)域中都獲得了廣泛的應(yīng)用。合成孔徑雷達模擬技術(shù)是一種用模擬的方法來研究SAR的技術(shù),在SAR的研究和研制工作中具有十分重要的作用。該技術(shù)能模擬出SAR的回波

2019-07-22 06:29:35

實際的測試中,它不需要借助于復雜和昂貴的測試設(shè)備,并且提供一種獨立于電路板技術(shù)的測試方法。采用邊界掃描測試技術(shù)進行集成電路設(shè)計和印制電路板設(shè)計,其最大的優(yōu)點是測試過程簡單,顯著地減少了生產(chǎn)、實驗

2018-09-10 16:50:00

,消除DDR BGA探頭探測效應(yīng)后的裕量可用于設(shè)計中容限更低的元器件。本文將介紹一種新的、可擴展DDR BGA探頭帶寬的探頭校正方法,以增加信號完整性測試的裕量,并最大程度降低DDR BGA探頭引起的誤差。

2019-07-23 07:10:11

的是,這種專門的電路還不是大多數(shù)高端Arm系統(tǒng)的標準功能。在我們最近與塞浦路斯大學的合作研究中,我們成功地開發(fā)了一種更通用的方法來監(jiān)測處理器中的電壓噪聲。這種技術(shù)依賴于使用外部天線和頻譜分析儀的處理器發(fā)出

2022-11-01 14:48:58

的不良相位失調(diào)。此外,這種補償必須持續(xù)存在。本文介紹一種在工廠測試和工作期間測量多個發(fā)射機之間的相位差,以便基帶處理器補償這些失調(diào)的方法。

2019-07-23 06:59:40

模型【DOI】:CNKI:SUN:IKJS.0.2010-03-020【正文快照】:目前進行測試性評估與分析主要有兩種方法:一種是基于經(jīng)驗的工程加權(quán)方法,如GJB2547中給出的加權(quán)平均法;另外一種

2010-04-22 11:28:58

與柵極驅(qū)動器的熱和噪聲隔離。然而,電流均分會更復雜,因為電流感測信號路由到控制器。還有另外的控制器-驅(qū)動器延遲,這是因為它們是分離的IC。 另一種方法是采用一個帶集成柵極驅(qū)動器和內(nèi)置同步和電流均分

2009-10-22 17:10:37

流水方式對復數(shù)數(shù)據(jù)實現(xiàn)了加窗、FFT、求模平方三種運算。整個設(shè)計采用流水與并行方式盡量避免瓶頸的出現(xiàn),提高系統(tǒng)時鐘頻率,達到高速處理。實驗表明此處理器既有專用ASIC電路的快速性,又有DSP器件的靈活性的特點,適合用于高速數(shù)字信號處理。

2012-08-12 11:49:01

增加了微處理器的復雜性,帶來了諸如材料、功耗、光刻、電磁兼容性等一系列問題。因此處理器設(shè)計人員開始尋找新的途徑來提高處理器的性能。Intel公司于2002年底推出了超線程技術(shù),通過共享處理器的執(zhí)行資源,提高CPU的利用率,讓處理單元獲得更高的吞吐量。

2019-09-19 06:59:47

本文概述了開發(fā)這種系統(tǒng)所必須面對的各種設(shè)計挑戰(zhàn),并講解了Altium公司的最新電子設(shè)計環(huán)境Nexar如何為FPGA設(shè)計提供一種全新的方法。這種方法不僅可將處理器有效地集成入FPGA之中,而且成為一種挖掘現(xiàn)有以及未來大容量、低成本FPGA部件應(yīng)用潛力的系統(tǒng)級

2021-05-08 06:02:24

Teledyne e2v為系統(tǒng)設(shè)計師提供的定制方案處理器功耗的背景知識三種調(diào)整處理器系統(tǒng)功耗的方法

2021-01-01 06:04:09

本文介紹了一種提高RS485總線通信速度的設(shè)計方法。

2021-06-02 06:29:06

本文介紹一種面向基站平臺處理單板的基于融合SoC處理器的平臺軟件解決方案。

2021-05-17 06:36:12

)中《保持電容性負載穩(wěn)定的六種方法》欄目的第六種方法(也是最后一種方法)。這六種方法包括Riso、高增益和CF、噪聲增益和CF、輸出引腳補償以及具有雙通道反饋的RISO。在第10部分中,我們將闡述具有

2009-09-25 09:31:04

本文將對基于NiosII的SOPC多處理器系統(tǒng)的實現(xiàn)原理、設(shè)計流程和方法進行詳細的討論。

2021-04-19 08:51:23

求大佬分享一種基于電磁流量計信號轉(zhuǎn)換器的校驗器設(shè)計方法研究

2021-04-07 06:31:20

;S RTO-/ RTP-K133高級抖動分析選件引入了一種分析方法來分離出各個抖動成分,如隨機性抖動和確定性抖動(如數(shù)據(jù)相關(guān)抖動和周期性抖動)。這種方法基于一種參數(shù)信號模型,該模型可以完全表征被

2020-02-11 09:39:41

摘要 介紹了利用MATLAB信號處理工具箱進行FIR濾波器設(shè)計的三種方法:程序設(shè)計法、FDATool設(shè)計法和SPTool設(shè)計法,給出了詳細的設(shè)計步驟,并將設(shè)計的濾波器應(yīng)用到一個混和正弦波信號,以驗證濾波器的性能。關(guān)鍵詞MATLAB,數(shù)字濾波器,有限沖激響應(yīng),窗函數(shù),仿真

2019-07-23 08:28:03

一種擴展微處理器/單片機外部中斷接口的方法一、普通單片機對數(shù)字量輸入信號的處理普通的微處理器(例如單片機)對數(shù)字量輸入信號的處理一般采用掃描輪詢和中斷處理的方式。采用掃描輪詢的方式很大程序上取決于

2016-10-28 19:56:17

求大佬分享一種基于遙測的移動艙室內(nèi)氣體檢測方法

2021-04-09 06:17:33

本文提出了一種基于TMS320C6701信號處理器的高性能信號處理模塊的設(shè)計方案,設(shè)計了具有一定通用性的并行信號處理模塊,該模塊具有高速互連接口,可以根據(jù)應(yīng)用系統(tǒng)的需求構(gòu)成不同的并行系統(tǒng),完成各種信號處理任務(wù)。

2021-04-02 07:30:14

模型的適用性決定多核處理器能否以最低的代價提供最高的性能。程序執(zhí)行模型是編譯器設(shè)計人員與系統(tǒng)實現(xiàn)人員之間的接口。編譯器設(shè)計人員決定如何將一種高級語言程序按一種程序執(zhí)行模型轉(zhuǎn)換成一種目標機器語言程序

2011-04-13 09:48:17

如何利用ARM9處理器如何設(shè)計一種SD卡電路呢?

2022-07-19 14:24:57

如何對紫外線強度進行測試?有哪幾種方法?如何去制作一種基于GY-ML8511的傳感器模塊?

2021-08-06 07:34:19

嵌入式處理器分為哪幾種?加入HAL的嵌入式軟件有什么目的和意義?如何去開發(fā)一種嵌入式程序?有哪幾種方法?

2021-07-02 06:54:34

如何去設(shè)計一種基于RK3399處理器的RT*** u***轉(zhuǎn)網(wǎng)口驅(qū)動呢?

2022-03-04 09:55:28

一、什么是CacheCache是一種容量比較小,但訪問速度比較快存儲器。由于處理器的速度遠高于主存,處理器直接從內(nèi)存中存取數(shù)據(jù)要等待一定周期,而Cache位于處理器與主存之間,保存著最近一

2016-08-31 16:30:26

有時人們?yōu)榱私档统杀荆捎秒娮桦娙輼?gòu)成的復位電路,這是一種比較危險的做法。主要表現(xiàn)在下面幾個方面: (1)這種電路產(chǎn)生的復位閾值非常不準確,在復位信號無效后,電源電壓還不夠高,以至于微處理器還不

2020-07-08 09:46:44

Vernier陽極探測器的結(jié)構(gòu)Vernier陽極電子讀出電路設(shè)計如何設(shè)計一種Vernier陽極探測器的信號處理電路?

2021-04-20 06:35:13

給大家介紹的是微處理器CPU性能測試基準Dhrystone。 在嵌入式系統(tǒng)行業(yè)用于評價CPU性能指標的標準主要有三種:Dhrystone、MIPS、CoreMark,其中Dhrystone是一種

2021-12-15 08:44:56

――EnergyBench。同協(xié)會的其他性能benchmark一起使用,EnergyBench可以測試處理器在進行一系列標準應(yīng)用任務(wù)時的功耗大小。有了這樣一個同性能測試緊密聯(lián)系的功耗標準測度,設(shè)計工程師就能比較多個供應(yīng)商提供的微處理器的性能/功耗,從而選擇一款最適合自己應(yīng)用的產(chǎn)品。

2019-08-22 07:30:54

什么是信號處理器?信號處理器測試現(xiàn)狀如何?怎樣去提高信號處理器的測試性?

2021-05-10 06:55:08

怎樣去設(shè)計一種RTU無線電遙測系統(tǒng)?RTU無線電遙測系統(tǒng)有哪應(yīng)用?

2021-05-27 06:16:09

怎樣去使用STMF103的處理器和外設(shè)呢?怎樣去設(shè)計一種基于STMF103處理器的微型四軸飛行器呢?

2021-11-09 07:07:08

微處理器是什么?微處理器是有哪些部分組成的?怎樣去選擇一種合適的嵌入式處理器呢?

2021-12-24 07:20:16

以下信息提供了有關(guān)推測性處理器漏洞的常見問題解答。

你能用通俗易懂的話解釋這個問題嗎?

·這兩種攻擊都利用了現(xiàn)有的旁路技術(shù),并可能導致通過使用惡意軟件訪問少量數(shù)據(jù)。

·使用這種方法并在本地運行的惡意

2023-08-25 07:15:47

對于一個從事電子信息行業(yè)的人員,對于數(shù)字信號處理器應(yīng)該特別了解了。數(shù)字信號處理器,簡稱為DSP,可以說是一種專用的微處理器,從其體系結(jié)構(gòu)方面來看,可以針對數(shù)字信號處理當中,進行必要的優(yōu)化。DSP

2020-12-09 14:01:39

總而言之,

我有一個在 ESP8266 上使用 painlessMesh 的項目。

已經(jīng)工作了好幾個月了。

不幸的是,最新版本的 8266 內(nèi)核導致 painlessMesh 編譯錯誤。

有沒有一種方法可以在“附加板管理器 URL”中指定舊版本

2023-05-08 08:25:01

有沒有一種方法直接從芯片上讀取27443的程序?

2019-09-17 13:45:00

本文用CPLD控制圖像的讀入,以TMS320VC5402 DSP作為處理器,并結(jié)合CA3318CE A/D轉(zhuǎn)換器介紹一種CCD圖像采集處理系統(tǒng)的設(shè)計方法。根據(jù)課題研究,將此系統(tǒng)應(yīng)用于手寫體數(shù)字的采集和識別中。如果配以適當?shù)墓鈱W系統(tǒng),便可以實現(xiàn)光-機-電-算一體化設(shè)計。

2021-04-22 06:04:10

分析了I2C總線的工作原理及其特點提出一種在I2C總線應(yīng)用下的EEPROM測試方法

2021-04-09 06:09:12

協(xié)議用于維護由于多個處理器共享數(shù)據(jù)引發(fā)的多處理器數(shù)據(jù)一致性問題。論述了一個適用于64位多核處理器的共享緩存設(shè)計,包括如何實現(xiàn)多處理器緩存一致性及其全定制后端實現(xiàn)。本文介紹了一種共享高速存儲器模塊

2021-02-23 07:12:38

本文設(shè)計了一種在多處理器系統(tǒng)中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數(shù)據(jù)存儲器加載數(shù)據(jù)時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

本文以MP3解碼器為例,介紹了一種在嵌入式Linux系統(tǒng)下配置使用處理器片內(nèi)SRAM的應(yīng)用方案,有效提高了代碼的解碼效率,降低了執(zhí)行功耗。該方案不論在性能還是成本上都得到了很大改善。

2021-04-26 07:01:55

求一種基于ARM Cortex-M處理器的音頻解決方案

2021-06-01 06:32:51

本文介紹了一種基于FPGA及NiosII軟核處理器與TFT-LCD接口的方法。它直接采用CPU對存貯器的讀寫,實現(xiàn)了對TFT-LCD屏的實時操作。它具有直接、有效和速度快等特點。該設(shè)計使CPU對TFT-LCD的控制極其簡單化。

2021-05-08 07:21:11

討論了一種基于FPGA的64點FFT處理器的設(shè)計方案,輸入數(shù)據(jù)的實部和虛部均以16位二進制數(shù)表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發(fā)平臺對處理器各個的模塊進行設(shè)計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結(jié)果正確。

2021-04-29 06:25:54

本文根據(jù)FPGA的結(jié)構(gòu)特點,圍繞在FPGA上設(shè)計實現(xiàn)八位微處理器軟核設(shè)計方法進行探討,研究了片上系統(tǒng)的設(shè)計方法和設(shè)計復用技術(shù),并給出了指令集和其調(diào)試方法,提出了一種基于FPGA的微處理器的IP的設(shè)計方法。

2021-04-29 06:38:37

求一種多處理器并行計算機系統(tǒng)的設(shè)計方案

2021-04-27 06:58:57

求一種基于FPGA芯片的嵌入式PLC處理器的設(shè)計方案。

2021-05-06 08:24:19

求大神分享一種基于FPGA的級聯(lián)結(jié)構(gòu)FFT處理器的優(yōu)化設(shè)計

2021-05-06 07:34:53

的修改方面缺乏靈活性。本文介紹一種嶄新的基于Matlab與QuartusII的DSP處理器的設(shè)計軟件DSP Builder,詳細介紹了其設(shè)計流程與優(yōu)點,并以DDS直接數(shù)字合成器的實現(xiàn)為例說明用該軟件來設(shè)計DSP處理器的方法以及與Matlab、QuartusÊ之間的關(guān)系。

2011-03-03 10:05:43

本文介紹一種三軸正交型傳感器正交性的軟件修正方法。

2021-05-07 06:53:11

芯片功能測試常用5種方法有板級測試、晶圓CP測試、封裝后成品FT測試、系統(tǒng)級SLT測試、可靠性測試。

2023-06-09 16:25:42

數(shù)字音頻處理器的結(jié)構(gòu)是由哪些部分組成的?怎樣去設(shè)計一種數(shù)字音頻處理器?

2021-06-03 07:03:59

怎么設(shè)計一種弱信號處理模塊測試系統(tǒng)?弱信號處理模塊測試系統(tǒng)的主要功能有哪些?如何弱信號處理模塊測試系統(tǒng)的硬件設(shè)計?如何弱信號處理模塊測試系統(tǒng)的軟件設(shè)計?

2021-04-15 06:54:46

一種基于單片機及MODEM的MTU、RTU無線電遙測系統(tǒng)

2021-06-03 06:09:06

怎樣設(shè)計FIR濾波器結(jié)構(gòu)?怎樣設(shè)計級聯(lián)型信號處理器?如何對級聯(lián)型信號處理器進行仿真測試?

2021-04-28 07:04:01

嗨,有沒有另一種方法來測量RTD傳感器而不使用IDAC?TKS。

2019-10-11 09:33:17

高級處理器特性能否提高編碼效率?

2021-04-26 06:41:08

介紹了一種基于PXI總線的測試平臺,以實現(xiàn)遙測系統(tǒng)中PCM碼的持續(xù)無丟幀存儲和模擬各種傳感器信號的功能。

2010-11-08 17:04:42 21

21 用成型濾波器組提高測距精度的一種方法

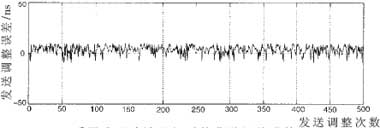

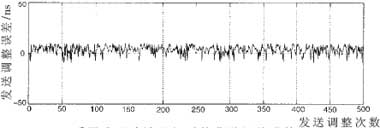

在許多測距系統(tǒng)中,用戶端接收到基站發(fā)送的幀信號后,便以該幀中特定的位置(稱為幀參考時標)為基準發(fā)送

2009-10-17 10:04:20 570

570

針對遙測信號的精度要求,設(shè)計了一種便攜式遙測信號組件通用檢測裝置。采用主要模擬產(chǎn)生多種模擬量信號、開關(guān)量信號和數(shù)字量信號作為導彈遙測信號組件調(diào)試或測試的數(shù)據(jù)輸入源,并將導彈遙測信號組件輸出的串行信號

2017-10-30 18:31:34 7

7 針對飛行器遙測振動信號具有典型的非平穩(wěn)、非線性及強噪聲干擾的特征,提出了一種變步長KLMS遙測振動信號降噪方法。首先利用遙測時序分析法將遙測振動信號序列分為平穩(wěn)飛行段落和特征飛行段落,以平穩(wěn)飛行段落

2017-11-06 17:56:47 12

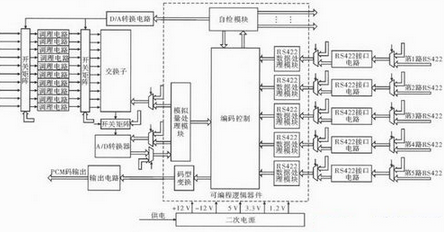

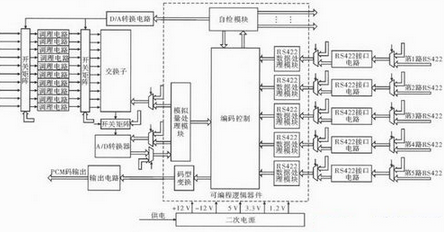

12 產(chǎn)品的質(zhì)量,降低產(chǎn)品的全壽命周期費用具有重要意義。隨著集成電路設(shè)計方法與工藝技術(shù)的不斷進步,集成電路的可測性已經(jīng)成為提高產(chǎn)品可靠性和成品率的重要因素。文中針對遙測產(chǎn)品中信號處理器的設(shè)計原理,通過增加BIT以提高信

2017-12-13 17:47:59 6328

6328

電子發(fā)燒友App

電子發(fā)燒友App

評論