PCI-SIG將PCIe的鎖相回路(PLL)列為基本測試項目,目前有幾種可用于執行該測試的手法。本文中將以PCIe 2.0的規格要求為例,概述幾種較為常見的方法,并針對其優勢與劣勢進行簡單比較。

為了在系統中控制抖動抑制效能,PCIe 2.0規定了板載PLL的操作回路回應特性,特別是最小和最大的PLL回路帶寬和峰值。表1列出了規格中所述的這些PLL回應特性。

?

目前有幾種量測PLL回路響應的方法,取決于所使用的測試儀器類型。正如預期,這些方法都會在測試準確度、測試速度(吞吐量)、易用性、易設定性及初始成本等方面有所取舍。此外,有些方法還具有不同的限制,造成其無法普遍用于所有的PLL類型。

雖然所有的方法均可測試對規格要求的兼容性,不過,有些方法可提供額外的實用數據,讓頻率設計人員能優化其設計。

為了維持一致性和可重復性,所有的方法均假定采用SIG提供的標準測試夾具,即兼容性基板(CBB) 2.0版。

以頻譜分析儀為基礎的量測是分析PLL回路回應的傳統方法(圖1)。此方法將采用兩部儀器;具有掃描功能的正弦訊號產生器,以及頻譜分析儀。訊號產生器用于調變的參考頻率工作周期,而發射頻率輸出則是在連接頻譜分析儀的數據信道上進行量測。

圖1 以頻譜分析儀為基礎的測試。

頻譜分析儀測試法僅適用特定PLL拓撲型態

因為同步訊號產生器以追蹤頻譜分析儀的本地振蕩器方法并不實際,量測作業是由繪制峰值振幅量測的封包使用大多數頻譜分析儀中所提供的「峰值保持」功能來進行。振蕩器會連續掃頻,比頻譜分析儀的掃描速度快得多。

輸出頻譜會顯示峰值和數據速率基波和所有諧波,且側頻帶斜率是PLL帶寬的曲線圖。因為分析儀的輸出為絕對值,所以不會進行縮放。相反,相關的量測是使用配對的增量光標(若可用)或手動使用單一光標(記錄絕對標稱值和峰值,并從中減去測試極限)來進行。

調變參考頻率的方法對此測試方法能否具備普遍適用性具有一定的影響力。在此測試方法中,CBB上的焊接式跳線配置為差動測試訊號與CBB上產生的100MHz振蕩器的總和。外部的BALUN會放置于訊號產生器與主板上的求和點之間,以調變差動頻率的兩個部分。結果是振幅-調變頻率訊號的交叉點基本上是由外部正弦來源從差動訊號的中心移動。

因為交叉點已改變,并非100MHz參考振蕩器的頻率,所以此方法實際上會調變PLL參考的工作周期。這對單邊緣相位偵測器而言,將呈現為相位調變,因此在這個測試案例中是可行的。然而,若要在高達5GT/s的設計上減少抖動,許多設計人員將會選擇采用PLL設計(在上升和下降邊緣比較相位),以降低相乘比率。 這類PLL僅會追蹤頻率的總周期,不會響應工作周期變化。此時便無法便使用此參考調變方法來分析其特性。

由于PLL參考的相位調變是由振幅調變(AM)100MHz參考頻率而產生,因此頻譜分析儀上的側頻帶包含調幅和調頻(FM)成分。工程師在解譯結果時,必須需格外謹慎,以確保量測所得的數據僅包含PLL帶寬。

如同所有使用掃頻外差頻譜分析儀所進行的量測,帶寬分辨率和掃描時間之間存在著直接的取舍問題。由于測試極限范圍縮小至個位數MHz,即需要相對較低 的頻率分辨率帶寬(通常是30kHz)。 外差頻譜分析儀中的偵測器僅會量測幅度,所以無法使用回路響應的相位數據。雖然對于基礎規格的測試兼容性并不要求相位,不過,頻率設計者仍可將其用于確定PLL相位余裕,這對評估設計而言是一個非常有力的工具。

以頻譜分析儀為基礎的方法提供了寬動態范圍的振幅,可有效簡化測試設定。振幅分辨率限制在約1dB或略佳的實用值,在峰值僅有1dB的情況下測試帶寬時,此值將為余裕。

測試設定有些復雜,需要設定訊號產生器的操作參數及頻譜分析儀的量測參數。在設定訊號產生器振幅時務必小心謹慎,以避免過度驅動CBB求和節點。預先儲存的設定可以用來簡化此程序;然而,所產生的曲線圖仍需要進行一些解譯和手動光標掃描,以讀取參數值。

手動放置游標常常是在量測中誤差和不可重復性的來源。在一些情況下,DUT具有與頻率數據速率不相關的抖動頻譜分量,如切換電源的諧波為例。這些峰值可能會發生在正在進行PLL響應量測的基線區域,造成用戶無法在實際軌跡上放置量測光標,導致用戶需猜測峰值是否在此位置。

示波器分辨率優于頻譜分析儀 然亦受限于PLL拓撲

以示波器為基礎的方法使用了數字示波器來代替頻譜分析儀。最直接的方法是使用示波器的FFT能力來產生頻域數據。相較于頻譜分析儀,此方法提供了幾項改善功能:頻率分辨率是采樣率和內存長度的函數,可針對量測的要求進行優化處理。訊號擷取和量測吞吐量的速度遠優于頻譜分析儀中的慢速掃描本地振蕩器。

相較之下,動態范圍小一個數量級,要求示波器在量測之前設定適當的比例因子,分辨率比頻譜分析儀更好。但是,最佳示波器的動態頻率響應準確為+/-1dB量級,將量測準確度限制至約1dB。垂直縮放功能在本質上為線性函數,需要參數數學運算以轉換為dB。

與頻譜分析儀不同的是,在示波器中的FFT計算可產生相位回應及大小。

以示波器為基礎的方法使用與頻譜分析儀方法相同的訊號產生器組態,因此這兩種方法均需要額外的儀器,也同樣無法與PLL搭配使用,進而需采用兩部邊緣相位偵測器。

誤碼率測試儀方法又快又精準

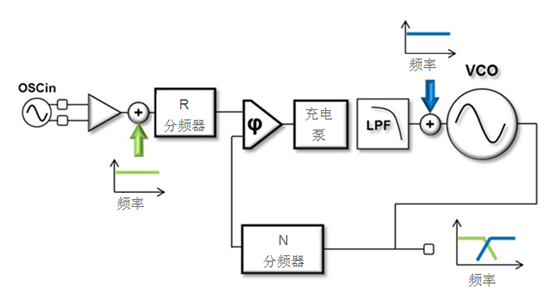

高效能誤碼率測試儀(BERT)可配置為直接量測PLL回路響應(圖2)。BERT 同時具有刺激和量測能力,可讓用戶以單一儀器來執行此測試。針對PLL量測,BERT必須可利用正確的直流偏移,將「壓力」(校準的抖動)注入碼型產生器100MHz差動輸出。

圖2 使用BERT進行PLL量測。

以BERT為基礎的量測使用與頻譜分析儀和示波器方法不同的方法來刺激待測PLL。BERT并不是將失真的訊號總結入兼容性基板上所產生的100MHz參考振蕩器,而是透過對碼型產生器進行程序設計來提供參考訊號,以200Mbit/s的速率輸出1010碼型(頻率)。這相當于100MHz的差動頻率。應力產生器設定為將正弦抖動注入至碼型輸出,可針對波形的周期進行相位調變。此組態要求CBB上的電阻器/跳線需設為外部參考頻率輸入。

在待測PLL輸出中的直通抖動是由BERT誤碼儀量測而得。透過步進調整正弦抖動應力的頻率,即可產生抖動轉移函數曲線圖。額外的數學處理功能則可產生PLL回路響應曲線圖。

如同以示波器為基礎的方法,使用者可手動執行此量測。然而,已錄制好的軟件選項將會自動執行任務,盡可能地減少了潛在的使用者錯誤;同時還可加快量測速度,并提供直接的通過/失敗測試。

相較于頻譜分析儀或示波器可提供的功能,以BERT為基礎的量測提供了更高的準確度和可重復性。透過自動化軟件,用戶只需要幾秒鐘就可得到準確結果。

頻率資料回復儀適用各類PLL拓撲

高效能頻率數據回復儀器可用于量測PLL回路回應(圖3)。相較于前述其他方法,此方法提供了幾項優勢。這些儀器在本質上屬于「儀器等級」的頻率數據回復單元,使用復雜的PLL設計,可在廣泛頻率頻率上操作,并具有校準和使用者可程序設計的回路響應。為了利于進行自我校準,這些儀器包含直接數字合成器(DDS)以生產各種訊號。

圖3 頻率數據回復儀器量測方法。

DDS的輸出可在PLL測試組態中由外部提供,以作為參考頻率。如同以BERT為基礎的測試方法,頻率數據回復儀器方法僅需單一儀器即可產生刺激并量測輸出。

然而,DDS來源頻率數據回復儀器為基礎的方法確實與頻譜分析儀及示波器方法不同,其參考訊號會經過程序設計以維持完美的 50%工作周期。這可讓使用者進行所有的PLL拓撲通用測試,包括具有雙邊緣相位偵波器。可在調變參考相位時維持50%工作周期的功能是以BERT或頻率數據回復為基礎的測試方法的獨特內建功能。

來自兼容性基板上用戶選定信道的輸出訊號會路由至頻率數據回復儀器的數據輸入接頭。在此處,頻率會透過儀器的精密PLL進行回復。相位誤差偵測器的輸出會進行數字化并處理,以確定相對相位誤差。來自數字化波形的正弦和余弦數據會用來計算通過待測PLL的相位調變的相位和幅度(相對于頻率)。因為相位誤差量測會同步至參考頻率的調變,所以可針對量測建立關聯,以有效將動態范圍提高到75dB以上。

相較于其他方法,除了在調變測試訊號的相位時維持50%的工作因子,以頻率數據回復為基礎的方法還提供了幾項優勢。在維持由頻譜分析儀提供的動態范圍之外,還可能具備0.01dB的振幅分辨率,這提供了最高的準確度和量測可重復性。

同時,這種方法也具有高頻率分辨率,且在不到10秒的時間內即可產生一個完整的量測。量測方法本身即會產生相位圖及大小。雖然在驗證兼容性時僅需要在-3dB點的頻率和峰值位準,不過,額外的相位圖可讓使用者用于判定其PLL設計的相位余裕;這是一個非常強大的設計評估工具。最后,此方法也能產生PLL 增益(亦稱為抖動傳遞函數,JTF)圖。

量測PCIe鎖相回路 BERT/頻率資料回復最理想

本文中所介紹的四種方法均可執行PCIe 2.0基本規格要求的PLL回路響應量測;然而,僅有由頻率數據回復所共享的相位調變方法和以BERT為基礎的方法可與所有PLL設計搭配使用。這些方法在設定及結果解釋的復雜性、分辨率和準確度、可重復性和初始成本等方面有顯著不同。

以頻率數據回復為基礎的方法是單一儀器解決方案,能以最簡單的設定和最低的成本提供高準確度、高分辨率和可重復性;亦具有提供額外數據的優點,可讓PLL設計人員更充分地了解其設計的效能。

電子發燒友App

電子發燒友App

評論