據2001 年的國際半導體技術未來發展預示,到2016 年MOSFETs 的物理溝道長度將達到低于10nm 的尺寸[1],而這種尺寸條件會影響到MOSFETs 的基本工作原理,因此必須尋找新的替代器件。單電子晶體管(Single-Electron Transistor,SET)具有較小體積、較低功耗和較高開關速度性能,其高度集成化遠遠超過目前大規模集成化的極限,被認為是下一代超大規模集成電路的理想器件[2]。同時SET 與MOSFET 具有很好的互補性:SET 的功耗低、可集成度高、有庫侖振蕩新特性等優點,而MOSFET 器件的高速、高電壓增益和高驅動特性可以補償SET 固有的缺點。因此,將來SET 與MOSFET 的混合在集成電路中共同占主導地位,對于解決納米尺寸的集成電路具有很好的應用前景[3, 4]。

單電子進出量子點(島)使其上的靜電勢和能量狀態發生很大變化,它就可以作為傳遞數值信息的載體,制備成單電子存儲器和單電子邏輯電路等等。因此,SET 在現代電路的微電子領域有潛在的應用價值,特別是在計算機和數字系統中,經常要對兩個數的大小進行選擇決策,因此,本文基于數字邏輯電路的設計思想,首先研究了雙柵極SET 的輸入特性,再利用SET/MOSFET 通用方波門特性討論了具有‘與’、‘或’和‘異或’等功能的電路,并利用這些電路構造了一位比較器電路結構,最后用SET 的MIB 模型[5]進行了仿真驗證。

2. 混合SET/MOSFET 結構與特性

2.1 雙柵極SET 的特性

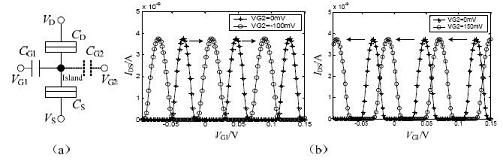

SET 由源極、漏極、與源漏極耦合的量子點(島)、兩個隧穿結和用來調節控制量子點中電子數的柵極組成。雙柵極單電子晶體管可以等效為一個四端元件[6],如圖1(a)所示。圖中CD和CS為隧穿結電容, RD和RS為隧穿結電阻,CG1和CG2為柵極電容,VG1和VG2為柵極電壓,VDS為偏置電壓。

圖1 (a)雙柵極SET的等效示意圖 (b)雙柵極SET的I-V特性

當漏極與源極間電壓VDS不變時,隨著柵極電壓VG1的變化,兩個隧穿結上電壓也隨之相應變化,當隧穿結上電壓大于開啟電壓時,就會發生電子隧穿效應,即電子離開量子點(島),隧穿出一個結;或者電子隧穿一個結,進入到量子點(島)。這種隧穿過程隨著VG的變化呈現為周期性如圖1(b)所示。當VDS較小,漏極與源極間電流iDS表現出所謂的庫侖振蕩形式,其振蕩電壓的間隔是e/CGS1(e 是基本電荷)。另外,當VGS2<0 時,相位向右移動;當VGS2>0 時,相位向左移動。但如果VGS2<0 且VGS2較大時,會產生較高的勢壘,阻礙了隧穿電流的產生,所以GS2 V 取值一般不應太小[7]。

2.2 雙柵極SET 與MOSFET 的混合特性

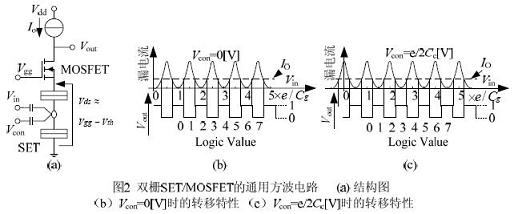

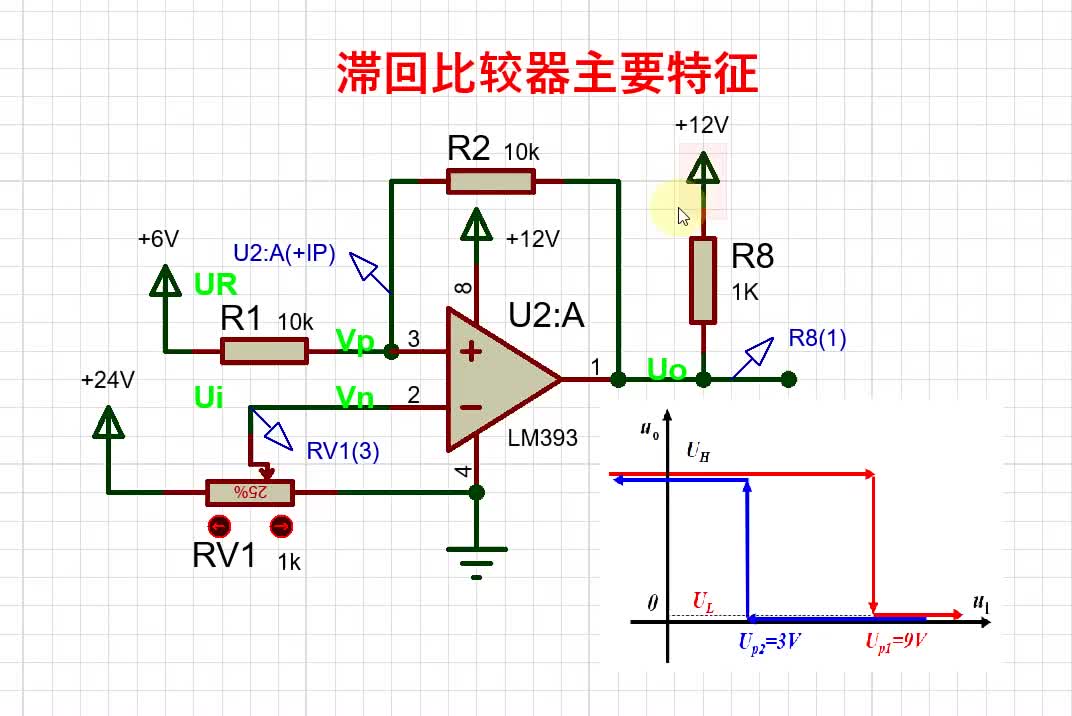

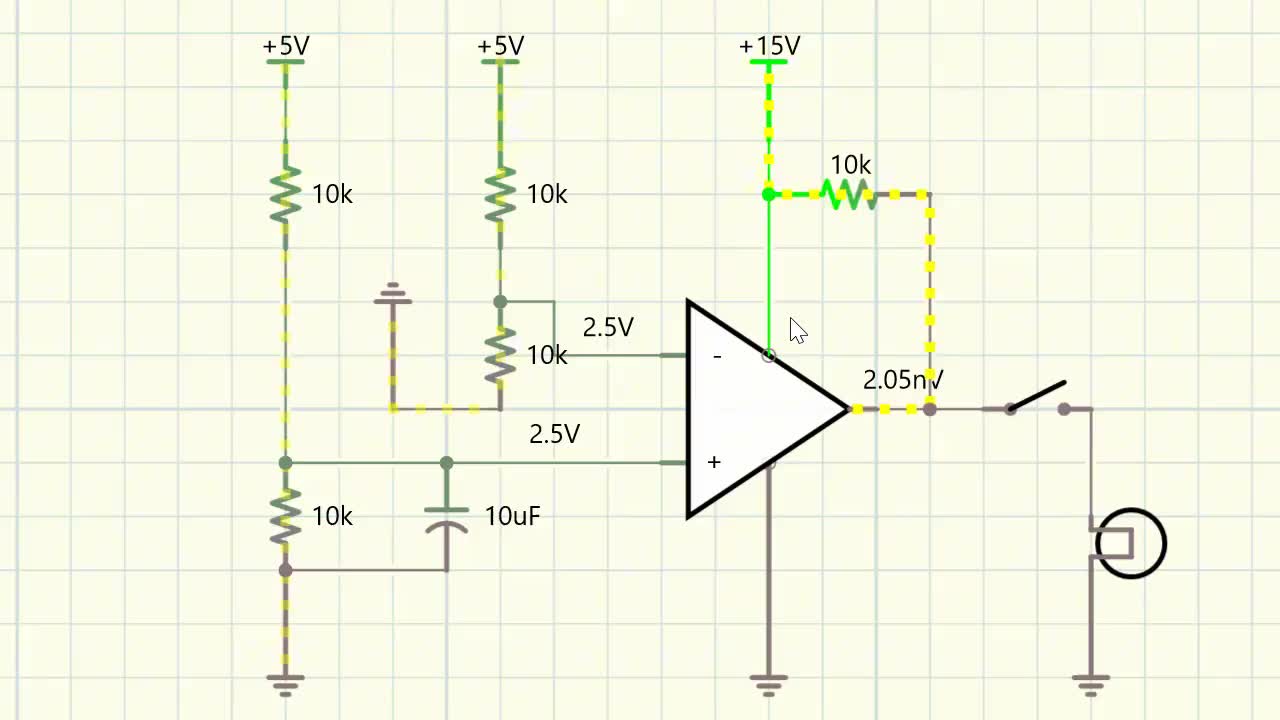

由SET 的周期振蕩特性和MOSFET 的閾值電壓特性可構成雙柵極SET/MOSFET 通用方波電路[8],它是構成邏輯門電路的基本單元,如圖2 所示。

圖中雙柵SET/MOSFET 的通用方波電路由SET、MOSFET 和恒流源構成。SET 的漏極電壓由Vgg 控制,Vgg-Vth 要足夠低以確保SET 漏源電壓近似恒定工作在庫侖振蕩條件下,Vcon控制漏電流周期振蕩的相位。接入恒流源Io 后,當Ids

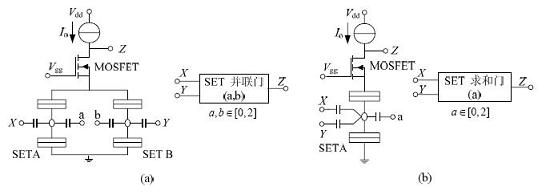

數字電路中,最基本的單元在于邏輯門設計。在上述電路基礎上,由雙柵SET/MOSFET基本電路單元可構造出所需的邏輯‘與或非’、‘異或’等基本門電路結構[9],如圖(3)所示。當a=0,b=1 時,SET并聯門實現邏輯函數Z =X?Y功能;當a=1,b=0 時,SET并聯門實現邏輯函數Z =X?Y功能。當a=0,SET求和門實現邏輯函數Z =X⊕Y功能;當a=1,SET求和門實現邏輯函數Z =X⊕Y功能。

圖3 SET/MOSFET 構成的邏輯門電路及相應符號

3 SET/MOSFET 數值比較器的實現

在計算機和數字系統中,特別是在計算機中都具有運算功能,一種簡單而又常用的運算是比較兩個數X 和Y 的大小,因此,在多情況下都用到數字比較器,需要判斷出X>Y,X

(X>Y)=XY (1)

利用a=1,b=0 時的SET 并聯門電路實現;

(X

利用a=0,b=1 時的SET 并聯門電路實現;

(X=Y)=XY+XY (3)

利用a= 1 時的SET 求和門電路實現。

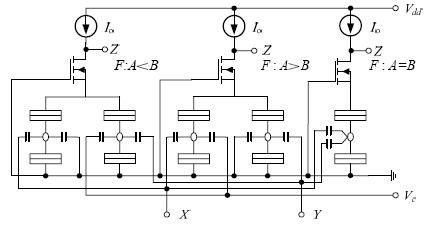

結合以上分析,利用SET/MOSFET 的混合結構設計出一位比較器的電路,如圖4 所示。

圖4 一位比較器電路圖

由圖4 可以看出,一位比較器由五個雙柵SET,三個耗盡型NMOSFET,三個恒流源構成。結構簡單,實現容易,更重要的是它的管子數大大減少,有利于進一步提高集成度,較好的適應了集成電路的發展要求,同時MOSFET 晶體管的高速、高驅動性為下一級電路的提供了可靠的工作環境。

4 仿真分析

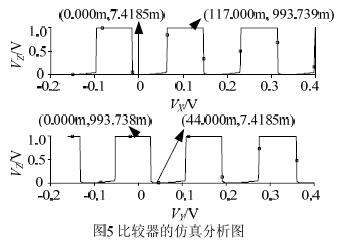

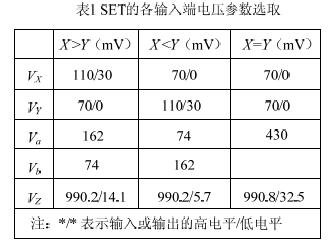

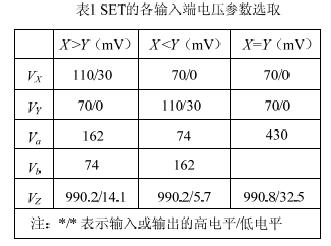

Mahapatra, Ionescu, Banerjee 等人2004 年提出SET 的MIB 數學模型[5]。該模型可以精確地描述SET 低溫低功耗下的I-V 特性。適當選取SET/MOSFET 的各物理參數使用該模型對該一位比較器進行仿真,得到圖5 的參數仿真分析結果,各參數選取如表1 所示。

圖5 中X 和Y 為輸入信號,Z 為輸出信號。當輸入X 為高電平信號,Y 為低電平信號,輸出Z 實現的是X>Y 功能,如圖5 所示。同理可得,當輸入X 為低電平信號,Y 為高電平信號,輸出Z 實現的是X

5 結論

本文作者創新點:基于數字電路的邏輯設計思想,利用SET/MOSFET 混合結構的傳輸特性,設計構造了一位數值比較器結構。通過仿真分析和驗證,該比較器的優點有:結構簡單;傳輸特性好;驅動負載工作能力強,通過適當選取混合SET/MOSFET 的各個物理參數,尤其是SET 的物理參數,可以達到低輸入電壓和高輸出電壓;同時利用混合雙柵極SET/MOSFET 實現‘同或’功能大大減少了管子的數目,更進一步提高了集成度,降低了功耗,更有利于大規模集成電路的實現。

參考文獻:

[1] Andrew R. Brown, Asen Asenov, and Jeremy R. Watling, “Intrinsic Fluctuations in Sub 10-nm Double-Gate MOSFETs Introduced by Discreteness of Charge and Matter”, IEEE Transactions on Nanotechnology, Vol. 1, No. 4, DEC 2002.pp:195~200.

[2] Likharev KK. “Single-electron devices and their applications”. Proceedings of the IEEE 1998;87(4), pp: 602~ 632.

[3] A. M. Ionescu et al., “Few electron devices: Toward hybrid CMOS-SET integrated circuits,” in Proc. DAC, 2002, pp: 323~326.

[4] 石喬林,李天陽,田海燕.深亞微米集成電路靜態功耗的優化[J].微計算機信息,2005,No.35, pp:138-141.

[5] S. Mahapatra, A. M. Ionescu, and K. Banerjee, “Analytical Modeling of Single Electron Transistor for Hybrid CMOS-SET Analog IC Design” IEEE Transactions on Electron Device, Vol.51, No. 11, Nov. 2004, pp: 1772~1782.

[6] 孫鐵署,蔡理,陳學軍. 一種單電子晶體管的SPICE宏模型[J],空軍工程大學學報(自然科學版),2003,4(6),65~67.

[7] Kim D H, Sung S-K, Kim K R et al. “Single-electron transistors based on gate-induced Si island for single-electron logic application” [J]. IEEE Transactions on Nanotechnology, 2002, 1(4):170~175.

[8] H. Inokawa, A. Fujiwara, and Y. Takahashi, “A Multiple-Valued Logic and Memory with Combined Single-Electron and Metal-Oxide-Semiconductor Transistors” IEEE Trans. Electron Devices, 2003, Vol. 50, No. 2, pp: 462~470.

[9] K. Degawa, T. Aoki, T. Higuchi, H. Inokawa, and Y.Takahashi, “A Single-Electron-Transistor Logic Gate Family and Its Application Part I: Basic Components for Binary, Multip le-Valued and Mixed-Mode Logic” Proc. 34th IEEE Int. Symp. on Multiple-Valued Logic, 2004.

電子發燒友App

電子發燒友App

評論