雙極發射極跟隨器:具有雙通道反饋的RISO

我們選擇用于分析具有雙通道反饋的RISO的雙極發射極跟隨器為OPA177,具體情況請參閱圖1。OPA177為一款低漂移、低輸入失調電壓運算放大器,其能在±3~±15V的電壓范圍內工作。

| 圖1:雙極發射極跟隨器運算放大器的技術規范。 |

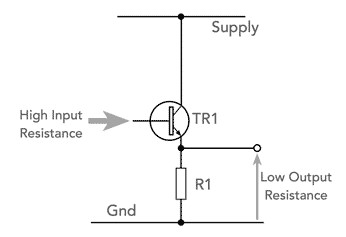

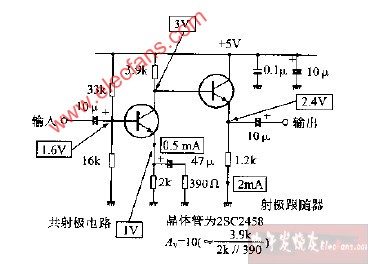

圖2顯示了一款典型的雙極發射極跟隨器的拓撲結構。請注意,用于Vo的正負輸出驅動均為雙極發射極跟隨器。目前,包含“等效電路圖”(表明運算放大器內部所用輸出級的拓撲結構)的產品說明書并不多見。為此,只能通過廠商的內部資料,我們才能確切了解輸出級的結構。

| 圖2:典型雙極發射極跟隨器運算放大器的拓撲結構。 |

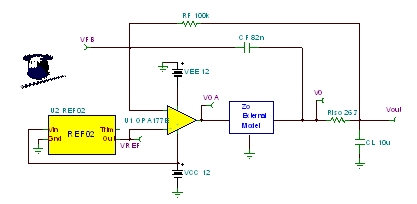

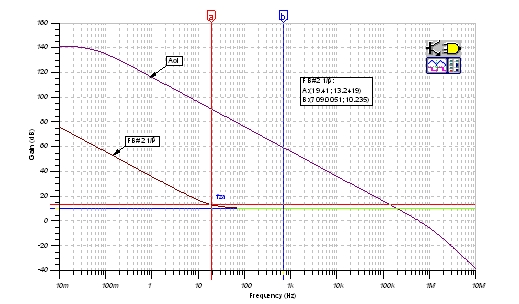

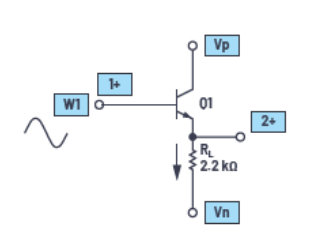

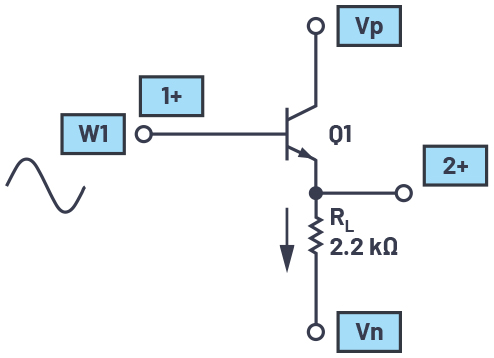

我們用于分析雙極發射極跟隨器的具有雙通道反饋的RISO電路如圖3所示。FB#1通過RF直接向負載(CL)提供反饋,從而促使Vout與VREF相等。FB#2通過CF提供了第二條反饋通道(在高頻率時占支配地位),從而確保了運行的穩定性。Riso將FB#1和FB#2相互之間隔離開來。需要注意的是,在目前用于穩定電容性負載的許多技術中,我們采用了經改進的Aol方法(當采用這種方法時,運算放大器的輸出阻抗和電容性負載改變了運算放大器的Aol曲線)。在改變后的Aol曲線中,我們在圖上標出1/,這將有助于電路的穩定運行。當采用具有雙通道反饋的RISO時,我們發現,更易于維持運算放大器Aol曲線不變并在圖上標出FB#1 1/β和FB#2 1/β曲線。于是,我們將運用疊加的方法,來獲得一條最終(net)的1/Bετα曲線,這樣,當在運算放大器的Aol曲線上進行標繪時,我們就能夠輕松地生成一款針對這種電容性負載穩定性問題的解決方案。

| 圖3:具有雙通道反饋的RISO:發射極跟隨器。 |

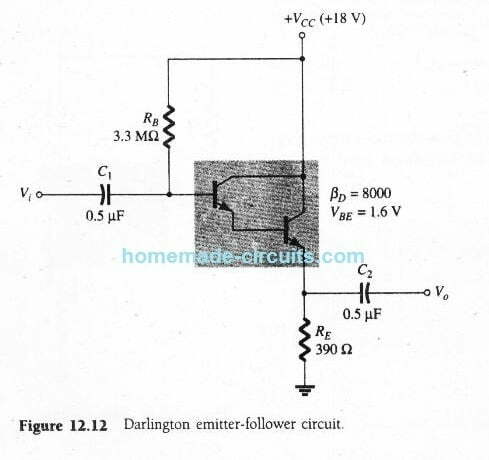

一旦我們選擇了運算放大器,如圖4所示的Aol測試電路就為開展穩定性分析提供了前提基礎。Aol曲線可從產品說明書中獲取,或者從如圖所示的Tina SPICE仿真中測量得出。Aol測試電路采用雙電源供電,即使Vout近乎為零伏,我們仍可測量空載時的Aol曲線,而且輸入共模電壓的要求易于滿足。R2和R1以及LT為低通濾波器函數提供了一條AC通道,從而允許我們在反饋通道中進行DC短路和AC開路操作。務必提請注意的是,在進行AC分析前,SPICE必須開展DC閉環分析,以找到電路的工作點。另外,R2和R1以及CT為高通濾波器函數提供了一條AC通道,這樣,使得我們能將DC開路和AC短路一起并入輸入端。LT和CT按大數值等級選用,以確保其在各種相關的AC頻率時,電路短路和開路情況下的正常運行。

| 圖4:Aol測試示意圖:發射極跟隨器。 |

| 圖5:Aol測試結果:發射極跟隨器。 |

從TinaSPICE仿真測量得出的OPA177 Aol曲線如圖5所示。測量得出的單位增益帶寬為607.2kHz。

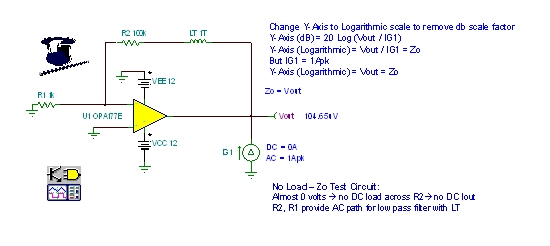

現在,我們必須測量如圖6所示的Zo(小信號AC開環輸出阻抗)。該Tina SPICE測試電路將測試空載OPA177的Zo。R2和R1以及LT為低通濾波器函數提供了一條AC通道,這樣,使得我們能將DC短路和AC開路一起并入反饋電路。DC工作點在輸出端顯示為接近零伏,這也就是說,OPA177沒有電流流入或流出。此時,通過運用1Apk AC電流生成器(我們能夠掃視10mHz至1MHz的AC頻率范圍),Zo的測量工作就可以輕松完成。最后,得出測量結果Zo=Vout(如果將測量結果的單位從dB轉換為線性或對數,那么Vout也將為以歐姆為單位的Zo)。

| 圖6:空載Zo測試電路:發射極跟隨器。 |

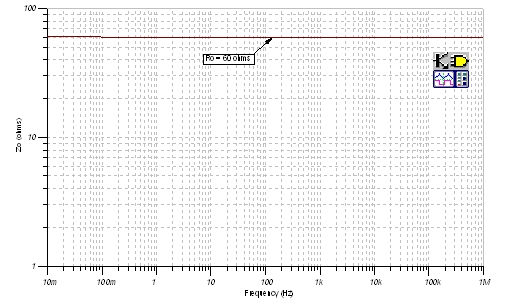

從圖7中,我們可以看出,OPA177 Zo是雙極發射極跟隨器輸出級所獨有的特征,而且這種輸出級的Ro在OPA177單位增益帶寬之內,是控制輸出阻抗的專門組件。OPA177的Ro為60歐姆。

|

| 圖7:開環輸出阻抗:發射極跟隨器。 |

|

| 圖8:Zo外部模型:發射極跟隨器。 |

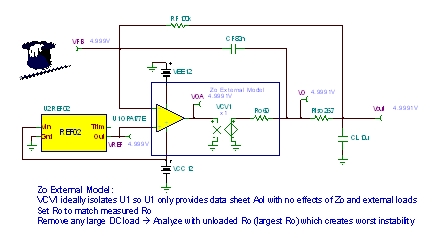

為了使1/β分析的情況包括在Zo與Riso、CL、CF以及RF之間相互作用的影響結果內,我們需將Zo從運算放大器的宏模型中分離出來,以便于弄清楚電路中所需的節點。這種構思如圖8所示。U1將提供了產品說明書中的Aol曲線,并從Riso、CL、CF以及RF的各種影響中得到緩沖。

|

| 圖9:具有雙通道反饋的RISO:發射極跟隨器Zo外部模型詳圖:發射極跟隨器。 |

通過如圖9所示的Zo外部模型,我們能夠測量Zo與Riso、CL、RF以及CF之間相互作用對1/β的影響。在Zo外部模型中,設置Ro=Ro OPA177,實際測量值為60歐姆。壓控電壓源VCV1將運算放大器宏模型U1從Ro、Riso、CL、CF以及RF中隔離開來。將VCV1設置為x1,以確保產品說明書中的Aol增益不變。由于我們要在穩定性狀況最糟的情況下(只存在CL以及我們計算得出的空載Zo[此時Ro=60歐姆])分析這種電路,因此,務必排除各種大的DC負載。VOA是一個與運算放大器相連的內部節點,在實際工作中,我們無法實現對這種節點的測量。同時,許多SPICE宏模型上的這種內部節點接入,也并非易事。對1/β進行分析(相對于VOA),已涵蓋了Ro、Riso、CL、CF以及RF的影響。如果未采用Zo外部模型,SPICE中的最終穩定性仿真就無法標繪出1/β的曲線;但是,如果采用Zo外部模型,則可標繪出環路增益的曲線以確認我們分析的正確性。

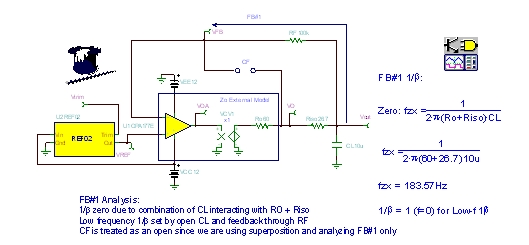

首先,我們要分析如圖10所示的FB#1。請注意,由于我們只分析FB#1,所以CF可視為處于開路狀態。接下來,我們將分析FB#2。然后,通過采用疊加的方法,將兩條反饋通道合并在一起,求取最終的1/β。分析結果如圖上所示,有關的公式推導和具體細節,請參閱下一張圖(圖11)。我們發現,當fzx=183.57Hz時,FB#1 1/β曲線的增益為零。低頻1/β值為1。如欲獲得該增益,那么低頻1/β值應大于1。

|

| 圖10:FB#1分析:發射極跟隨器。 |

| 圖11:FB#1 1/β公式的推導:發射極跟隨器。 |

FB#1β的公式推導如圖11左側所示。由于1/β是β的倒數,所以FB#2 1 1/β的計算結果可以輕而易舉的被推導出來,具體推導過程,請參閱圖11右側。從圖中我們還發現,在β推導過程中的pole,fpx變成了1/β推導過程中的zero,fzx。 我們將采用如圖12所示的電路來開展AC分析:通過Tina SPICE,求取FB#1的1/β,OPA177的Aol以及只采用FB#1電路的環路增益。正因為如此,所以我們將CF從圖中除去。

FB#1 1/β的結果標示在圖13中的OPA177 Aol曲線上。在環路增益為零的fcl處,我們發現,接近速率為40dB/decade:[(Aol曲線上的-20dB/decade)-(FB#1 1/β曲線上的+20dB/decade)=-40dB/decade接近速率)]。

|

| 圖12:FB#1AC電路分析:發射極跟隨器。 |

接近速率的經驗數據表明了存在的不穩定性。我們對FB#1的分析是基于zero、fzx=183.57Hz,低頻1/β=1的情況。從圖13中可以看出,我們的一階分析準確地推算出了FB#1 1/β的數值。

|

| 圖13:FB#1 1/β曲線圖:發射極跟隨器。 |

從圖14中我們發現,只配置FB#1的電路環路增益分析顯示,在環路增益為零的fcl處,相位裕度接近零。這樣,就明確證實了電路的不穩定性。通過檢測圖13中Aol曲線上的FB#1 1/β曲線,可推算出環路增益曲線上的極點和零點。

| 圖14:FB#1環路增益分析:發射極跟隨器。 |

| 圖15:FB#1瞬態穩定性測試電路:發射極跟隨器。 |

如果我們有任何疑問,或如果只采用FB#1構建參考緩沖電路,此時,我們可運用如圖15中的電路,進行實際的瞬態穩定性測試。

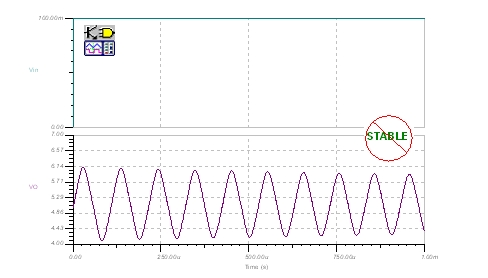

圖16中的瞬態穩定性測試結果同時與Aol曲線上的1/β值和環路增益曲線一致,因此,證明了只采用FB#1構建參考緩沖電路,將導致電路運行的不穩定性。

|

| 圖16:FB#1瞬態穩定性測試:發射極跟隨器。 |

現在,我們必須弄清楚如何生成一款解決方案,以保證電容性負載參考緩沖電路的穩定性。此時,我們進一步了解了如圖17所示的Aol曲線和FB#1 1/β曲線。如果我們添加如圖17所示的FB#2 1/β曲線,我們則會看到一條最終的1/β曲線,這樣,根據fcl處的接近速率以往的穩定性經驗,我們可以推斷電路的運行也將是穩定的。

另外,我們將促使fpc低于1/β曲線中的fzx一個decade,以確保當頻率低于fcl時,相位裕度優于45度。上述工作通過調整1/βFB#2的高頻部分,使其比FB#1低頻1/β高出+10dB。然后,設置fza,使其至少低于fpc一個decade,以確保當實際應用中進行參數變化時,能夠避免BIG NOT。通過觀察,我們發現,最終的1/β曲線是在FB#1 1/β曲線和FB#2 1/β曲線中選擇最小數值的1/β通道而形成的。

務必請記住,在雙反饋通道中,從運算放大器輸出端至負極輸入端的最大電壓反饋將主導著整個反饋電路。最大的反饋電壓意味著β值最大或者是1/β值最小。圖18向我們展示了這種關鍵的推算技巧。

最后,在FB#2取得支配地位之前,預計Vout/Vin的傳輸函數將隨著FB#1的變化而變化。此時,Vout/Vin將會衰減至-20dB/decade,直至FB#2與Aol曲線相交,然后,將隨著Aol曲線下降。

|

| 圖17:FB#2圖解分析:發射極跟隨器。 |

|

| 圖18:雙通道反饋、疊加以及1/β:發射極跟隨器。 |

圖18告訴我們,當整個運算放大器電路采用雙通道反饋電路時,最大的β值電路將居支配地位。一個很明顯的例子就是,如果有兩個人對著您的同一只耳朵講話,您會更易于聽到哪個人的講話?當然是嗓門最大的那個人!同樣的道理,運算放大器也將會“聽到”β值最大或1/β值最小的反饋電路。運算放大器察覺到最終的1/β曲線將是在各種FB#1 1/β或FB#2 1/β頻率時,頻率較低的那一條曲線。??

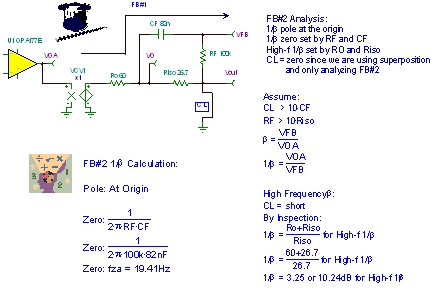

如圖19所示,里面會有一些主要的假設。我們將這些假設運用于幾乎所有的具有雙通道反饋的RISO電路中。首先,我們假設CL>10*CF,這也就是說,在高頻率時,CL早在CF短路前短路。因此,我們將短路CL以排除FB#1,從而便于單獨分析FB#2。另外,我們假設RF>10*Riso,這意味著作為Riso的負載,該RF幾乎完全失效。從圖19和圖20中具體的公式推導,我們可以看出,當zero,fza=19.41Hz(由RF和CF產生)時,FB#2在原點擁有一個極點。由于在高頻時,CF和CL同時處于短路狀態,所以FB#2高頻1/β部分即為Ro+Riso與Riso之間的比值。FB#2 1/β的公式推導請參閱下一張圖(圖20),有關計算結果請參閱下圖。FB#2高頻1/β設置為3.25dB或10.24dB、原點擁有一個極點以及當頻率為19.41Hz時的零點。

|

| 圖19:FB#2分析:發射極跟隨器。 |

| 圖20:FB#2 1/β公式推導:發射極跟隨器。 |

FB#2β的公式推導如圖20左側所示。由于1/β是β的倒數,所以FB#1 1/β的計算結果可以輕而易舉的被推導出來,具體推導過程請參閱圖20右側。從圖中我們還發現,在β推導過程中的pole,fpa變成了1/β推導過程中的zero,fza。

|

| 圖21:FB#2AC電路分析:發射極跟隨器。 |

|

| 圖22:FB#2 1/β曲線:發射極跟隨器。 |

為了檢驗FB#2的一階分析情況,我們可采用如圖21所示的Tina SPICE電路。再者,為了便于分析,我們將CL設置為10GF,因此對各種相關的頻率而言,CL都等同于短路狀態。但是,在開展AC分析前,仍允許SPICE查找到相應的DC工作點。

Tina SPICE仿真的結果如圖22所示。FB#2 1/β曲線正如當fza=19.41Hz以及高頻1/β=10.235dB時,采用一階分析推算出來的結果一樣。另外,我們也繪制出OPA177 Aol曲線,以弄清楚在高頻率時,FB#2將如何與其相交。

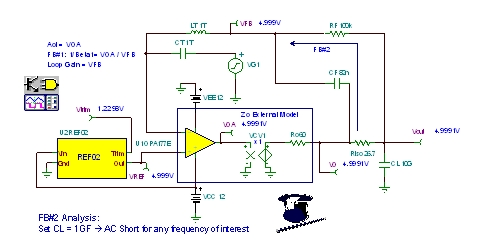

如果推算的FB#1和FB#2的疊加結果會產生所需的最終1/β曲線,那么我們將通過如圖23所示的Tina SPICE電路,開展分析工作。我們還可通過Tina SPICE電路,繪制出Aol曲線、最終的1/β曲線以及環路增益曲線。

| 圖23:最終環路增益分析電路:發射極跟隨器。 |

從圖24中,我們可以看出,分析結果驗證了我們所推算的最終1/β曲線。在環路增益為零的fcl處,推算的接近速率為20dB/decade。

|

| 圖24:最終1/β曲線:發射極跟隨器。 |

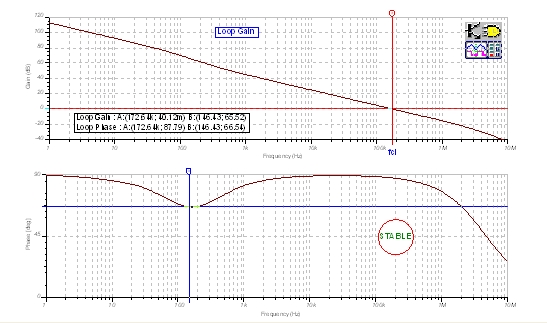

最終電路的環路增益相位曲線(采用FB#1和FB#2)如圖25所示。相移從未下降至58.77度以下(如為當頻率為199.57kHz時的情況),而且,在fcl處(頻率為199.57kHz),相位裕度為76.59度。

|

| 圖25:最終環路增益分析:發射極跟隨器。 |

我們將采用圖26中的Tina SPICE電路,對我們的穩定電路進行最后的檢驗-瞬態穩定性測試。

|

| 圖26:最終瞬態穩定性測試電路:發射極跟隨器。 |

圖27中最終電路瞬態穩定性的測試結果符合我們其他所有的推算結果,從而研制出一款性能優良、運行穩定的電路。而且,我們可以信心十足的將這種電路投入量產,因為它不會發生故障或在實際運行中出現異常。

|

| 圖27:最終瞬態穩定性測試:發射極跟隨器。 |

|

通過圖28中的Tina SPICE電路,可驗證我們對Vout/Vin的推算是否正確。

從圖29中,我們可以看出,Vout/Vin的測試結果與我們推算的一階分析結果一致,具體表現為:當頻率為625.53Hz時,單極點開始下降。而且,當頻率約為200kHz(此時,FB#2與OPA177 Aol曲線相交)時,出現第二個極點。

|

| 圖29:最終Vout/Vin傳輸函數:發射極跟隨器。 |

圖30總結了一種易于使用的漸進式程序。這種程序輕松地將具有雙通道反饋的RISO電容性負載穩定性技術應用于雙極發射極跟隨器輸出運算放大器上。

1. 測量運算放大器的Aol。

2. 測量運算放大器的Zo,并在圖上繪制出其曲線。

3. 確定RO。

4. 創建Zo的外部模型。

5. 計算FB#1低頻1/b:對單位增益電壓緩沖器而言,該值為1。

6. 將FB#2高頻1/b設置為比FB#1低頻1/b高+10dB(為獲得最佳的Vout/Vin瞬態響應并實現環路增益帶寬相移量最少)。

7. 從FB#2高頻1/b中選擇Riso以及RO。

8. 從CL、Riso、RO中,計算FB#1 1/bfzx。

9. 設置FB#2 1/b fza=1/10fzx。

10. 選擇具有實際值的RF和CF,以產生fza。

11. 采用Aol、1/b、環路增益、Vout/Vin以及瞬態分析的最終值,運行仿真以驗證設計的可行性。

12. 核實環路增益相移的下降不得超過135度(>45度相位裕度)。

13. 針對低噪聲應用而言:檢查Vout/Vin扁平響應,以避免增益驟增→Vout/Vin中的噪聲陡升。

| 圖30:具有雙通道反饋的RISO補償程序:發射極跟隨器。 |

|

| 圖31:雙通道反饋和BIG NOT。 |

當運算放大器采用雙通道反饋回路時,有一種異常重要的情況需要避免,那就是“BIG NOT”。如圖31所示,存在能夠產生反饋回路的運算放大器電路(反饋回路導致了BIG NOT),這可從包括有效1/β斜坡(從+20db/decade驟變為-20dB/decade)的最終1/β曲線中看出。這種快速變化意味著在1/β曲線中存在復共扼極點,因此,也意味著在環路增益曲線中存在復共扼零點。當處于復合零點/復合極點的頻率時,復合零點和極點產生了±90度的相移。同時,在復合零點/復合極點附近的相位斜坡在頻率發生位置的窄頻帶,可在±90度至±180度之間變化。出現復合零點/復合極點將在閉環運算放大器響應中導致增益的驟增。這種現象會造成負面的影響,尤其是對于功率運算放大器電路而言,更是如此。

|

| 圖32:以圖表的形式創建BIG NOT。 |

讓我們回到圖17OPA177 Aol曲線上的FB#1和FB#2標繪點,只要改變如圖32所示的fza的位置,就可輕而易舉的創建BIG NOT。在fcl處,按照以往接近速率的情況,顯示這種電路的運行是穩定的——但是,果真如此么?

在圖33中,我們改變了同時用于分析FB#1和FB#2的Tina SPICE電路,以創建如圖32所示的BIG NOT。將CF由82nF調整為220pF,以便于將fza移到所需的BIG NOT創建位置。

|

| 圖33:環路增益分析電路:BIG NOT。 |

| 圖34:1/β曲線:BIG NOT。 |

BIG NOT的1/β曲線與OPA177 Aol曲線一起在圖34中標繪出來。在fcl處,出現了20dB/decade的接近速率。但是,請注意在BIG NOT1/β曲線中,斜率有一個急劇的變化--從+20dB/decade變為-20dB/decade。然而,這種1/β曲線的急劇變化并非是一件好事,為此,我們應質疑這種電路的穩定性。

圖35中BIG NOT電路的環路增益曲線表明相移幾乎達到了180度(當頻率為1.034kHz時,大于167度),這意味著當頻率為1.034kHz時,我們僅與180度的相移相距約13度。同時,請注意觀察在這同一區域,環路增益是如何向下朝著零點環路增益急劇形成尖峰的。同樣,在fcl處,有著充足的相位裕度。但是,我們還是會問,這種電路運行穩定么?

|

| 圖35:環路增益分析:BIG NOT。 |

于是,假設我們在穩定性分析技巧方面毫無經驗(事實上并非如此),接著構建這款BIG NOT電路。我們期望了解實際應用中的瞬態穩定性會是如何開展的。通過圖36中的Tina SPICE電路,我們可以看到,如果我們將該BIG NOT電路投入量產,再將其投入實際的應用中,會產生什么結果呢?

千萬不要告訴您的上司,我們將該電路投入了量產,否則情況會更糟糕。客戶收到您發送的、內置這種電路的設備后,發現有時向電路供電或當其他負載突然饋入該參考緩沖電路時,會出現奇怪和間歇性的問題。這是更新我們的歷史參數的適當時候嗎?盡管該電路不是振蕩器,但是,如圖37所示來自瞬態穩定性測試中過度的振鈴和很長的建立時間意味著電路處于穩定的邊緣上。根據BIG NOT出現的位置,振動器振鈴的持續時間和振幅更容易變得比本例所述的情況還糟。從電路板和系統層面來考慮,我們將這種電路定義為“不穩定”,尤其是當我們的分析工作未涵蓋實際應用中的寄生效應時,情況更是如此(這些寄生效應出現在PCB布局、組件容差、運算放大器參數容差以及組件和運算放大器參數的溫度變化等方面)。令人感到欣慰的是,我們只將該電路投入“虛擬”的量產,而相應的將我們的具有雙通道反饋的RISO應用到即將投入實際使用的電路。

|

| 圖36:瞬態穩定性測試電路:BIG NOT。 |

| 圖37:瞬態穩定性測試:BIG NOT。 |

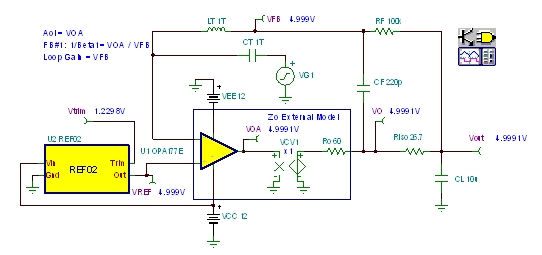

CMOS RRO:具有雙通道反饋的RISO

我們選擇用于分析具有雙通道反饋的RISO的CMOS RRO為OPA734,具體情況請參閱圖38。OPA734是一款低漂移、低輸入失調電壓的運算放大器,其能在+2.7V~+12V的電壓范圍內工作。這種極低的漂移(0.05uV/C)加上其超低的初始輸入失調電壓(1uV),使OPA734成為了單電源應用中理想的參考緩沖放大器。由于這并非是軌至軌CMOS輸入放大器,因此,我們有必要觀察輸入電壓范圍的技術規范[(V-)-0.1V至(V+)-1.5V]。

|

| 圖38:CMOS RRO運算放大器的技術規范。 |

典型的CMOS RRO等效電路圖如圖39所示。從圖中可以看出,運算放大器的輸出端連接至MOSFET的漏極。這種漏極輸出運算放大器具備一個Zo(同時具有阻性和容性的特點),要求我們運用某些相對于雙極發射極跟隨器略有不同的分析技術,如具有雙通道反饋的RISO電路示例。

| 圖39:典型的CMOS RRO運算放大器拓撲結構。 |

從圖40中我們可以看出,CMOS RRO參考緩沖電路的外觀與雙極發射極跟隨器示例中所采用的電路外觀一模一樣。在本應用示例中,我們采用電壓為5V的單電源,對2.5V的參考電路(該電路的電壓值低于輸入電壓范圍的技術規范[輸入電壓范圍:5V-1.5V=3.5V])進行緩沖。由于為了獲得良好的穩定性,在高頻時FB#1和FB#2將提供所需要的反饋,因此,在Vout處,可獲取準確的參考電壓。Riso將使兩條反饋電路單獨運行,互不干擾。

|

| 圖40:具有雙通道反饋的RISO:CMOS RRO。 |

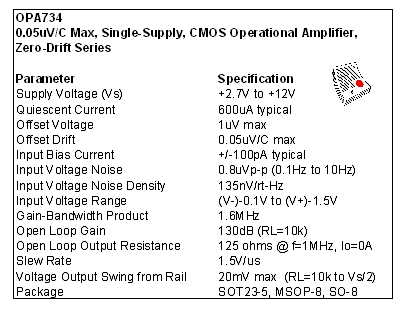

由于在本應用示例中,我們采用的是單電源,因此,我們將運用一些新技巧來獲取如圖41所示的空載Aol曲線。首先,我們需要確保在開展DC工作點分析之后的OPA734輸出信號處于工作的線性區域。通常來說,由于運算放大器的飽和輸出信號并非處在工作的線性區域,因此,其未能提供恰當的AC性能。對于大多數運算放大器宏模型來說也是如此。在DC狀態時,LT為短路而CT為開路。OPA734的非反相輸入限制為Vs/2(2.5V)。因此,輸出將為Vs/2(2.5V)。如圖所示的RL接線方式,在運算放大器的輸出端不存在DC負載。RL以及LT為低通濾波器函數提供了一條AC通道。這樣,在反饋電路中,就可使DC處于短路狀態而AC處于開路狀態。務必提請注意的是,在進行AC分析前,SPICE必須開展DC閉環分析,以找到電路的工作點。另外,RL以及CT為高通濾波器函數提供了一條AC通道,這樣,使得我們能將DC開路電路和AC短路電路一起并入輸入端。而且,LT和CT按大數值等級選用,以確保其在各種相關的AC頻率時,電路短路和開路情況下的正常運行。

| 圖41:Aol測試示意圖:CMOS RRO。 |

從Tina SPICE仿真測量得出的OPA734 Aol曲線如圖42所示。測得的單位增益帶寬為1.77MHz。

|

| 圖42:Aol測試結果:CMOS RRO。 |

| 圖43:由Zo、CCO、RCO、CL改變Aol效應的TINA電路。 |

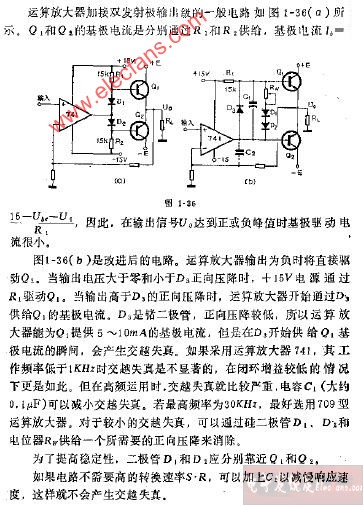

現在,我們必須測量如圖43所示的Zo(小信號AC開環輸出阻抗)。該Tina SPICE測試電路將測試空載OPA734的Zo。請注意,由于我們測試的是單電源電路,因此將輸出信號調整至Vs/2(2.5V),以確保運算放大器輸出電流的正弦波位于工作的線性區域。RL以及LT為低通濾波器函數提供了一條AC通道。這樣,在反饋電路中,就可使DC處于短路狀態而AC處于開路狀態。由于RL限定在Vout(2.5V)和Vs/2(2.5V)之間,所以DC工作點在輸出端顯示為2.5V或Vs/2伏,這也就是說,OPA734沒有電流流入或流出。此時,通過運用1Apk AC電流發生器(我們能夠掃視10mHz至1MHz的AC頻率范圍),Zo的測量工作能夠輕松完成。最后,得出測量結果Zo=Vout(如果將測量結果的單位從dB轉換為線性或對數,Vout也就是以歐姆為單位的Zo)。

| 圖44:Zo、開環輸出阻抗:CMOS RRO。 |

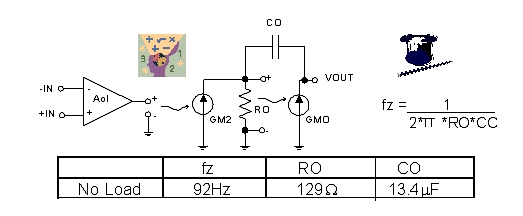

從圖44中,我們可以看出,OPA734 Zo是CMOS RRO運算放大器輸出級所獨有的特征。而且,這種輸出級的Ro在高頻時,處于支配地位。同時,Co所呈現出的電容效應在頻率低于92Hz時,處于支配地位。

根據前面圖表的仿真測試結果,我們在圖45中構建了OPA734的Zo模型。RO直接測得為129歐姆,fz直接測得為92Hz。根據測得的fz和RO數值,我們可以輕松地計算出CO的數值(為13.4uF)。最終完成了如圖所示的Zo模型。

|

| 圖45:Zo模型:CMOS RRO。 |

| 圖46:Zo外部模型:CMOS RRO。 |

為了使1/β分析的情況包含在Zo與Riso、CL、CF以及RF之間相互作用的影響結果內,我們需將Zo從運算放大器的宏模型中分離出來,以便于弄清楚電路中所需的節點。這種構思如圖46所示。另外,U1將提供產品說明書的Aol曲線,并從Riso、CL、CF以及RF的各種影響中得到緩沖。

通過如圖47所示的Zo外部模型,我們能夠測量Zo與Riso、CL、RF以及CF之間的相互作用對1/β的影響。RO和CO是我們在前一張圖表中測出的參數。GM2將U1(OPA734運算放大器宏模型)從Zo外部模型中隔離開來。將GM2設置為1/RO以保持適當的Aol增益,目的是與最初的OPA734運算放大器宏模型和產品說明書中的Aol相匹配。在SPICE進行AC分析前,其必須開展DC分析。因此,我們需確保擴展后的運算放大器模型,將具備正確的DC工作點而無需使U1達到飽和狀態。為此,我們在CO至VO之間添加了一條低頻通道。GMO將由RO兩端的電壓控制(該電壓與VOA相匹配)。將GMO設置為1/RL以維持DC狀態時的綜合增益水平,目的是與最初的OPA734 Aol相匹配。另外,一只低通濾波器由RLP和CLP形成,并設置為0.1*fLOW(fLOW是相關的最低頻率)。將RLP設置為1000*RO,以避免RO上出現負載或相互作用(影響),最終導致Zo傳輸函數發生錯誤。

| 圖47:Zo外部模型詳圖:CMOS RRO。 |

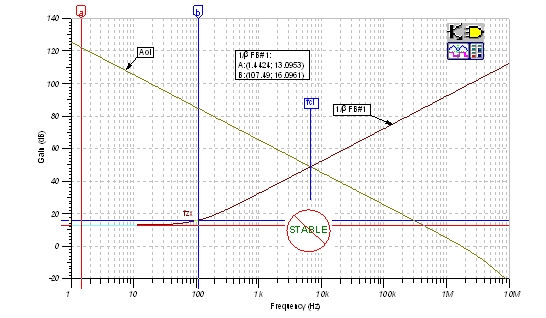

首先,我們分析如圖48所示的FB#1。請注意,由于我們只分析FB#1,所以CF可視為處于開路狀態。接下來,我們將分析FB#2。然后,通過采用疊加的方法,將兩條反饋通道合并在一起,求取最終的1/β。分析結果如圖48所示,有關的公式推導和具體細節,請參閱圖49。我們發現,當fzx=107.49Hz時,FB#1 1/β曲線上出現零點。低頻1/β值為4.5或13dB,并由介于CO和CL之間的電容分壓器確定。如果改變電路以獲得增益,那么低頻1/β值將大于β。

|

| 圖48:FB#1分析:CMOS RRO。 |

|

| 圖49:FB#1 1/β公式推導:CMOS RRO。 |

FB#1β的公式推導如圖49左側所示。由于1/β是β的倒數,所以FB#1 1/β的計算結果可以輕而易舉的推導出來,具體推導過程,請參閱圖49右側。從圖中我們還發現,在β推導過程中的pole,fpx變成了1/β推導過程中的zero,fzx。

我們將采用如圖50所示的電路來開展AC分析:通過Tina SPICE,找到FB#1的1/β,OPA177的Aol以及只采用FB#1電路的環路增益。

|

| 圖50:FB#1 AC電路分析:CMOS RRO。 |

FB#1 1/β的結果標示在圖51中的OPA734 Aol曲線上。在環路增益為零的fcl處,我們發現,接近速率為40dB/decade:

[(Aol曲線上的-20dB/decade)-(FB#1 1/β曲線上的+20dB/decade)=-40dB/decade接近速率)]

為此,接近速率的歷史數據表明了存在不穩定性。而且,我們對FB#1的分析是基于zero、fzx=183.57Hz,低頻1/β=13.09dB的情況。從圖51中可以看出,我們的一階分析準確推算出了FB#1 1/β的數值。

|

| 圖51:FB#1 1/β曲線:CMOS RRO。 |

|

| 圖52:具有雙通道反饋的RISO:發射極跟隨器FB#1環路增益分析:CMOS RRO。 |

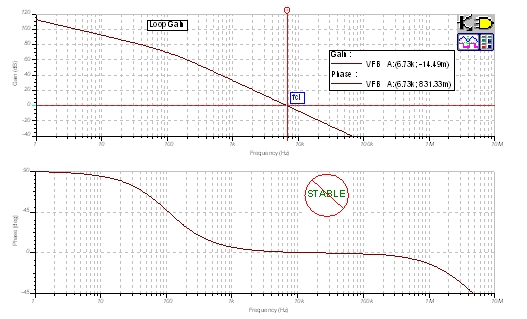

從圖52中我們發現,只配置FB#1的電路環路增益分析顯示,在環路增益為零的fcl處,相位裕度接近零。這樣,就明確證實了電路的不穩定性。通過觀察圖51中Aol曲線上的FB#1 1/β標繪點,可推算出環路增益曲線上的極點和零點。

如果我們有任何疑問,或如果只采用FB#1構建參考緩沖電路,此時,我們可運用圖53中的電路,進行實際的瞬態穩定性測試。

圖54中的瞬態穩定性測試結果同時與Aol曲線上的1/β值和環路增益曲線一致,因此,證明了只采用FB#1構建參考緩沖電路,將導致電路運行的不穩定性。

|

| 圖53:FB#1瞬態穩定性測試電路:CMOS RRO。 |

| 圖54:FB#1瞬態穩定性測試:CMOS RRO。 |

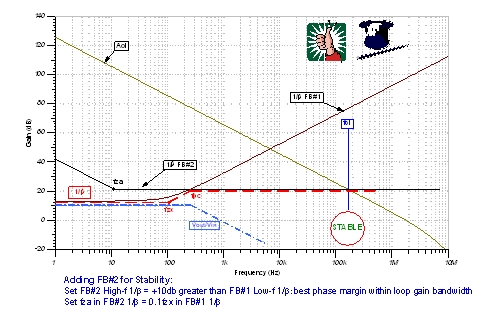

現在,我們必須弄清楚如何合成一種解決方案,以保證設置電容性負載參考緩沖電路的穩定性。此時,我們進一步了解如圖55所示的Aol曲線和FB#1 1/β曲線。如果我們添加圖55所示的FB#2 1/β曲線,我們就會看到一條最終的1/β曲線,這樣,根據fcl處的接近速率在歷史上的穩定性經驗,可以推斷電路的運行也將是穩定的。

另外,我們將促使fpc低于1/β曲線中的fzx一個decade,以確保當頻率低于fcl時,相位裕度優于45度。上述工作通過調整1/βFB#2的高頻部分,使其比FB#1低頻1/β高出+10dB。接著,設置fza,使其至少低于fpc一個decade,以確保當實際應用中進行參數變化時,能夠避免BIG NOT。通過觀察,我們發現,最終的1/β曲線是在FB#1 1/曲線和FB#2 1/β曲線中選擇最小數值的1/β通道而形成的。

務必請記住,在雙反饋通道中,從運算放大器輸出端至負極輸入端的最大電壓反饋將主導著整個反饋電路。最大的反饋電壓意味著β值最大或者是1/β值最小。

最后,在FB#2取得支配地位之前,預計Vout/Vin的傳輸函數將隨著FB#1的變化而變化。此時,Vout/Vin將會衰減至-20dB/decade,直至FB#2與Aol曲線相交,然后,將隨著Aol曲線下降。

|

| 圖55:FB#2圖解分析:CMOS RRO。 |

如圖56所示,里面有一些主要的假設。我們將這些假設運用于幾乎所有的具有雙通道反饋的RISO電路中。首先,我們假設CL>10*CF,這也就是說,在高頻率時,CL早在CF短路之前就短路。因此,我們將短路CL以排除FB#1,從而便于單獨分析FB#2。另外,我們假設RF>10*Riso,這意味著作為Riso的負載,該RF幾乎完全失效。從圖56和圖57中具體的公式推導,我們可以看出,當zero,fza=19.41Hz(由RF和CF產生)時,FB#2在原點擁有一個極點。由于在高頻時,CF和CL同時處于短路狀態,所以FB#2高頻1/β部分即為Ro+Riso與Riso之間的比值。FB#2 1/β的公式推導請參閱下一張圖(圖57),有關計算結果請參閱下圖。FB#2高頻1/β設置為10.92dB或20.76dB、原點擁有一個極點以及當頻率為10.6Hz時的零點。

|

| 圖56:FB#2分析:CMOS RRO。 |

FB#2β的公式推導如圖57左側所示。由于1/β是β的倒數,所以FB#1 1/β的計算結果可以輕而易舉的推導出來,具體推導過程請參閱圖57右側。從圖中我們還發現,在β推導過程中的pole,fpa變成了1/β推導過程中的zero,fza。

|

| 圖57:FB#2分析:CMOS RRO。 |

為了檢驗FB#2一階分析情況,我們可采用如圖58所示的Tina SPICE電路。而且,為了便于分析,我們將CL設置為10GF,因此對各種相關的頻率而言,CL都等同于短路狀態。但是,在開展AC分析前,仍允許SPICE查找到相應的DC工作點。

| 圖3:FB#2 AC電路分析:CMOS RRO。 |

Tina SPICE仿真結果如圖59所示。FB#2 1/β曲線正如當fza=10.6Hz以及高頻1/β=23.78dB時,采用一階分析推算出來的結果一樣。另外,我們也繪制出OPA734 Aol曲線,以弄清楚在高頻時,FB#2將如何與其相交。

| 圖59:FB#2 1/β曲線:CMOS RRO。 |

如果推算的FB#1和FB#2疊加結果會產生所需的最終1/β曲線,那么我們將通過如圖60所示的Tina SPICE電路開展分析工作。同時,我們還可通過Tina SPICE電路,繪制出Aol曲線、最終的1/β曲線以及環路增益曲線。

|

| 圖60:最終環路增益分析電路:CMOS RRO。 |

從圖61中,我們可以看出,分析結果驗證了我們所推算的最終1/β曲線。在環路增益為零的fcl處,推算的接近速率為20dB/decade。

| 圖61:最終的1/β曲線:CMOS RRO。 |

最終電路的環路增益相位曲線(采用FB#1和FB#2)如圖62所示。相移從未下降至66.54度以下(出現在頻率為146.43kHz的地方),因為,在fcl處(頻率為172.6?kHz),相位裕度為87.79度。

|

| 圖62:最終環路增益分析:CMOS RRO。 |

我們將采用圖63中的Tina SPICE電路對我們的穩定電路進行最后的檢驗-瞬態穩定性測試。

電子發燒友App

電子發燒友App

評論