Hoover 通常,它需要一個可具有高達 1nsRMS 抖動的函數發生器。常常需要采用一個高質量的 RF 發生器或晶體振蕩器以從 16 或 18 位 ADC 獲得最佳的 SNR 值,即使在相對較低的輸入頻率

2018-08-28 09:31:02 5393

5393 RCC電路原理與設計及問題解析

RCC電路,單端反激式的一種,結構簡單,主要應用在1~200W,首先變壓器設計最為重要,RCC電路結構主要包括: 1.

2009-12-14 10:31:05 24103

24103 模數轉換器的電源去耦問題解析

盡管高速ADC給電源帶來的總負載是穩定的,但需要電流以ADC采樣速率和此頻率的諧波快速跳變。由于

2011-01-01 12:30:11 990

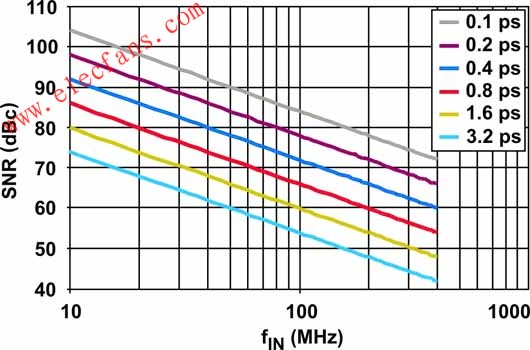

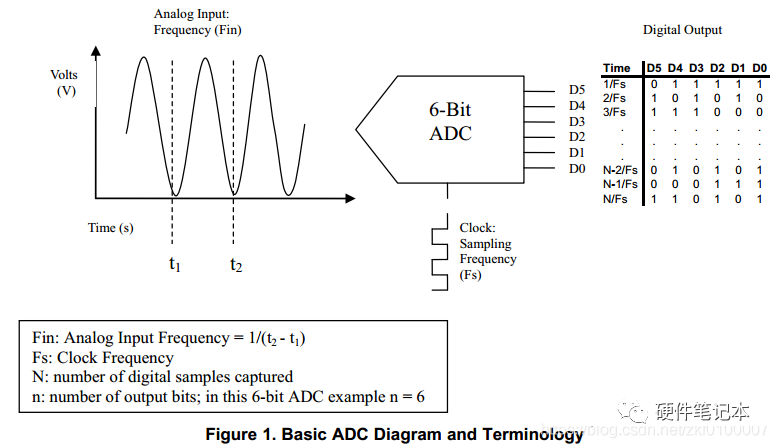

990 本文即第2部分中,這種組合抖動將用于計算ADC的信噪比 (SNR),之后將其與實際測量情況進行比較。

2012-05-07 11:31:22 1428

1428

模/數轉換器(ADC)電路設計中,特別是當系統設計人員需要處理各種擺幅的電壓信號時,很容易產生的一個誤區是縮小輸入信號范圍,以適應ADC的滿量程范圍,這將大大降低信噪比(SNR)。綜合來看,低壓

2013-09-22 12:12:56 3874

3874

圖所示電路是14位、125 MSPS四通道ADC系統的簡化圖,該電路使用后端數字求和將信噪比(SNR)從單通道ADC的 74 dBFS提升到四通道ADC的78.5 dBFS。這項技術特別適合要求高SNR(如超聲和雷達)的應用,并且利用了現代高性能、低功耗、四通道流水線式ADC。

2013-10-30 10:07:29 2206

2206

獲得ADC的最佳SNR性能并不僅僅是給ADC輸入提供低噪聲信號的問題,提供一個低噪聲基準電壓是同等重要。雖然基準噪聲在零標度沒有影響,但是在全標度,基準上的任何噪聲在輸出代碼中都將是可見的。對于某個

2022-07-13 09:17:27 1039

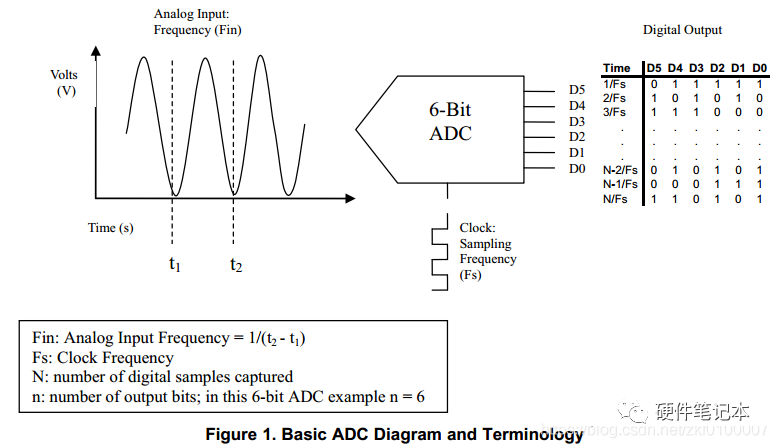

1039 本文的目的是介紹高速ADC相關的理論和知識,詳細介紹了采樣理論、數據手冊指標、ADC選型準則和評估方法、時鐘抖動和其它一些通用的系統級考慮。另外,一些用戶希望通過交織、平均或抖動(dithering)技術進一步提升ADC的性能。

2023-03-16 09:15:15 4738

4738 本文的目的是介紹高速ADC相關的理論和知識,詳細介紹了采樣理論、數據手冊指標、ADC選型準則和評估方法、時鐘抖動和其它一些通用的系統級考慮。 另外,一些用戶希望通過交織、平均或抖動(dithering)技術進一步提升ADC的性能。

2023-04-15 14:00:51 1333

1333

您在測試 ADC 的SNR時,您可能會連接一個低抖動時鐘器件到轉換器的時鐘輸入引腳,并施加一個適度低噪的輸入信號。如果您并未從您的轉換器獲得SNR產品說明書標稱性能,則說明存在

2011-10-12 12:00:09 2661

2661

大家好,我正在嘗試使用33210A信號發生器來確定PCB布局不佳的ADC的SNR損耗。來自數據表的ADC的SNR為85dB,我的測量結果為70dB。我需要確定ADC側的15dB差異以及mych如何來

2019-05-29 12:29:57

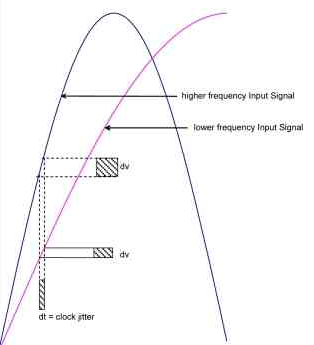

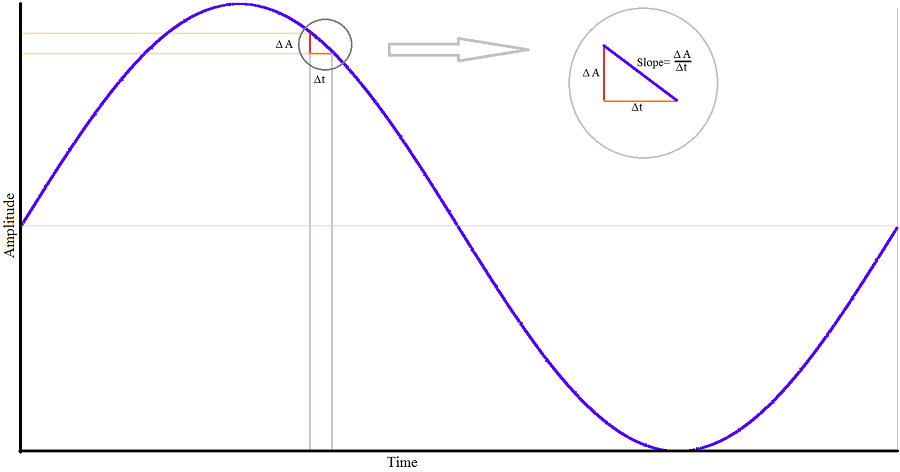

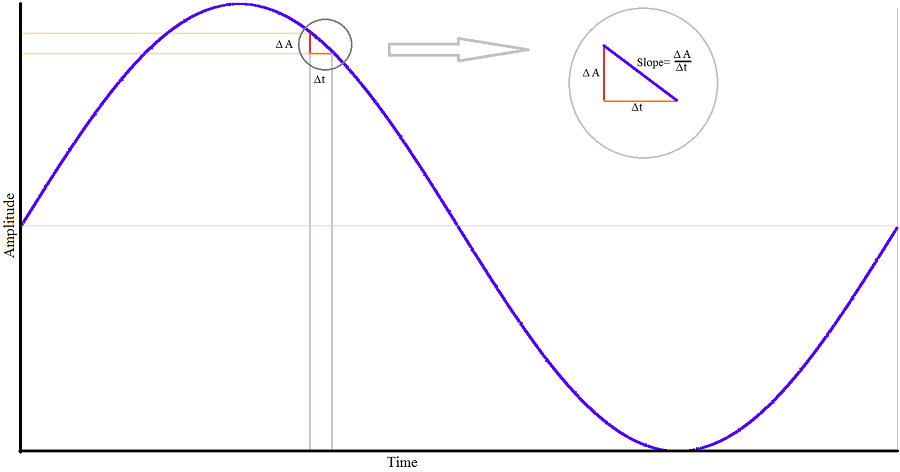

進行采樣。這要求具有穩定的采樣時 鐘,因為任何不理想的時鐘源都將產生一定相位噪聲。抖動是指采樣時鐘載波上兩個指定頻率偏移之間的時段上的相位噪聲積分。對于ADC,一般認為寬帶噪聲是最重要的因素

2019-10-23 08:00:00

來說,測試中需要對 ESG 或 PSG 產生的信號進行進一步的濾波以濾去諧波和雜散信號,濾波器的參數要根據用戶實際使用的信號頻率范圍選擇。對于高精度的 ADC 來說,采樣時鐘的抖動對于測試結果

2018-04-03 10:39:35

/1.8V)的 ADC功耗。因此,將該鏈的低噪聲 LDO去除可以產生巨大的節能效果。去除 LDO 還可以降低設計的板級空間、熱量以及成本。 本文闡述了包括超高性能 16 位 ADC 在內的一些 TI 高速

2018-09-26 11:04:47

至關重要。 噪聲信噪比(SNR)和失真要求對ADC的選擇有幫助,因而一般在設計早期確定。轉換器看到的噪聲量與其自己的噪聲量之比即為SNR。SNR與帶寬、信號質量(抖動)和增益相關。提高增益也會提高與之相關

2018-09-17 15:48:29

重新采樣數據,產生一個新的清潔數據流。這些器件可顯著提高信號質量,而且經常用在抖動規范極為嚴格的光模塊之前。除非距離信號源只有一英寸,否則很可能需要采用一個重定時器。重定時器實例包括DS100RT410

2018-09-13 10:02:04

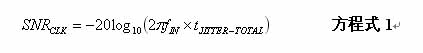

時鐘抖動引起的采樣噪聲為:

計算SNR為:

為何這里不像《[MT-001_cn] 揭開公式(SNR = 6.02N + 1.76dB)的神秘面紗,以及為什么我們要予以關注》文章里那樣,信號用

2023-12-01 08:30:52

C語言習題解析庫

2015-03-11 15:20:07

一個放大器系統:ADC + STA339BW + MCU,MCU產生12MHz時鐘應用于ADC(連接到MCLK引腳)和STA339BW(連接到XTI引腳)。我不知道會有多少差異,這會影響THD

2019-07-22 16:10:23

采樣時鐘考量在高性能采樣數據系統中,應使用低相位噪聲晶體振蕩器產生ADC(或DAC)采樣時鐘,因為采樣時鐘抖動會調制模擬輸入/輸出信號,并提高噪聲和失真底。采樣時鐘發生器應與高噪聲數字電路隔離

2014-11-20 10:58:30

-Delta ADC常見問題解答 ,歡迎小伙伴們下載~~附件Sigma-Delta ADC 常見問題解答_V2.0.pdf923.4 KB

2018-12-10 11:20:32

技術三千問:【技術三千問】之《玩轉ART-Pi》,看這篇就夠了!干貨匯總【技術三千問】之《AT組件問題匯總與解析》,干貨匯總!【技術三千問】之《UART串口問題解析》,干貨匯總!【技術三千問】之

2021-08-05 06:54:19

本文為高速數據轉換器提供了一個低抖動時鐘源的參考設計,目標是在時鐘頻率高達2GHz時,邊沿間抖動《 100fs。對于1GHz模擬輸出頻率,所產生的抖動信噪比SNR為:-20 × log(2 × π × f × tj) = -64dB。

2021-04-15 06:28:19

DN1013- 了解時鐘抖動對高速ADC的影響

2019-07-17 06:41:39

`描述此參考設計展示了高速放大器 THS4509 執行單端至差動轉換以驅動高速模數轉換器 (ADC),同時保持卓越的噪聲和失真性能的能力。為交流和直流耦合應用顯示了連接到 ADS4449 四通

2015-05-11 10:33:40

描述TIDA-01016 是一款適合高動態范圍高速 ADC 的時鐘解決方案。射頻輸入信號由高速 ADC 直接采用射頻取樣法捕獲。ADC32RF80 是一款雙通道 14 位 3GSPS 射頻取樣

2018-09-30 09:26:09

哪些參數會影響SNR?哪種評估SNR最好?以上來自于谷歌翻譯以下為原文 Which are the parameters that impact on SNR? Which is the best way to evaluate the SNR?

2018-09-28 16:47:28

時鐘抖動,這是ADC采樣頻率較高時常見的SNR降級原因之一。高速,高分辨率ADC對時鐘輸入的質量非常敏感。要在高速ADC中實現卓越的SNR,必須根據應用輸入頻率的要求仔細考慮均方根(rms)時鐘抖動

2018-11-01 11:33:13

引言要獲得 ADC 的最佳 SNR 性能并不僅僅是給 ADC 輸入提供低噪聲信號,提供一個低噪聲基準電壓是同等重要。雖然基準噪聲在零標度沒有影響,但是在全標度,基準上的任何噪聲在輸出代碼中都將是可見

2019-07-25 07:15:15

如何推導ADC的SNR?如何準確地估算某個時鐘源的抖動?如何將其與ADC的孔徑抖動組合?

2021-05-13 06:17:20

高信噪比=低ADC孔徑抖動嗎?在設計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉換為時間抖動呢?

2019-08-13 06:27:54

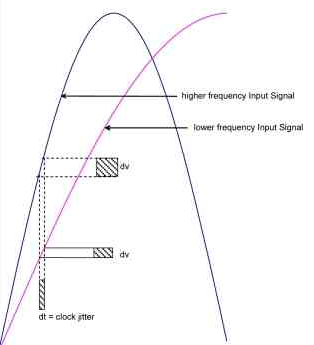

對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。那么時鐘抖動會對高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

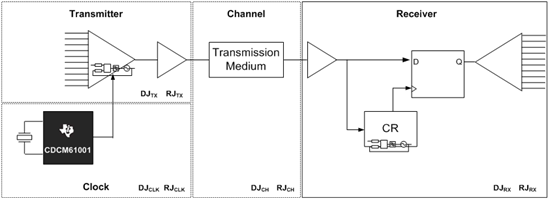

作者:John Johnson,德州儀器 本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成

2018-09-19 14:23:47

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成了各種委員會和標準機構,根據其開發標準的目標

2022-11-23 06:59:24

的時鐘源之問題。——Guy Hoover通常,它需要一個可具有高達 1nsRMS 抖動的函數發生器。常常需要采用一個高質量的 RF 發生器或晶體振蕩器以從 16 或 18 位 ADC 獲得最佳的 SNR

2018-07-19 16:23:22

是量化有用信號,產生量化噪聲的,對于1bitADC,產生7.78db的SNR本地噪聲是白噪聲,量化后還是白噪聲,所以幅值等完全不變這樣,只要對于本地噪聲比信號還大的場合,無論用什么ADC都可以,都不會劣化SNR類似的,時鐘抖動等均毫無影響 請問這種推論到底哪里有問題?錯在哪?

2018-08-19 06:31:10

讀寫24C02的時候為什么一直有IIC_Wait_Ack();ACK應答是自動產生的嗎?

2020-05-29 10:13:54

` 本帖最后由 web_master 于 2013-9-26 14:19 編輯

運算放大器經典問題解析——設計運放電路必備常識![hide] [/hide]`

2013-09-26 11:48:56

的。整個抖動轉移帶寬由低帶寬環路控制,典型情況下采用電壓控制晶體振蕩器(VCXO)。當CDR是系統中唯一的時鐘發生單元時,抖動轉移帶寬與抖動容差必須符合ITU-T規范。抖動產生是另一個重要的參數。抖動產生

2014-12-09 14:36:58

包含千兆采樣率ADC的系統設計會遇到許多復雜情況。面臨的主要挑戰包括時鐘驅動、模擬輸入級和高速數字接口。本文探討了如何才能克服這些挑戰,并給出了在千兆赫茲的速度下進行系統優化的方法。在討論中,時鐘

2019-05-30 05:00:04

電子設計競賽賽題解析

東西是非常不錯的,可供參考.

2016-12-17 12:43:15 0

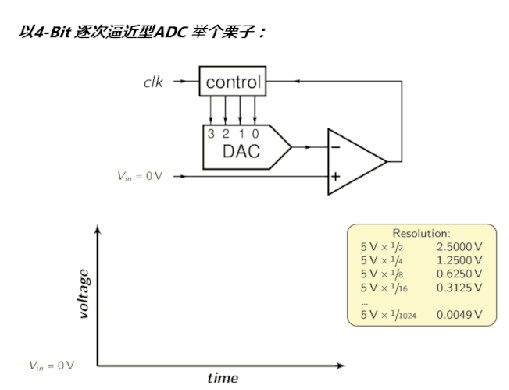

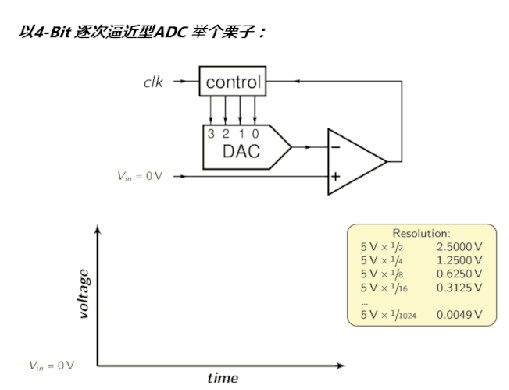

0 解析逐次逼近ADC

2009-05-04 13:29:41 24

24 本文研究了直擴超寬帶通信系統的關鍵技術----定時抖動及其抑制方法,主要分析了定時抖動產生的原因、分布規律和各種有效的抑制方法。文中第一次對DS-UWB 系統定時抖動產生的各

2009-08-10 14:24:07 15

15 極高速ADC(>1 GSPS)需要一種低抖動的采樣時鐘,以保持信噪比(SNR)。這些8比特和10比特轉換器具有由量化噪聲設置的最佳情形的噪聲基底。對滿量程正弦波進行采樣的N比特ADC,SNR的

2009-09-30 10:04:05 20

20 介紹了一種用于高速ADC 的低抖動時鐘穩定電路。這個電路由延遲鎖相環(DLL)來實現。這個DLL 有兩個功能:一是通過把一個時鐘沿固定精確延遲半個周期,再與另一個沿組成一個新

2009-11-26 15:55:15 28

28 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。

2009-11-27 11:24:07 15

15 高速互聯鏈路中參考時鐘的抖動分析與測量

在高速互聯鏈路中,發送器的參考工作時鐘的抖動是影響整個

2010-04-15 14:01:39 19

19 高速ADC供電指南

為使高速模數轉換器發揮最高性能,必須為其提供干凈的直流電源。高噪聲電源會導致信噪比(SNR)下降和/或ADC輸出中出現不良的雜散成分。本文將介紹有關ADC

2011-01-01 12:18:09 94

94 按鈕式數字電位器的防抖動和重復動作問題解決方法

介紹按鈕式數字電位器的防抖動和重復動作問題的一種解決方法,以及對數字電位器電壓、電流、級

2009-04-05 09:26:26 2871

2871

車臺天線的位置和輻射問題解析

1、車臺外接的天線,放在后備箱上比放在車頂中間的效果是不是差一些?

回答:車臺的天線共有四

2010-01-04 09:44:48 3186

3186 凌力爾特推出16位ADC,可實現實現卓越的SNR

不久前,凌力爾特公司(Linear)推出 16 位 SAR ADC LTC2393-16,該器件以高達 1Msps 的采樣率實現卓越的 94dB SNR,而且無周期延遲。LTC

2010-01-18 08:35:51 946

946 高速ADC,什么是高速ADC

背景知識:

隨著計算機技術、通信技術和微電子技術的高速發展,大大促進了ADC技術的發展,ADC作為模擬量與數據量接

2010-03-24 13:28:01 9741

9741 16位、1Msps SAR ADC實現94dB SNR、可測量±4.096V的寬輸入范圍

加利福尼亞州米爾皮塔斯 (MILPITAS, CA) – 2010 年 1 月 14 日 – 凌力爾特公司(Line

2010-12-26 15:40:19 1431

1431 您在使用一個高速模數轉換器 (ADC) 時,總是期望性能能夠達到產品說明書載明的信噪比 (SNR) 值,這是很正常的事情。您在測試 ADC 的 SNR 時,您可能會連接一個低抖動時鐘器件到

2011-01-05 10:44:48 1284

1284 為實現高信噪比(SNR),ADC的孔徑抖動必須很低(參見參考文獻1、2和3)。目前可提供孔徑抖動低至60 fs rms的ADC(AD9445 14位125 MSPS和AD9446 16位100 MSPS)。為了避免降低ADC的性能,必須采用抖動極低

2011-11-17 15:10:53 28

28 蘇泊爾微電腦電磁爐故障問題解析,本內容介紹了蘇泊爾電磁爐故障問題的分析

2012-05-11 15:14:47 6390

6390

SNR boost是一種噪聲成型技術,該技術能夠改變量化噪聲的頻譜

2013-03-14 16:02:01 17

17 自動控制原理習題解析,有需要的下來看看。

2016-05-05 14:06:42 0

0 風力擺控制系統賽題解析

2016-12-09 23:00:44 31

31 了解高速ADC時鐘抖動的影響將高速信號數字化到高分辨率要求仔細選擇一個時鐘,不會妥協模數轉換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數轉換器的性能

2017-05-15 15:20:59 13

13 新型的高速ADC 都具備高模擬輸入帶寬(約為最大采樣頻率的3 到6 倍),因此它們可以用于許多欠采樣應用中。ADC 設計的最新進展極大地擴展了可用輸入范圍,這樣系統設計人員便可以去掉至少一個中間頻率

2017-05-18 09:47:38 1

1 時鐘產生抖動(jitter)會使發生抖動的時鐘信號與未發生抖動的時鐘信號在時域上存在偏差,從而使模數轉換器的采樣頻率發生紊亂,最終導致模數轉換器采樣的不穩定性,使輸出信號存在頻譜毛刺,導致誤碼率上升

2017-11-11 18:22:26 9

9 本文主要討論采樣時鐘抖動對 ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。 ADC 是現代數字解調器和軟件無線電接收機中連接模擬信號處理部分和數字信號處理部分的橋梁,其性能在很大程度上決定

2017-11-27 14:59:20 17

17 本文繼續進行時鐘抖動的分析,闡明了如何通過改善ADC的孔徑抖動來提高ADC的SNR。

2018-05-08 17:48:41 7

7 《高等學校優秀教材?電工學知識要點與習題解析》為配合秦曾煌教授主編的《電工學》(第六版)而編寫的輔導書。《電工學知識要點與習題解析/高等學校優秀教材輔導叢書》主要包括知識要點、書后思考題解答、書后

2020-01-10 11:48:10 56

56 ADC 的 SNR:SNR(signal noise ratio)是指信噪比,受許多因素影響,包括分辨率,線性度和準確性(量化級別與真實模擬信號的匹配程度),混疊和抖動。ADC 的 SNR 通常

2020-08-13 17:25:09 2157

2157

對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。借助本文,我們將使讀者更好地理解時鐘抖動問題及其對高速ADC性能的影響。

2020-08-20 14:25:16 791

791

作為基線,DC1826A-A 的時鐘輸入采用一個羅德與施瓦茨 SMB100A RF 發生器來驅動,并由 Stanford Research SR1 提供模擬輸入。結果是圖 1 中的 PScope 數據,其產生一個 98.247dBFS SNR。

2021-01-04 15:44:49 2667

2667

AN-1221: 使用ADF4002 PLL產生高速模數轉換器所需的極低抖動編碼(采樣)時鐘

2021-03-19 08:59:00 13

13 16 位、1Msps SAR ADC 實現 94dB SNR、可測量 ±4.096V 的寬輸入范圍

2021-03-20 17:46:23 0

0 MT-200:降低ADC時鐘接口抖動

2021-03-21 01:18:30 7

7 DN568 - 基準濾波器使 32 位 ADC SNR 增加 6dB

2021-03-21 12:27:12 13

13 前言 :本文我們介紹下ADC采樣時鐘的抖動(Jitter)參數對ADC采樣的影響,主要介紹以下內容: 時鐘抖動的構成 時鐘抖動對ADC SNR的影響 如何計算時鐘抖動 如何優化時鐘抖動 1.采樣理論

2021-04-07 16:43:45 7378

7378

自適應抖動緩沖器-下載產生碼

2021-04-12 16:47:30 3

3 LTC2391-16:16位、250ksps SAR ADC,帶94dB SNR數據表

2021-04-17 09:25:40 2

2 LTC2373-18:18位、1Msps、8通道SAR ADC,帶100dB SNR數據表

2021-04-18 12:52:57 6

6 超低抖動時鐘的產生與分配

2021-04-18 14:13:51 8

8 LTC2378-16:16位、1 Msps、低功耗SAR ADC,帶97dB SNR數據表

2021-04-23 16:18:36 7

7 ADC時鐘接口中的最小抖動

2021-05-09 12:19:40 6

6 DN1013-了解時鐘抖動對高速ADC的影響

2021-05-11 18:22:19 0

0 LTC2392-16:16位、500ksps SAR ADC,帶94dB SNR數據表

2021-05-17 14:00:52 3

3 自適應抖動緩沖器-下載產生碼

2021-06-16 11:08:38 4

4 電工學-知識要點與習題解析電子版

2021-07-23 09:33:51 0

0 樊昌信《通信原理》真題解析及講義電子版

2021-09-06 14:40:47 0

0

?

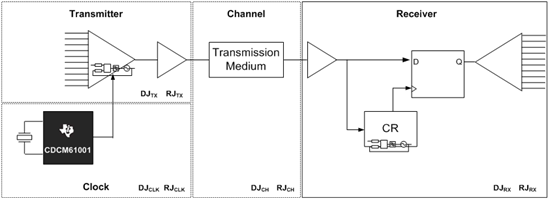

圖 1 顯示了集成有一個嵌入式時鐘的典型高速通信鏈路。每個子系統(時鐘、發送器、通道和接收機)都會對整體抖動預算的增加產生影響。子系統抖動包括一個決定性 (DJ) 組件和一個隨機組件 (RJ),如圖

2021-11-22 15:52:21 1284

1284

《電路考研精要與典型題解析》陳燕主編

2022-01-14 15:33:40 0

0 《信號與系統 第3版》習題解析

2022-03-21 15:06:19 0

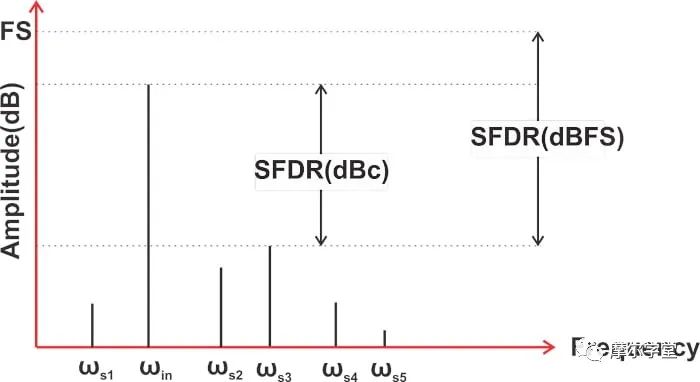

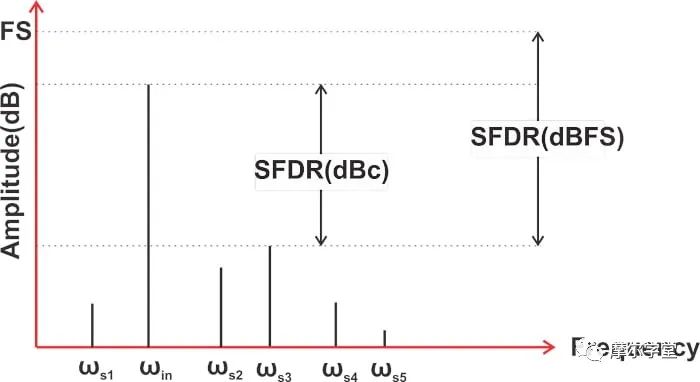

0 時鐘抖動、采樣率和量化噪聲是影響 ADC 中 SNR 和 SFDR 的最關鍵因素

2022-08-11 14:26:08 2684

2684

本文件的目的是介紹與高速模數轉換器(ADC)。本文件詳細介紹了抽樣理論,數據表規格、ADC選擇標準和評估方法、時鐘抖動等常見問題系統級問題。此外,一些最終用戶希望擴展通過實現交織、平均或抖動技術實現ADC。的好處和關注點本文討論了交織、平均和抖動ADC

2022-09-20 14:23:49 3

3 時鐘抖動解秘—高速鏈路時鐘抖動規范基礎知識

2022-11-07 08:07:30 1

1 源,即采樣保持 (S/H) 電路和 ADC 的編碼器部分。

我們還將了解 ADC 中 SFDR 和SNR(信噪比)之間的一般權衡,并為以后有關應用抖動技術改善 ADC SFDR 的有趣討論奠定

2023-05-11 15:22:25 892

892

比亞迪漢EV高速行駛抖動故障現象故障診斷故障排除一輛比亞迪漢EV,車主反饋車輛在120km/h高速行駛中有抖動現象。故障現象故障診斷故障排除原因分析1、車輪不平衡2、傳動半軸不平衡3、輪轂法蘭

2023-03-03 11:30:57 2009

2009

電子發燒友網站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費下載

2023-11-28 10:24:10 1

1

電子發燒友App

電子發燒友App

評論