ATK-精英STM32F103開發(fā)板 DEVB_115X117MM 6~24V

1970-01-01 08:00:00

異步SRAM存儲器接口電路設(shè)計(Altera FPGA開發(fā)板)如圖所示:

2012-08-15 14:37:05 3792

3792

FLASH存儲器接口電路圖(Altera FPGA開發(fā)板)

2012-08-15 14:36:31 6074

6074

在FPGA開發(fā)板上都有幾種不同的存儲器,比如SDRAM,F(xiàn)LASH,EPCS,還有內(nèi)部

2020-10-09 11:41:41 2721

2721 AS下載和調(diào)試接口電路(Altera FPGA開發(fā)板)如下圖所示:

2012-08-15 14:29:23 5436

5436

許多 FPGA 設(shè)計都采用高速存儲器接口,可能調(diào)試比較困難,不過只要采用正確的方法就能成功進(jìn)行調(diào)試。 現(xiàn)代 FPGA 通常連接高速 SRAM 和 SDRAM 存儲器 。要確保這種器件無差錯運(yùn)行,調(diào)試

2018-01-12 11:48:44 868

868

本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog設(shè)計Altera的DE2板上SDRAM存儲器。

2021-01-22 15:34:09 9

9 SDRAM作為大容量存儲器在高速圖像處理中具有很大的應(yīng)用價值。但由于SDRAM的結(jié)構(gòu)和SRAM不同,其控制比較復(fù)雜。文章詳細(xì)介紹了 SDRAM存儲器的結(jié)構(gòu)、接口信號和操作方法,以及 SDRAM控制器

2021-01-26 15:30:52 13

13 其他元件,占用了寶貴的電路板空間。

Stratix? III FPGA具有專用內(nèi)置I/O電路,降低了高速DDR3存儲器設(shè)計的難度。觀看這一演示,了解怎樣輕松實現(xiàn)1,067 Mbps DDR3存儲器

2018-06-22 02:04:00 3226

3226 使用功能強(qiáng)大的FPGA來實現(xiàn)一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲控制器,由于該公司出產(chǎn)的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 5款ALTERA FPGA開發(fā)板原理圖合集

2017-01-18 20:35:09 159

159 本資料是關(guān)于Altera公司 Stratix V GX FPGA開發(fā)板電路圖的資料。資料包括開發(fā)板原理圖、PCB圖。

2012-08-10 15:55:44 138

138 電源、時鐘和復(fù)位電路圖(Altera FPGA開發(fā)板)如圖所示:

2012-08-15 14:42:33 9299

9299

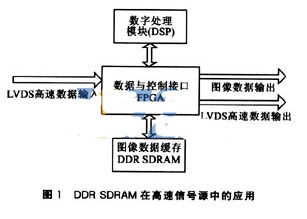

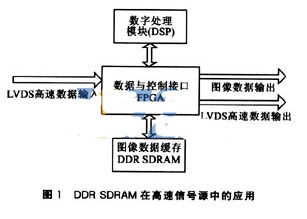

基于FPGA的高速SDRAM控制器的視頻應(yīng)用

0 引言 SDRAM(同步動態(tài)存儲器)是一種應(yīng)用廣泛的存儲器,具有容量大、數(shù)據(jù)讀寫速度快、價格低廉等優(yōu)點(diǎn),特別適

2009-11-04 09:56:20 817

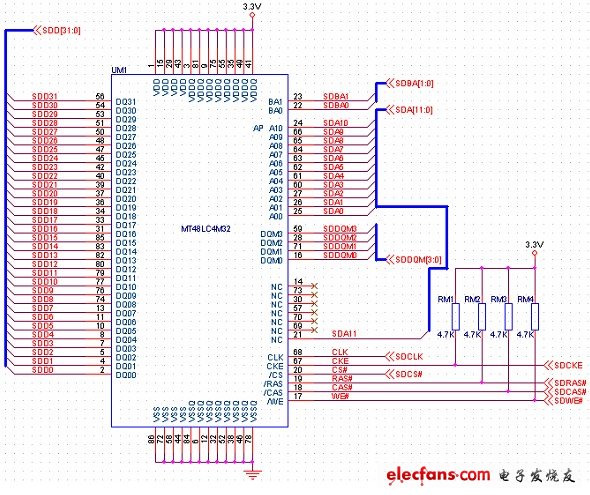

817 SDRAM幀存儲器部分電路

2010-05-07 18:41:54 21

21 最全面的fpga開發(fā)板電路圖,一共有10多份fpga開發(fā)板電路圖。

2012-04-19 12:50:50 131

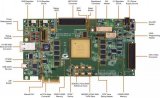

131 本系統(tǒng)的設(shè)計是基于Altera公司的EP2S60系列的開發(fā)板,板上集成兩片 SDRAM存儲芯片、視頻輸入接口和VGA輸出接口

2012-12-16 10:07:31 1185

1185 本教程介紹如何將Altera的DE2開發(fā)和教育板上的SDRAM芯片與使用Altera SOPC Builder實現(xiàn)的Nios II系統(tǒng)一起使用。本文的討論是基于這樣一個假設(shè):讀者可以訪問DE2板,并且熟悉教程介紹中使用VHDL設(shè)計的Altera SOPC Builder的內(nèi)容。

2021-01-22 15:34:11 9

9 開發(fā)板是用來進(jìn)行嵌入式系統(tǒng)開發(fā)的電路板,主要由嵌入式處理器、存儲器、輔助存儲器、通用接口四個部分構(gòu)成。那么開發(fā)板的常見分類有哪些呢?

2022-01-25 14:51:37 5765

5765 電子發(fā)燒友網(wǎng)訊 :Altera 公司與FPGA高性能知識產(chǎn)權(quán)(IP)內(nèi)核領(lǐng)先供應(yīng)商N(yùn)orthwest Logic2012年11月14號宣布,開始提供硬件成熟的1,600 Mbps低延時DRAM (RLDRAM) 3存儲器接口解決方案,可用于

2012-11-15 09:32:59 738

738 華清遠(yuǎn)見FPGA代碼-在Altera的FPGA開發(fā)板上運(yùn)行第一個FPGA程序

2016-10-27 18:07:54 16

16 本文檔的主要內(nèi)容詳細(xì)介紹的是Altera Cyclone III系列FPGA開發(fā)板的庫文件免費(fèi)下載。

2021-03-07 08:00:00 16

16 開發(fā)板是用來進(jìn)行嵌入式系統(tǒng)開發(fā)的電路板,包括中央處理器、存儲器、輸入設(shè)備、輸出設(shè)備、數(shù)據(jù)通路/總線和外部資源接口等一系列硬件組件。在一般的嵌入式系統(tǒng)開發(fā)過程中,硬件一般被分成兩個平臺,一個是開發(fā)平臺

2017-10-23 17:18:57 3966

3966 Digilent公司推出了一款新型的基于FPGA的硬件開發(fā)平臺,NEXYSTM3開發(fā)板。此開發(fā)板采用了Xilinx公司最先進(jìn)的Spartan6 FPGA芯片,擁有48M字節(jié)大小的外部存儲器、USB以及以太網(wǎng)接口,還有其他通

2011-08-22 09:28:43 1216

1216 利用Virtex-5 FPGA迎接存儲器接口設(shè)計挑戰(zhàn):在不支持新的接口協(xié)議時,存儲器接口設(shè)計師總是試圖支持越來越快的接口總線速度。目前,源同步雙數(shù)據(jù)速率 (DDR)存儲器件,例如 DDR2 SDRAM

2010-04-25 10:28:16 57

57 SDRAM存儲器相關(guān)資料下載

2018-05-02 11:46:57 49

49 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA讀寫SDRAM存儲器的實例工程文件和程序免費(fèi)下載。

2020-12-18 16:13:13 10

10 SDRAM存儲器接口電路設(shè)計,5.異步SRAM存儲器接口電路設(shè)計,6.FLASH存儲器接口電路設(shè)計,7.電源, 時鐘和復(fù)位電路設(shè)計,8.FPGA最小系統(tǒng)的調(diào)試方法和技巧

2019-04-04 17:18:48 101

101 在FPGA開發(fā)板上都有幾種不同的存儲器,比如SDRAM ,F(xiàn)LASH,EPCS,還有內(nèi)部onchip memory,這幾種存儲器間是如何通信或者構(gòu)建一個系統(tǒng)該如何搭配他們呢, 不少人都問到這個問題。在這里我做個總結(jié)以方便初學(xué)者的學(xué)習(xí)。

2020-10-12 16:57:00 25

25 3.0設(shè)計。使用這些開發(fā)板可開發(fā)和測試由DDR4、DDR3、QDR IV和RLDRAM III存儲器組成的存儲器子系統(tǒng)。

2023-09-07 10:15:33 533

533

,因此能夠很好地滿足上述場合對大量數(shù)據(jù)緩存的需求。但DDR SDRAM的接口不能直接與現(xiàn)今的微處理器和DSP的存儲器接口相連,需要在其間插入控制器實現(xiàn)微處理器或DSP對存儲器的控制。

2019-07-02 08:03:00 3865

3865

,最大用戶IO個數(shù)為91。 板卡提供JTAG和AS兩種配置FPGA接口,JTAG方式主要用于板 卡調(diào)試,下載速度快,但程序不會寫入存儲器,掉電后需要重新 用J

2019-01-04 13:43:34 25413

25413 基于FPGA的高速固態(tài)存儲器優(yōu)化設(shè)計_楊玉華

2017-01-13 21:40:36 1

1 簡單51單片機(jī)開發(fā)板的電路設(shè)計(單片機(jī)控制電機(jī))-該文檔為簡單51單片機(jī)開發(fā)板的電路設(shè)計講解資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-22 10:03:57 88

88 電子發(fā)燒友網(wǎng)站提供《如何實現(xiàn)SDRAM存儲器并通過接口連接到高性能微控制器.zip》資料免費(fèi)下載

2022-09-07 09:31:55 1

1 控制器用戶接口設(shè)計方案。該控制器用戶接口已經(jīng)在Xilinx 公司的VC707 開發(fā)板上通過了功能驗證,并成功的被應(yīng)用到高速圖像數(shù)據(jù)采集系統(tǒng)中。

2017-11-17 14:14:02 3091

3091

系統(tǒng)架構(gòu)師必須解決高性能系統(tǒng)應(yīng)用的一些復(fù)雜問題,包括體系結(jié)構(gòu)、算法和功能范圍。一般而言,這些應(yīng)用中一個基本的問題是存儲器,作為系統(tǒng)性能的瓶頸和挑戰(zhàn)經(jīng)常位于存儲器的體系結(jié)構(gòu)中。由于外部存儲器需要更快

2018-12-24 08:00:00 14

14 開發(fā)板(demoboard)是用來進(jìn)行嵌入式系統(tǒng)開發(fā)的電路板,包括中央處理器、存儲器、輸入設(shè)備、輸出設(shè)備、數(shù)據(jù)通路/總線和外部資源接口等一系列硬件組件。開發(fā)板一般由嵌入式系統(tǒng)開發(fā)者根據(jù)開發(fā)需求自己訂制,也可由用戶自行研究設(shè)計。

2017-12-09 09:40:08 100881

100881 PLC系統(tǒng)存儲器與用戶存儲器的功能(嵌入式開發(fā)板有哪些功能接口)-該文檔為PLC系統(tǒng)存儲器與用戶存儲器的功能總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 09:47:10 11

11 Cyclone IV GX FPGA開發(fā)板為開發(fā)和原型化低功耗、大容量、功能豐富的設(shè)計提供了硬件平臺,并演示了Cyclone IV GX器件的片上存儲器、嵌入式乘法器和Nios∈II嵌入式軟處理器。該板提供外圍設(shè)備和存儲器接口,以促進(jìn)Irror IV GX FPGA設(shè)計的發(fā)展。

2018-11-22 08:00:00 6

6 邏輯復(fù)雜,接口方式與普通的存儲器差異很大。為了解決這個矛盾,需要設(shè)計專用的SDRAM控制器,使用戶像使用SRAM -樣方便的使用SDRAM。考慮到控制器的通用性,本文中提出了一種通用的SDRAM控制器的FPGA設(shè)計,FPGA內(nèi)部采用狀態(tài)機(jī)的方式。該設(shè)計采用了AD公

2017-11-28 19:51:26 5

5 FPGA設(shè)計的高速FIFO電路技術(shù)

本文主要介紹高速FIFO電路在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,相關(guān)電路主要有高速A/D轉(zhuǎn)換器、FPGA、SDRAM存儲器等。圖1為本方案的結(jié)構(gòu)框圖。在大容量

2010-05-27 09:58:59 2092

2092

斑梨電子FPGA CycloneII EP2C5T144 學(xué)習(xí)板 開發(fā)板產(chǎn)品參數(shù)1. 采用ALTERA公司的CyclonellEP2C5T144芯片作為核心最小系統(tǒng),將FPGA

2023-02-03 15:14:29

,SDRAM的原理和時序,SDRAM控制器,動態(tài)隨即存儲器SDRAM模塊功能簡介,基于FPGA的SDRAM控制器的設(shè)計和實現(xiàn),一種簡易SDRAM控制器的設(shè)計方法

2018-12-25 08:00:00 56

56 高速電路板布板指南-Altera

2022-12-30 09:22:20 0

0 ETL-002 FPGA開發(fā)板是以Altera公司的最新系列Cyclone III中的3C10為主芯片,并提供了極為豐富的芯片外圍接口資源以及下載線,數(shù)據(jù)線以及資料光盤等。除了這些硬件外,我們還提供了十多個

2011-04-17 22:11:28 132

132 ,SDRAM是非常流行的存儲器。它們不像靜態(tài)存儲器那樣容易控制,因此經(jīng)常使用SDRAM控制器。 FPGA器件屬于專用集成電路中的一種半定制電路,是可編程的邏輯列陣,能夠有效的解決原有的器件門電路數(shù)較少的問題。FPGA的基本結(jié)構(gòu)包括可編程輸入輸出單元,可配

2020-05-19 17:35:14 1647

1647

Altera公司(Nasdaq: ALTR)今天宣布,在硅片中演示了DDR4存儲器接口,其工作速率是業(yè)界最高的2,666 Mbps。

2014-12-19 15:13:01 3754

3754 PLC核心開發(fā)板是用于開發(fā)和測試PLC系統(tǒng)的關(guān)鍵組件。它具有以下幾個優(yōu)點(diǎn): (1)強(qiáng)大的計算能力:PLC核心開發(fā)板通常集成了高性能處理器和大容量存儲器,具有強(qiáng)大的計算和存儲能力。這使得它能夠處理復(fù)雜

2023-09-22 08:40:03 110

110

正在加载...

3792

3792 3792

3792

2721

2721 2721

2721 5436

5436 5436

5436

868

868 868

868

9

9 9

9 13

13 13

13 3226

3226 3226

3226 237

237 237

237 138

138 138

138 電子發(fā)燒友App

電子發(fā)燒友App

評論