幾乎每個RF和微波系統(tǒng)都需要頻率合成器。頻率合成器產(chǎn)生本振信號以驅(qū)動混頻器、調(diào)制器、解調(diào)器及其他許多RF和微

2017-12-07 07:11:00 8835

8835

要滿足苛刻的頻率合成器要求,通常需要做到一定程度的設(shè)計(jì)靈活性。基本的鎖相環(huán)(PLL)頻率合成器能以低成本、高空間效率、低功耗封裝提供合理的頻譜純度和頻率捷變,因此它在射頻(RF)系統(tǒng)核心位置發(fā)揮作用

2022-10-14 10:30:36 2027

2027 頻率合成器的核心是鑒相器或鑒頻鑒相器。在這里,將參考頻率信號與VCO輸出反饋的信號進(jìn)行比較,產(chǎn)生的誤差信號用于驅(qū)動環(huán)路濾波器和VCO。在數(shù)字PLL(DPLL)中,鑒相器或鑒頻檢波器是一個邏輯元件。三種最常見的實(shí)現(xiàn)是:

2023-01-30 10:19:07 1584

1584

本篇文章是關(guān)于相位鎖定環(huán)(PLL)頻率合成器的設(shè)計(jì)和分析,重點(diǎn)討論了相位噪聲和頻率噪聲的測量、建模和仿真方法。文章以設(shè)計(jì)一個假想的PLL頻率合成器為例,詳細(xì)介紹了設(shè)計(jì)過程和步驟。從規(guī)格選擇、電路配置

2023-10-26 15:30:51 483

483

概述:ADF41020是一款18GHz微波PLL頻率合成器,ADF41020 頻率合成器在無線接收機(jī)和發(fā)射機(jī)的上變頻和下變頻部分中,可用來實(shí)現(xiàn)高達(dá)18 GHz 的本振。

2021-04-12 07:59:42

的輸出,并且如果正弦波不夠完美的話,在振蕩器內(nèi)部稍微改造下來改變它的性能。當(dāng)合成器執(zhí)行反饋時,它們有時稱為鎖相環(huán)或PLL。www實(shí)際生活中的介成器作常復(fù)雜,也很昂貴。它們可以完成許多功能而不僅僅是反饋

2017-12-06 14:06:07

EV-ADF411xSD1Z,用于評估ADF411x整數(shù)N和小數(shù)N分頻PLL頻率合成器的評估板。 SDP-S控制器板允許對頻率合成器進(jìn)行軟件編程。它顯示了電路板,其中包含頻率合成器的足跡,電源

2019-07-15 10:29:22

EVAL-ADF4351EB1Z,該板設(shè)計(jì)用于允許用戶評估ADF4351頻率合成器的性能,以實(shí)現(xiàn)鎖相環(huán)(PLL)。它顯示了該板,其中包含ADF4351集成合成器和VCO,用于輸出信號的SMA連接器

2019-03-01 08:03:03

。選擇頻率合成器芯片時,第一步是決定使用整數(shù)N還是分?jǐn)?shù)N型頻率合成器。設(shè)計(jì)良好的Σ-Δ分?jǐn)?shù)N頻率合成器能夠在相位噪聲、PLL鎖定時間和鑒相噪聲抑制方面提供優(yōu)異的性能。雖然分?jǐn)?shù)N頻率合成器的成本不斷降低,但

2019-06-26 06:42:04

優(yōu)勢擴(kuò)展到高性能用于軍事,空間和地面應(yīng)用的合成器。 產(chǎn)品名稱:鎖相環(huán)產(chǎn)品型號: MTI頻率合成器 MTI鎖相環(huán)特征鎖相環(huán)直接數(shù)字合成多輸出頻率相位(時間)同步輸出抗沖擊和隔離系統(tǒng)低g靈敏度BIT監(jiān)視器

2019-06-23 17:07:53

的輸出能否具有調(diào)幅(AM)、調(diào)頻(FM)和調(diào)相(PM)等功用。 隨著電子技術(shù)的不時開展,對頻率合成器性能的請求越來越高。20世紀(jì)80年代以來,各國都在研制和開展各自的DDS產(chǎn)品,如今盛行的DDS產(chǎn)品以

2020-03-17 14:54:24

:直接合成法和間接合成法,其形式有:直接頻率合成器、鎖相頻率合成器和直接數(shù)字頻率合成器。目前應(yīng)用較普遍的是直接數(shù)字頻率合成(DDS),其優(yōu)點(diǎn)是分辨率高、成本低、控制靈活;其主要缺點(diǎn)是輸出頻率上限不能太高

2012-08-02 11:08:55

頻率合成技術(shù)是現(xiàn)代通信的重要組成部分,它是將一個高穩(wěn)定度和高準(zhǔn)確度的基準(zhǔn)頻率經(jīng)過四則運(yùn)算,產(chǎn)生同樣穩(wěn)定度和準(zhǔn)確度的任意頻率。頻率合成器是電子系統(tǒng)的心臟,是影響電子系統(tǒng)性能的關(guān)鍵因素之一。本文結(jié)合

2019-06-25 06:36:13

問:什么是PLL頻率合成器?

2019-09-17 19:00:51

頻率合成器是利用一個或多個基準(zhǔn)頻率,通過各種技術(shù)途徑產(chǎn)生一系列的離散頻率信號的設(shè)備。這些頻率的穩(wěn)定度和精度均和基準(zhǔn)頻率相同,而且頻率的轉(zhuǎn)換時間很短,這樣才會有效率和實(shí)用價值。 頻率合成器的實(shí)現(xiàn)

2019-08-19 19:18:00

【作者】:廖梁兵;鄧賢進(jìn);張紅雨;【來源】:《信息與電子工程》2010年01期【摘要】:簡要介紹毫米波頻率合成器的重要性,分析兩種毫米波頻率合成器實(shí)現(xiàn)方案的優(yōu)劣,綜合其優(yōu)點(diǎn),并采用直接數(shù)字頻率合成

2010-04-22 11:47:22

Si4133-EVB,Si4133-BT PLL頻率合成器評估板。該板包括評估合成器所需的所有支持電路,包括參考時鐘,用于外部測量設(shè)備的SMA連接,以及用于控制設(shè)備的個人計(jì)算機(jī)接口。 PC軟件是一個易于使用的圖形界面,允許用戶通過并行端口連接直接輸入頻率,設(shè)置分頻比和切換功率控制選項(xiàng)

2020-07-30 10:21:46

直接數(shù)字頻率合成(DDS)在過去十年受到了頻率合成器設(shè)計(jì)工程師極大的歡迎,它被認(rèn)為是一種具有低相位噪聲和優(yōu)良雜散性能的靈活的頻率源,基于DDS的頻率合成器在許多應(yīng)用中能比基于鎖相環(huán)(PLL)頻率

2019-07-08 07:26:17

本文設(shè)計(jì)了一種多環(huán)鎖相頻率合成器。多環(huán)鎖相環(huán)路有直接數(shù)字頻率合成(DDS)環(huán)路和鎖相頻率合成環(huán)路(PLL)組成。充分利用兩個不同環(huán)路的優(yōu)點(diǎn),既保證了高的輸出頻率,又得到了較高的頻率分辨率。【關(guān)鍵詞

2010-05-13 09:09:53

。本文結(jié)合FPGA技術(shù)、鎖相環(huán)技術(shù)、頻率合成技術(shù),設(shè)計(jì)出了一個整數(shù)/半整數(shù)頻率合成器,能夠方便地應(yīng)用于鎖相環(huán)教學(xué)中,有一定的實(shí)用價值。那么有誰知道具體該如何利用FPGA設(shè)計(jì)PLL頻率合成器嗎?

2019-07-30 07:55:22

PLL應(yīng)用中頗具價值的注意事項(xiàng)和使用技巧基于鎖相環(huán)(PLL)技術(shù)的頻率合成器

2021-05-12 06:59:03

本文將介紹DDS和PLL的工作原理,并結(jié)合一電臺(工作頻率2 MHz~500 MHz)的設(shè)計(jì),給出DDS做參考的PLL頻率合成器的設(shè)計(jì)方案。

2021-04-20 06:42:27

提供大量精確且能迅速轉(zhuǎn)換的載波信號和本振信號,完全滿足現(xiàn)代通信的需要。其中鎖相頻率合成器具有工作頻帶寬、工作頻率高、頻譜質(zhì)量好、方案簡單、造價低等優(yōu)點(diǎn),在目前現(xiàn)有的頻率合成方法中應(yīng)用最為廣泛。

2019-08-22 07:55:34

EV-ADF41020EB1Z,用于ADF41020 PLL頻率合成器評估板的評估板。評估用于鎖相環(huán)(PLL)的ADF41020頻率合成器。它包含ADF41020合成器,100 MHz TCXO,電源,USB接口和RF輸出。板載有一個有源環(huán)路濾波器和一個13 GHz VCO

2019-02-28 07:23:02

要滿足苛刻的頻率合成器要求,通常需要做到一定程度的設(shè)計(jì)靈活性。基本的鎖相環(huán)(PLL)頻率合成器能以低成本、高空間效率、低功耗封裝提供合理的頻譜純度和頻率捷變,因此它在射頻(RF)系統(tǒng)核心位置發(fā)揮作用

2019-07-08 06:10:06

提供大量精確且能迅速轉(zhuǎn)換的載波信號和本振信號,完全滿足現(xiàn)代通信的需要。其中鎖相頻率合成器具有工作頻帶寬、工作頻率高、頻譜質(zhì)量好、方案簡單、造價低等優(yōu)點(diǎn),在目前現(xiàn)有的頻率合成方法中應(yīng)用最為廣泛。

2019-08-06 06:55:11

DDS9850的原理是什么?怎樣去設(shè)計(jì)數(shù)字化可編程頻率合成器?DDS與使用PLL技術(shù)實(shí)現(xiàn)的頻率合成器相比,有哪些優(yōu)勢?

2021-04-20 07:30:07

能否用頻率合成器,如ADF4351來做PLL,VCO的開環(huán)FSK調(diào)制呢。如何不行,能否給一些芯片選型的建議。

2018-12-26 14:27:58

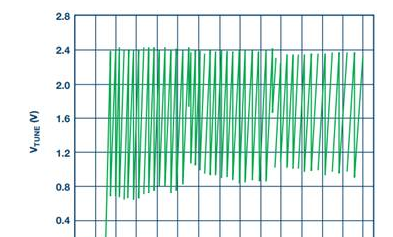

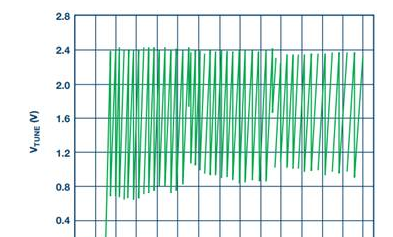

頻率合成器的主要性能指標(biāo)鎖相環(huán)頻率合成器原理鎖相環(huán)頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

文章分析了小數(shù)分頻頻率合成器中存在的相位雜散的問題,介紹了采用Σ — Δ 調(diào)

制技術(shù)的小數(shù)頻率合成器。詳細(xì)介紹了Σ — Δ 調(diào)制頻率合成器的原

2009-08-19 11:00:37 12

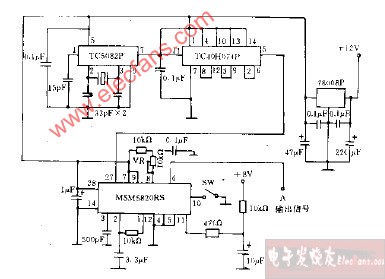

12 本文討論了DDS+PLL 結(jié)構(gòu)頻率合成器硬件電路設(shè)計(jì)中需要考慮的幾方面問題并給出了設(shè)計(jì)原則,依此原則我們設(shè)計(jì)了一套短波波段頻率合成器,實(shí)驗(yàn)結(jié)果證實(shí)了其可行性。

2009-09-07 16:07:29 34

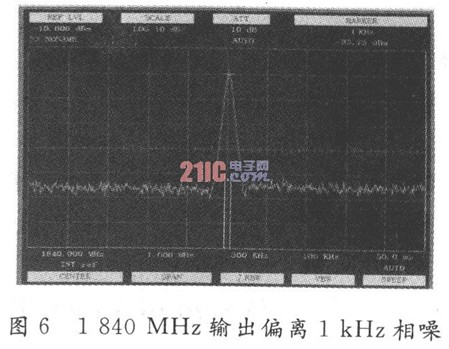

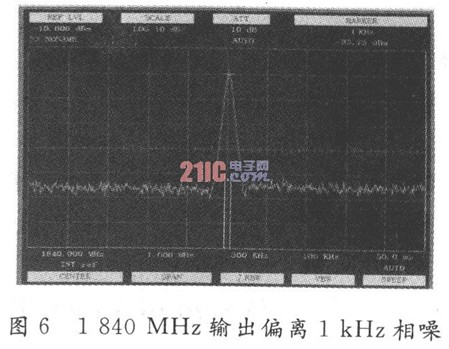

34 PLL頻率合成器的噪聲基底測量

在無線應(yīng)用中,相位噪聲是頻率合成器的關(guān)鍵性能參數(shù)。像PHS、GSM和IS-54等相位調(diào)制蜂窩系統(tǒng)的RF系統(tǒng)設(shè)計(jì)均需要低噪聲本地振蕩(L

2010-04-07 15:25:21 22

22 應(yīng)用FPGA,采用PLL頻率合成技術(shù),結(jié)合教學(xué)實(shí)驗(yàn)平臺的需要,設(shè)計(jì)出了一個整數(shù)/半整數(shù)頻率合成器,輸出范圍為1kHz~999.5kHz,步進(jìn)頻率可達(dá)到0.5kHz。與以前的教學(xué)實(shí)驗(yàn)裝置相比,系統(tǒng)在性能指

2010-09-01 09:43:34 45

45

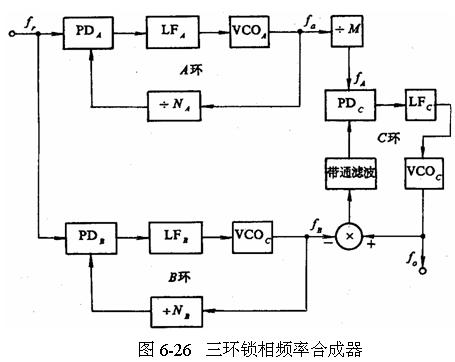

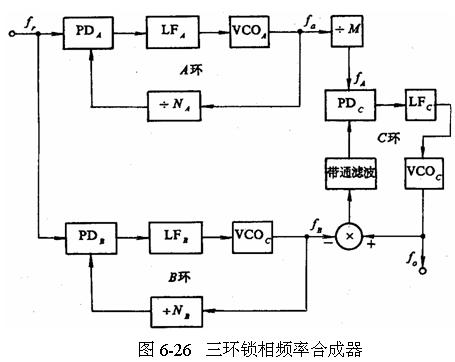

三環(huán)鎖相頻率合成器

2008-04-21 14:30:43 2076

2076

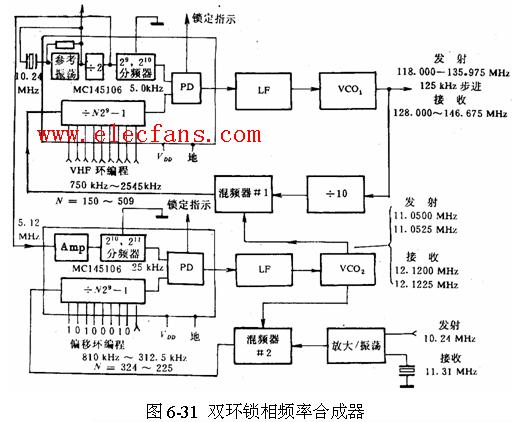

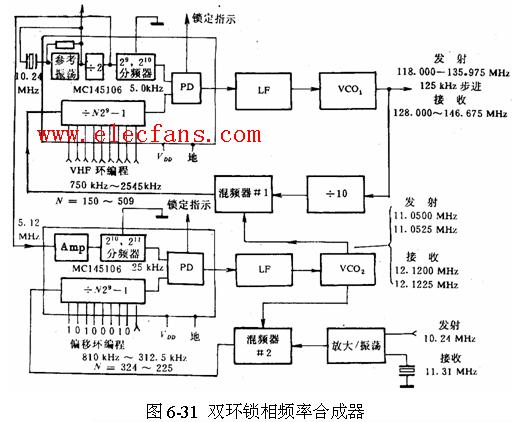

雙環(huán)鎖相頻率合成器

2008-04-21 14:38:36 1088

1088

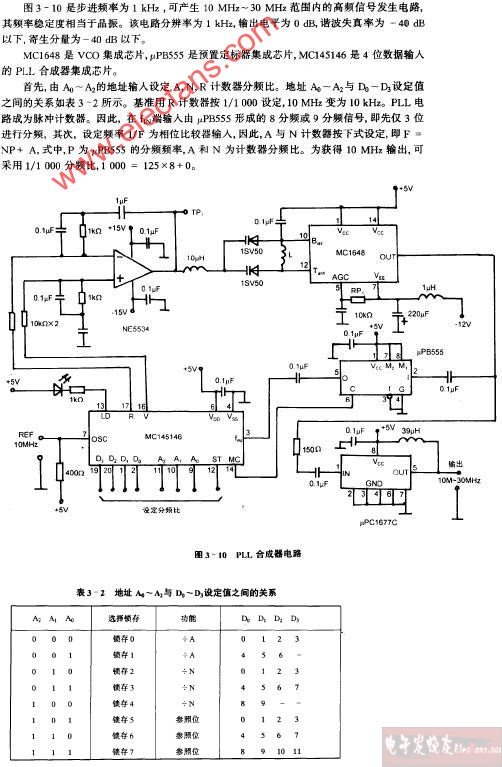

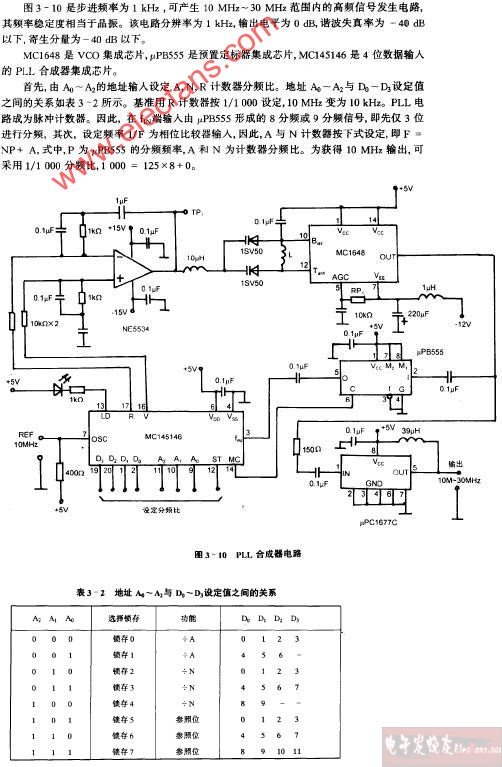

PLL合成器電路圖

2009-07-14 17:08:22 439

439

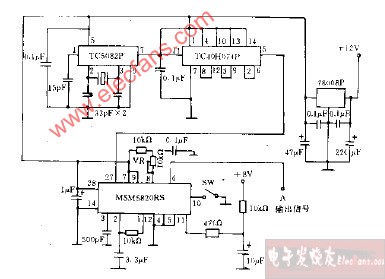

采用PLL的頻率合成器電路圖

2009-07-20 11:38:29 1118

1118

ADI推出靈活、高性價比雷達(dá)系統(tǒng)的 PLL 合成器

Analog Devices, Inc.最新推出的 ADF4158PLL 合成器,可靈活 、高性價比地實(shí)現(xiàn) FMCW (頻率調(diào)制連續(xù)波)雷達(dá)系統(tǒng)。FMCW 雷達(dá)系統(tǒng)廣

2010-01-12 17:58:32 843

843 ADI發(fā)布新款PLL合成器,用于實(shí)現(xiàn)高性價比FMCW雷達(dá)系統(tǒng)

Analog Devices, Inc.,最新推出的 ADF4158 PLL 合成器,可靈活 、高性價比地實(shí)現(xiàn) FMCW(頻率調(diào)制連續(xù)波)雷達(dá)系統(tǒng)。FMCW

2010-01-13 08:37:59 899

899 ADI推出的 ADF4158 PLL 合成器

ADI最新推出的 ADF4158 PLL 合成器,可靈活 、高性價比地實(shí)現(xiàn) FMCW (頻率調(diào)制連續(xù)波)雷達(dá)系統(tǒng)。FMCW 雷達(dá)系統(tǒng)廣泛應(yīng)用于汽車、航空、軍事、工業(yè)

2010-01-13 11:38:55 1287

1287 頻率合成器,頻率合成器原理及作用是什么?

所謂的頻率合成器,就是以一個精確度、穩(wěn)定度極好的石英晶體振蕩器作為基準(zhǔn)頻率,并利用加、減

2010-03-23 11:04:54 14601

14601 什么是直接式頻率合成器(DS)

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)的“心臟”。現(xiàn)代戰(zhàn)

2010-03-23 11:23:38 1607

1607 間接式頻率合成器(IS)的定義和原理是什么?

頻率合成的歷史 頻率合成器被人們喻為眾多電子系統(tǒng)的“心臟”。現(xiàn)代戰(zhàn)爭是

2010-03-23 11:31:41 2157

2157 單環(huán)鎖相頻率合成器,單環(huán)鎖相頻率合成器是什么意思

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)的“心臟”。現(xiàn)代戰(zhàn)爭是

2010-03-23 11:36:28 883

883 變模分頻鎖相頻率合成器是什么意思

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)的“心臟”。現(xiàn)代戰(zhàn)爭是爭奪電子頻譜控

2010-03-23 11:41:23 1384

1384 集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)

2010-03-23 11:45:44 770

770 DDS+PLL高性能頻率合成器的設(shè)計(jì)方案

頻率合成理論自20世紀(jì)30年代提出以來,已取得了迅速的發(fā)展,逐漸形成了直接頻率合成技術(shù)、鎖相頻率合成技術(shù)、直接數(shù)字式頻率

2010-04-17 15:22:13 3209

3209

針對RF設(shè)計(jì)的新版PLL頻率合成器設(shè)計(jì)軟件

ADI全球領(lǐng)先的高性能信號處理解決方案供應(yīng)商,和提供覆蓋整個RF信號鏈的RF IC功能模塊的全球領(lǐng)導(dǎo)者,最

2010-05-24 11:21:08 731

731 對體積、速度和省電的更進(jìn)一步的要求推動了頻率合成器技術(shù)的發(fā)展。目前頻率合成器的一個明顯趨勢是集成了越來越多的微型鎖相環(huán)(PLL)/壓控振蕩器(VCO)元件。過去在PCB上的多個元

2010-05-28 11:11:31 1858

1858 頻率合成器可以提供大量精確、穩(wěn)定的頻率作為無線通信設(shè)備的本振信號。簡要介紹了鎖相環(huán)頻率合成器的基本原理,并利用整數(shù)N鎖相芯片ADF4112設(shè)計(jì)了一個寬波段的頻率合成器。討論

2011-05-03 18:20:24 101

101 雜散抑制是PLL 頻率合成器的幾個關(guān)鍵指標(biāo)之一。在實(shí)際設(shè)計(jì)中,雜散的輸出種類比較多,產(chǎn)生的原因也各不一樣,但是它們中的大多數(shù)并不常見。首先從雜散的基本概念出發(fā),詳細(xì)地介紹了

2011-09-01 16:34:56 68

68 ADF4xxx系列PLL頻率合成器的鎖定檢測

2011-11-29 15:37:17 38

38 為了滿足寬頻段、細(xì)步進(jìn)頻率綜合器的工程需求,對基于多環(huán)鎖相的頻率合成器進(jìn)行了分析和研究。在對比傳統(tǒng)單環(huán)鎖相技術(shù)基礎(chǔ)上,介紹了采用DDS+PLL多環(huán)技術(shù)實(shí)現(xiàn)寬帶細(xì)步進(jìn)頻綜,輸

2013-04-27 16:26:51 48

48 DDS-PLL組合跳頻頻率合成器,有需要的都可以看看。

2016-07-20 15:48:57 42

42 學(xué)習(xí)單片機(jī)電路圖的很好的資料——DDS-PLL組合跳頻頻率合成器

2016-11-03 15:15:39 0

0 您曾設(shè)計(jì)過具有分?jǐn)?shù)頻率合成器的鎖相環(huán)(PLL)嗎?這種合成器在整數(shù)通道上看起來很棒,但在只稍微偏離這些整數(shù)通道的頻率點(diǎn)上雜散就會變得高很多,是吧?如果是這樣的話,您就已經(jīng)遇到過整數(shù)邊界雜散現(xiàn)象了 該現(xiàn)象發(fā)生在載波的偏移距離等于到最近整數(shù)通道的距離時。

2017-04-08 03:56:11 4188

4188

結(jié)合數(shù)字式頻率合成器(DDs)和集成鎖相環(huán)(PLL)各自的優(yōu)點(diǎn),研制并設(shè)計(jì)了以DDS芯片AD9954和集成鎖相芯片ADF4113構(gòu)成的高分 辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器進(jìn)行了分析

2017-10-27 17:54:21 8

8 頻率合成器是決定電子系統(tǒng)性能的關(guān)鍵設(shè)備,隨著通信、數(shù)字電視、衛(wèi)星定位、航空航天、雷達(dá)和電子對抗等技術(shù)的發(fā)展,對頻率合成器提出了越來越高的要求。頻率合成理論自20世紀(jì)30年代提出以來,已取得了迅速

2017-11-02 10:49:36 4

4 無線電系統(tǒng)會因?yàn)楦鞣N各樣的原因而采用基于鎖相環(huán)(PLL)技術(shù)的頻率合成器。PLL 的好處包括: (1)易于集成到 IC 中。 (2)無線信道間隔中的靈活性。 (3)可獲得高性能。 (4)頻率合成器

2017-11-16 15:28:13 15

15 頻率合成器主要有直接式、鎖相式、直接數(shù)字式和混合式4種。目前,鎖相式和數(shù)字式容易實(shí)現(xiàn)系列化、小型化、模塊化和工程化,性能也越來越好,已逐步成為最為典型和廣泛的應(yīng)用頻率合成器[1]。本文主要采用集成鎖相環(huán)PLLphase-Lockde Loop芯片CD4046,運(yùn)用FPGA來實(shí)現(xiàn)PLL頻率合成器。

2019-01-07 09:52:00 3077

3077

PLL頻率合成器和ADIsimFrequencyPlanner

2019-07-01 06:12:00 3764

3764 幾乎每個RF和微波系統(tǒng)都需要頻率合成器。頻率合成器產(chǎn)生本振信號以驅(qū)動混頻器、調(diào)制器、解調(diào)器及其他許多RF和。頻率合成器常被視為系統(tǒng)的心跳,創(chuàng)建方法之一是使用鎖相環(huán)(PLL)頻率合成器。傳統(tǒng)

2020-10-15 10:43:00 8

8 利用頻率合成器,你可以產(chǎn)生單一參考頻率的各種不同倍數(shù)的輸出頻率。其主要應(yīng)用是為RF信號 的上變頻和下變頻產(chǎn)生本振(LO)信號。頻率合成器在鎖相環(huán)(PLL)中工作,其中鑒頻鑒相器(PFD)將反饋頻率

2020-10-12 10:43:00 0

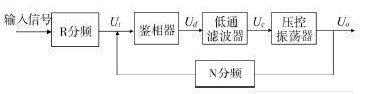

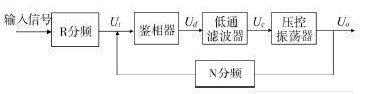

0 PLL 頻率合成器基本構(gòu)建模塊 PLL 頻率合成器可以從多個基本構(gòu)建模塊的角度來考察。我們在前面已經(jīng)提到過這個問題,下面將更加詳細(xì)地進(jìn)行探討:鑒頻鑒相器(PFD) 參考計(jì)數(shù)器(R) 反饋計(jì)數(shù)器

2020-12-03 01:47:00 21

21 UG-092: ADF4001 PLL頻率合成器評估板

2021-03-19 12:32:51 5

5 UG-167:針對ADF4153小數(shù)N分頻PLL頻率合成器的評估板

2021-03-19 12:42:52 11

11 UG-164:針對PLL頻率合成器的1750 MHz評估板用戶指南

2021-03-19 12:49:22 4

4 UG-158: 7.5 GHz PLL頻率合成器評估板

2021-03-20 09:48:41 2

2 UG-161:PLL頻率合成器評估板

2021-03-20 09:54:34 6

6 UG-160: 整數(shù)N分頻PLL頻率合成器評估板

2021-03-20 10:17:59 6

6 ADF4155:整數(shù)N/小數(shù)N分頻PLL頻率合成器

2021-03-20 17:01:57 11

11 AN-873: ADF4xxx系列PLL頻率合成器的鎖定檢測

2021-03-21 09:34:20 6

6 ADF41020:18 GHz微波PLL頻率合成器

2021-03-21 10:16:11 10

10 ADF4107:PLL頻率合成器數(shù)據(jù)表

2021-04-14 09:44:36 8

8 ADF4212L:雙低功耗PLL頻率合成器數(shù)據(jù)表

2021-04-22 19:18:02 5

5 ADF4216/ADF4217/ADF4218:雙射頻PLL頻率合成器550 MHz/1.2/2.0/2.5 GHz數(shù)據(jù)表

2021-04-23 13:36:06 5

5 ADF4196:低相位噪聲、快速建立、6 GHz PLL頻率合成器數(shù)據(jù)表

2021-04-23 17:13:01 1

1 ADF4206/ADF4208:雙射頻PLL頻率合成器數(shù)據(jù)表

2021-04-26 08:11:58 7

7 ADF4193:低相位噪聲、快速建立PLL頻率合成器數(shù)據(jù)表

2021-04-27 21:07:31 3

3 ADF4106:PLL頻率合成器數(shù)據(jù)表

2021-04-29 08:52:36 12

12 ADF4108:PLL頻率合成器數(shù)據(jù)表

2021-05-19 18:23:27 13

13 圖1所示電路使用帶集成式VCO和外部PLL的ADF4350頻率合成器,通過隔離PLL頻率合成器電路與VCO電路將雜散輸出降至最低。集成PLL和VCO的器件可從數(shù)字PLL電路饋通至VCO,由于PLL

2021-05-28 17:50:57 7

7 圖1所示電路框圖是一個低相位噪聲轉(zhuǎn)換環(huán)路頻率合成器(也稱為偏移環(huán)路)。此電路將ADF4002 鎖相環(huán) (PLL) 的較低100 MHz參考頻率轉(zhuǎn)換到5.0 GHz至5.4 GHz的較高頻率范圍

2021-05-29 08:17:44 20

20 ADF4107 PLL頻率合成器數(shù)據(jù)表

2021-06-18 10:01:57 7

7 pll頻率合成器工作原理與pll頻率合成器的原理圖解釋 我們要搞清楚pll頻率合成器工作原理與pll頻率合成器的原理圖就要先搞清楚pll和頻率合成器的概念。 頻率合成器:將一個高穩(wěn)定度和高精度的標(biāo)準(zhǔn)

2023-02-24 18:19:52 8275

8275

MAX2902 ISM發(fā)送器設(shè)計(jì)用于與外部頻率合成器IC組合,形成完整的TX路徑方案。根據(jù)系統(tǒng)要求,可以使用小數(shù)N分頻或整數(shù)N分頻頻率合成器IC。了解兩種頻率合成器的通道步長、相位噪聲和PLL鎖定時間有何不同,對于確定哪種頻率合成器更適合特定應(yīng)用是必要的。本說明將嘗試說明主要差異,以便正確選擇合成器。

2023-03-03 15:22:43 429

429

鎖相環(huán)頻率合成器的優(yōu)缺點(diǎn)? 鎖相環(huán)頻率合成器,又稱為PLL(Phase Locked Loop),是一種廣泛應(yīng)用的電路,能夠?qū)⑤斎胄盘柕?b class="flag-6" style="color: red">頻率合成為電路所需要的頻率,并且能夠?qū)崿F(xiàn)對信號的相位和頻率

2023-09-02 14:59:33 1216

1216 如何調(diào)試鎖相環(huán)頻率合成器?? 鎖相環(huán)頻率合成器(PLL)是電路中常見的一個模塊,用于生成穩(wěn)定的高精度頻率信號。PLL的核心部分是相位檢測器和環(huán)路濾波器,其主要工作原理是通過不斷調(diào)整反饋回來的參考信號

2023-09-02 15:06:37 504

504 時鐘發(fā)生器/PLL頻率合成器SOP-82~15V2MHz封裝:SOP-8

2022-08-19 15:57:46 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評論