電子發燒友網站提供《構建LED二進制計數器.zip》資料免費下載

2023-06-12 09:54:30 0

0 N進制計數器的實現 一、用集成計數器可以實現任意進制的計數器二、集成計數器控制功能的歸類三、集成計數器的級聯擴展四、復位法組成任意進制加法計數器五、置位法組成任意進制加法計數器六

2008-07-05 13:41:26

8位同步二進制遞減計數器-74HC40103

2023-03-03 19:49:59 0

0 7級二進制紋波計數器-74HC4024

2023-02-21 18:29:48 0

0 7級二進制紋波計數器-74HC4024_Q100

2023-02-21 18:29:31 0

0 可預置同步BCD十進制計數器;異步復位-74HC160

2023-02-20 20:05:50 4

4 雙4位同步二進制計數器-74HC_HCT4520

2023-02-17 19:22:25 1

1 雙 4 位二進制紋波計數器-74LV393

2023-02-16 21:08:21 0

0 12級二進制紋波計數器-74HC_HCT4040

2023-02-16 20:14:26 2

2 14級二進制紋波計數器-74HC_HCT4020

2023-02-15 19:40:50 1

1 雙十進制紋波計數器-74HC_HCT390

2023-02-15 19:06:31 0

0 雙 4 位二進制紋波計數器-74HC_HCT393

2023-02-15 18:58:50 0

0 14級二進制計數器-HEF4020B

2023-02-15 18:42:12 0

0 14級二進制計數器-HEF4020B_Q100

2023-02-15 18:41:58 0

0 12級二進制紋波計數器-HEF4040B

2023-02-15 18:40:14 0

0 12級二進制紋波計數器-HEF4040B_Q100

2023-02-15 18:40:02 1

1 雙二進制計數器-HEF4520B

2023-02-10 18:34:09 0

0 雙二進制計數器-HEF4520B_Q100

2023-02-10 18:33:54 0

0 本方案是一個基于 FPGA ?的十進制計數器。共陽極 7 段顯示器上的 0 到 9 十進制計數器,硬件在 Xilinx Spartan 6 FPGA 板上實現。

2022-12-20 14:52:25 2

2 構建一個4位二進制計數器,計數范圍從0到15(包括0和15),計數周期為16。同步復位輸入時,將計數器重置為0。

2022-12-02 09:20:28 1762

1762 電子發燒友網站提供《FPGA上的十六進制計數器.zip》資料免費下載

2022-11-23 10:47:06 7

7 二進制編碼的十進制是一個串行數字計數器,可計數十位數字,它會為每個新的時鐘輸入重置。由于它可以通過10種獨特的輸出組合,因此也被稱為“十進制(BCD)計數器”。十進制計數器可以計數0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11018

11018

將二進制數視為元胞自動機可能有助于數字二進制計數器的設計和實現嗎?

2022-07-28 11:47:10 840

840

CD4017 十進制計數器的應用實驗

2022-05-11 16:58:25 47

47 計數器(Counter)由基本的計數單元和控制門所組成,是在數字系統中對脈沖的個數進行計數,以實現測量、計數和控制功能,且兼有分頻功能的儀器。計數器按進位制不同,分為二進制計數器和十進制計數器;按

2021-11-25 18:06:07 32

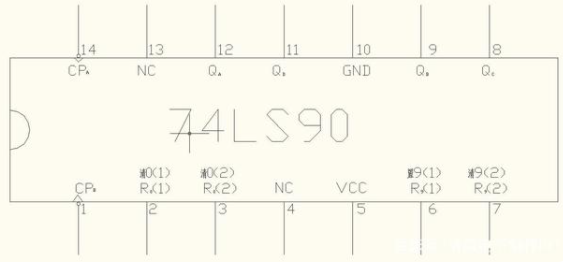

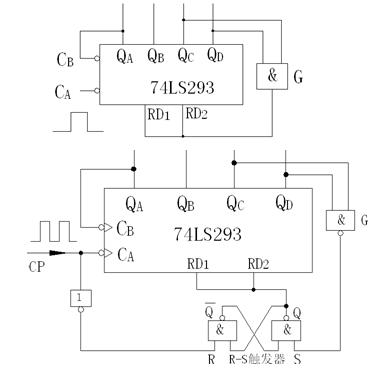

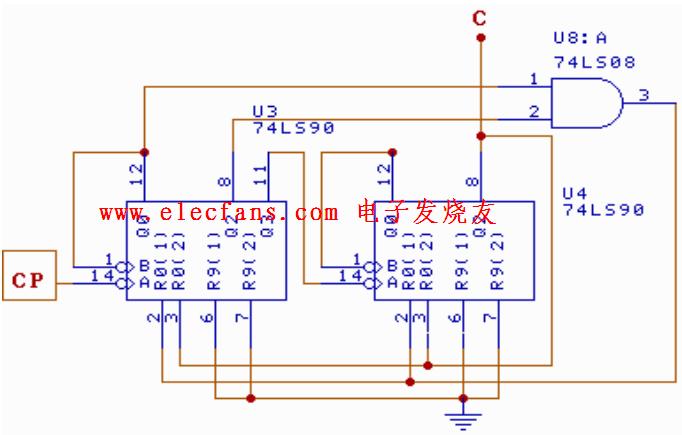

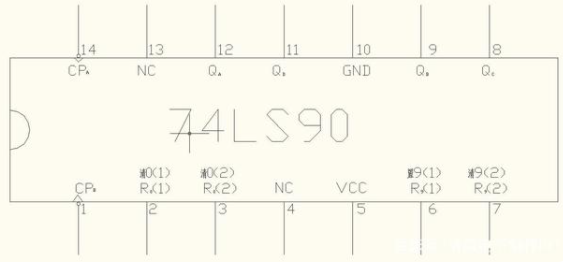

32 其中CPa和Qa構成1位二進制計數器,CPb和Qd、Qc、Qb 組成五進制計數器,將兩個計數器有關端子適當組合,可以組成其他類型的計數器。R0(1)、R0(2)為兩個清0端,R9(1)、 R9(2)為兩 個置9端。

2021-06-21 09:39:44 34099

34099

聲。除此之外,整個秒表還需有一個啟動信號和一個歸零信號,以便秒表能隨意停止及啟動。秒表的邏輯結構較簡單,它主要由顯示譯碼器、分頻器、十進制計數器、六進制計數器。四個10進制計數器:用來分別對百分之一秒、十分之一秒、秒和分

2020-07-14 17:09:21 13

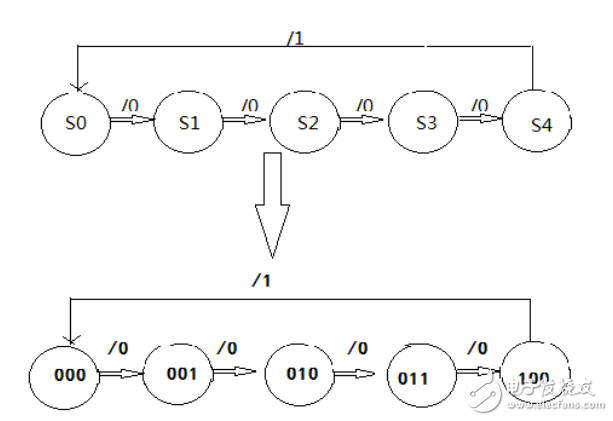

13 本文檔的主要內容詳細介紹的是同步7進制計數器的設計資料免費下載。

2020-05-20 08:00:00 11

11 十進制計數器是人們最常用的計數器,但在某些特殊的計數場合下,也需要其他進制的計數器。

2020-01-14 09:46:48 6705

6705

本文檔的主要內容詳細介紹的是如何使用Multisim仿真一個60進制的計數器的詳細資料免費下載

2018-10-23 11:37:56 126

126 關鍵詞:TTL , 分頻器 , 計數器 , 十進制 如圖所示為由TTL十進制計數器構成的分頻電路。在許多情況下。需要對脈沖序列進行N(N為整數)分頻。例如,數字鐘需要進行60分頻,得到重復頻率為

2018-10-03 18:46:02 2650

2650 本文首先介紹了計數器種類與應用,其次介紹了74LS160并行置零法設計24進制計數器電路圖,最后介紹了74ls162設計24進制計數器原理電路圖。

2018-05-08 11:46:43 54648

54648 由題目及其要求分析可知,首先要使用74LS192或40192設計一個4進制計數器和一個7進制計數器,然后通過數碼管來顯示狀態。兩種進制間的切換可以通過一個單刀雙擲開關來實現。其重點和難點在于設計一個4進制計數器和一個7進制計數器。

2018-01-31 16:18:13 54591

54591

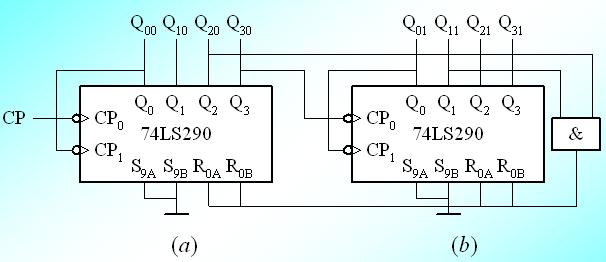

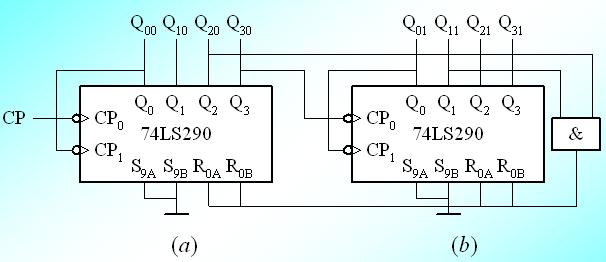

74ls290是一個二,五,十進制計數器,本文為大家介紹由74ls290構成的各種進制計數器的電路。

2018-01-26 09:26:11 106188

106188

74LS290為異步二-五-十進制加法計數器。本文為大家介紹74ls290構成31進制計數器電路。

2018-01-25 14:36:39 16924

16924

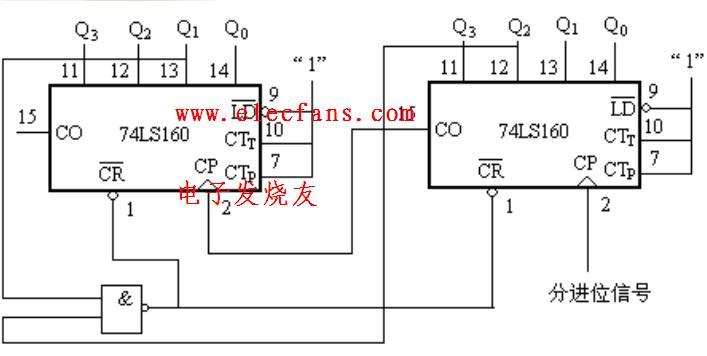

本文主要介紹了74ls160構成24進制計數器電路設計。本設計采用異步清零。由兩片十進制同步加法計數器74LS160和一片與非門74LS00以及相應的電阻開關組成。由外加送來的計數脈沖送入兩個計數器

2018-01-18 15:43:05 145644

145644

本文主要介紹了74ls160十進制計數器電路的設計與實現。74LS160是二~十進制同步可預置計數器,1腳Cr為清零端,低電平有效.2腳CP為時鐘脈沖輸人端,上升沿觸發.3~6V腳D1一D4為數據

2018-01-18 15:14:45 182091

182091

本文主要介紹了74LS161集成計數器電路(2、3、4、6、8、10、60進制計數器)。74LS161是4位二進制同步計數器,該計數器能同步并行預置數據,具有清零置數,計數和保持功能,具有進位輸出端

2018-01-18 10:56:39 324594

324594

本文為大家帶來三種5進制計數器設計方案。

2018-01-17 15:51:48 56298

56298

使用兩片74LS161芯片級聯的形式來構成六十進制計數器,一片控制個位,為十進制;另一片控制十位,為六進制。

2018-01-17 13:58:47 52599

52599

計數器由基本的計數單元和一些控制門所組成,計數單元則由一系列具有存儲信息功能的各類觸發器構成。計數器在數字系統中應用廣泛,如在電子計算機的控制器中對指令地址進行計數。本文為大家帶來六種10進制計數器設計方案。

2018-01-17 08:58:24 64843

64843

74ls161為二進制同步計數器,具有同步預置數、異步清零以及保持等功能。兩片74ls161可設計一個24進制計數器。

2018-01-16 15:30:46 110315

110315

60進制計數器,由于24進制、60進制計數器均由集成計數器級聯構成,且都包含有基本的十進制計數器,從設計簡便考慮,芯片選擇同步十進制計數器

2017-12-22 13:55:48 148134

148134

計數器是一個用以實現計數功能的時序部件,本設計主要設備是兩個74LS160同步十進制計數器,并且由200HZ,5V電源供給。作高位芯片與作低芯片位之間級聯。

2017-12-21 17:23:51 224996

224996

針對任意進制(N進制)計數器的設計目的,采用反饋復零法對基于同步十進制計數器7415160進行設計,分別采用異步清零法實現了6進制計數器和同步置數法實現7進制計數器的設計,通過應用EWB軟件對所設

2017-12-21 17:08:37 60783

60783

本文為大家介紹基于74LS192的任意進制計數器的設計。

2017-12-21 12:00:28 92329

92329

二進制加計數器

2017-11-24 14:31:30 6

6 集成計數器常見的是多位二進制計數器及十進制計數器,當需要實現其它進制計數器時,通常利用現有的集成計數器進行適當的連接而構成。對于當設計要求沒有限定計數器的狀態編碼時電路設計的靈活性問題已有文獻進行

2017-11-09 16:36:16 81

81 基于VHDL的EDA實驗---3位二進制計數器

2017-11-08 17:45:53 1

1 約翰遜MC14017B是五級十進制計數器內置代碼轉換器。 高速運行和約翰遜spike-free輸出是通過使用十進制計數器的設計。 十個解碼輸出通常是低,只在適當的十進制時間走高。 輸出的正向變化的時鐘脈沖。 這部分可用于分頻應用程序以及十進制計數器或十進制譯碼顯示應用程序。

2017-04-06 09:03:48 28

28 實驗目的:

1、熟悉計數器、譯碼器和顯示器的使用方法。

2、提高綜合實踐的技能。

3.設計十進制,并用譯碼器和顯示器,顯示計數結果。

2016-10-11 17:41:59 37

37 提出一種基于Proteus 軟件的任意進制計數器的設計。以74LS163 集成計數器為基礎,用置數法設計了兩種48 進制計數器,采用Proteus 軟件對計數器進行仿真。結果表明,Proteus 軟件具有實現48 進制計數器的功能。仿真圖像清晰,能快速準確地驗證設計結果。

2016-07-29 18:53:03 24

24 集成計數器實現N進制計數集成計數器實現N進制計數集成計數器實現N進制計數

2016-06-08 14:28:43 15

15 關于FPGA的資料,包括很多有用的東西,在EDA實驗4-10進制計數器。

2016-05-05 15:43:18 0

0 數字電子技術--中規模集成計數器及其應用--同步、異步二五十進制計數器-PPT

2016-03-22 14:33:06 1

1 計數器是常用的時序邏輯電路器件,文中介紹了以四位同步二進制集成計數器74LS161和異步二-五-十模值計數器74LS290為主要芯片,設計實現了任意模值計數器電路,并用Multisim軟件進行了

2013-07-26 11:38:41 133

133 計數器是一種重要的時序邏輯電路,廣泛應用于各類數字系統中。介紹以集成計數器74LS161和74LS160為基礎,用歸零法設計N進制計數器的原理與步驟。用此方法設計了3種36進制計數器,并

2012-03-20 10:21:38 95

95 計數器是數字邏輯系統中的基本部件,它是數字系統中用得最多的時序邏輯電路,本文主要闡述了用中規模集成計數器設計任意進制同步加法計數器的設計思想,并對設計方法和步驟作

2012-02-28 11:41:43 6157

6157

異步計數器電路是指其構成的基本功能單元觸發器的時鐘輸入信號不是與觸發器在一起的,有的是外輸入的脈沖信號,有的是其他觸發器的輸出。本文給出了N進制 異步計數器 設計方案

2011-10-24 15:39:38 3245

3245

介紹了集成4位二進制計數器 74LS161 異步置零法構成任意進制計數器的 Multisim 仿真方案,即以波形方式顯示計數器的計數過程、過渡狀態形成異步置零信號的過程,用四蹤示波器以面板

2011-08-05 14:25:22 330

330 采用可編程器件設計電路,利用MAX+plus II設計軟件中LPM元件庫所提供的lpm_counter元件,實現任意進制計數器的設計。該計數器電路與結構無關,可編程器件的芯片利用率及效率達到最

2010-12-29 17:47:07 55

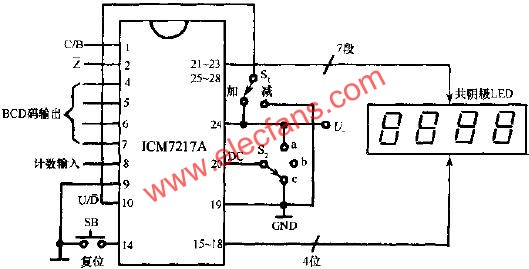

55 使用一片ICM7217A配4只共陰極LED數碼管,可構成4位十進制可逆計數器,其

2010-12-10 13:55:24 6871

6871

C186是任意進制串行計數器,所謂任意進制,即在進行計數或分頻時,不需外加門電路,依靠本身管腳引出線的

2010-10-19 16:09:24 1361

1361

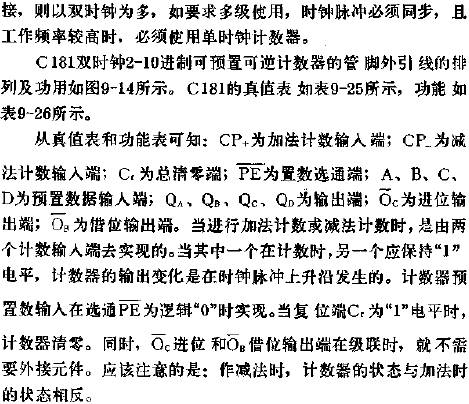

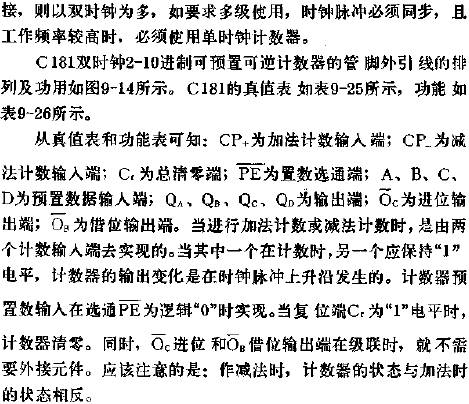

C181是雙時鐘2-10進制可預置可逆計數器.所謂雙時鐘是指計數器的加法計數時鐘和減法計數時鐘各有它自身的輸入

2010-10-19 15:16:06 814

814

十進制計數器,十進制計數器原理是什么?

二進制計數器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數,特

2010-03-08 13:19:54 23684

23684 什么是二進制計數器,二進制計數器原理是什么?

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數,還可以實現

2010-03-08 13:16:34 29984

29984 環形計數器和扭環形計數器

移位寄存器也可以構成計數器,稱為移位型計數器。它有兩種結構:環形計數器和扭環形計數器。

2010-01-12 14:07:46 8704

8704 利用預置端構成的模六計數器

2010-01-12 13:55:38 1128

1128

100進制加減計數器的設計與制作:本電路結構如圖袁主要由晶體振蕩電路,分頻電路,控制電路,計數電路,譯碼電路,數碼管顯示等幾部分構成。

2009-10-22 21:50:19 228

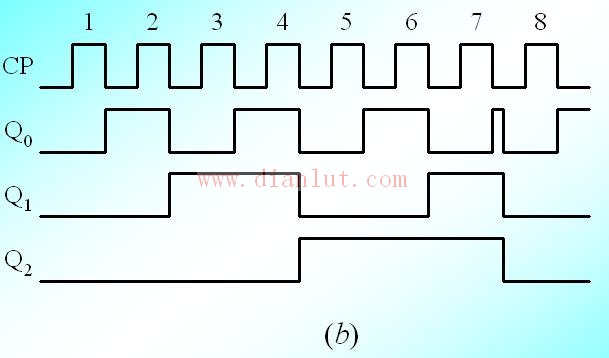

228 同步二進制計數器

1. 同步與異步二進制加法計數器比較態序表和工作波形一樣電路結構不同: 異步二進制加法

2009-09-30 18:37:29 10744

10744

異步二進制計數器

1. 電路構成與工作原理

2009-09-30 18:33:25 13201

13201

異步十進制遞增計數器

2009-09-24 11:12:05 1095

1095

8421碼同步十進制遞增計數器

2009-09-24 11:09:34 5844

5844

12位二進制計數器

2009-09-16 15:56:08 5906

5906

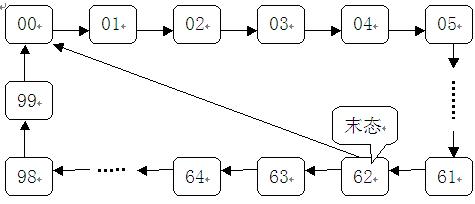

64進制計數器

64進制計數器由兩個

2009-09-16 15:54:01 3909

3909

24進制計數器電路

在百進制基礎上,采用反饋歸零法即可組成二十四進制計數器。計數范圍為0~23,24為過渡狀態,當高位計數至2、低位計數至4

2009-09-16 15:50:29 19522

19522

百進制計數器電路

將兩塊74LS290進行級聯,組成的百進制計數器如圖12.8所示。

2009-09-16 15:47:50 5541

5541

74LS290組成七進制計數器?

解 首先,將74LS290的CP1端與Q0端相接,使

2009-09-16 15:46:35 8926

8926

TTL 二進制同步可逆計數器

2009-08-03 09:05:53 26

26 100進制計數器一、 實驗目的:1、 熟悉MAX+PLUS環境的基本操作。2、 掌握VHDL和原理圖的設計輸入方式。3、 設計100進制計數器。二、&

2009-06-28 00:07:21 7414

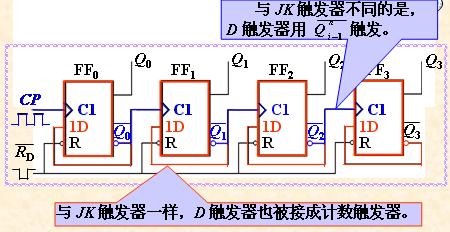

7414 第二十五講 同步計數器

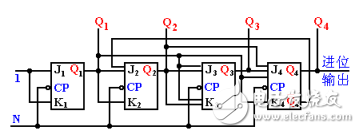

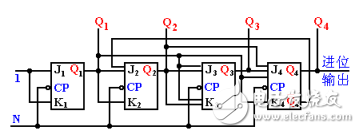

7.3.2 同步計數器一、同步二進制計數器1.同步二進制加法計數器JK觸發器組成的4位同步二進制加法

2009-03-30 16:28:45 7879

7879

兩片4位二進制數加法計數器74LS161級聯成五十進制計數器。

2009-03-28 10:10:23 33045

33045

100進制計數器

異步級聯法組成的100進制計數器

定義集成計數器的高低位,1#芯片為低位(相當

2008-07-05 14:25:17 5412

5412

我們可以采用具有保持功能的同步集成計數器(如74LS160)組成同步計數器,電路如圖3-4所示。在160計數器中當S1=S2

2008-07-05 14:17:49 4236

4236

先級聯后預置數構成的63進制計數器:我們同樣也可以先用級聯法組成10i計數器、或16i計數器,再用預置

2008-07-05 13:58:00 1405

1405

用16進制計數器先級聯后預置數構成的63

2008-07-05 13:54:55 2733

2733

45進制計數器,芯片有:

2008-06-30 00:14:21 4068

4068

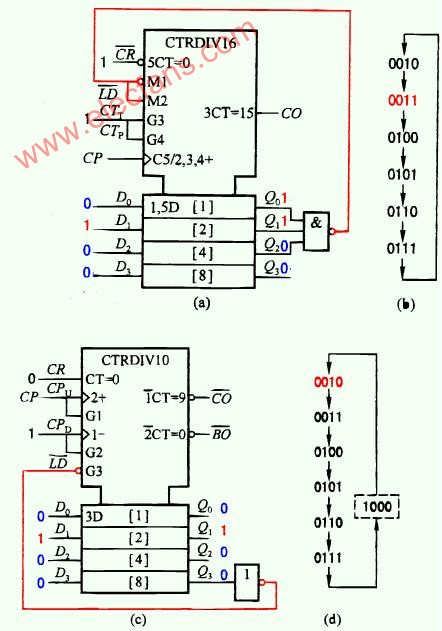

計數器級聯時的時鐘構成方式可以采用同步時鐘,也可以采用異

2008-06-30 00:03:32 11061

11061

60進制計數器,由于24進制、60進制計數器均由集成計數器級聯構成,且都包含有基本的

2008-06-30 00:00:41 15300

15300

十進制計數器工作原理

同二進制計數器相比,十進制計數器較為復雜。分析步驟一般是:

2008-01-21 13:15:22 27668

27668

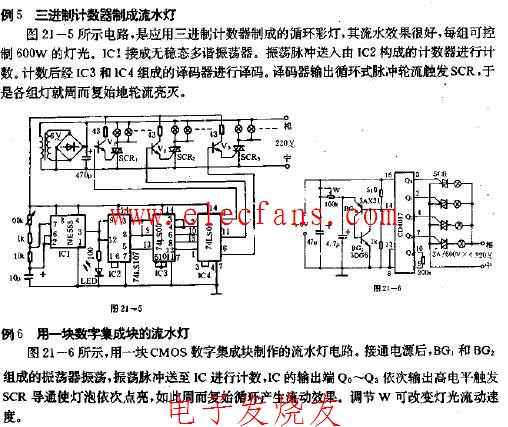

三進制計數器制成流水燈是應用三進制計數器制成的循環彩燈,其流水效果很好,每組可控制600W的燈光,IC1接成無穩態多諧振蕩器。

2007-12-26 19:27:57 2273

2273

計數器的級連使用

一個十進制計數器只能顯示0~9十個數,為了擴大計數器范圍,常用多個十進制計數器級連使用。

2007-11-22 12:53:25 3143

3143

十進制計數器

二進制計數器具有電路結構簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數,特別是當二進制數的位數較多時,閱讀非常困難,還

2007-06-20 13:46:05 3559

3559

電子發燒友App

電子發燒友App

硬聲App

硬聲App

2

2 11018

11018

32

32 34099

34099

13

13 2650

2650 54648

54648 54591

54591

106188

106188

145644

145644

182091

182091

324594

324594

52599

52599

64843

64843

110315

110315

148134

148134

224996

224996

60783

60783

81

81 28

28 37

37 24

24 133

133 95

95 6157

6157

3245

3245

330

330 55

55 814

814

23684

23684 29984

29984 228

228 19522

19522

7414

7414 3559

3559

評論