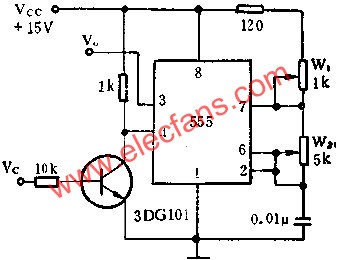

可變占空因數的脈沖發生器

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>信號處理電子電路圖>可變占空因數的脈沖發生器

相關推薦

201

201 681

681 322

322 570

570

1547

1547

1

1 3026

3026 324

324

3084

3084 24

24 12907

12907

10902

10902 32242

32242

19858

19858

4639

4639

52

52 3023

3023

評論