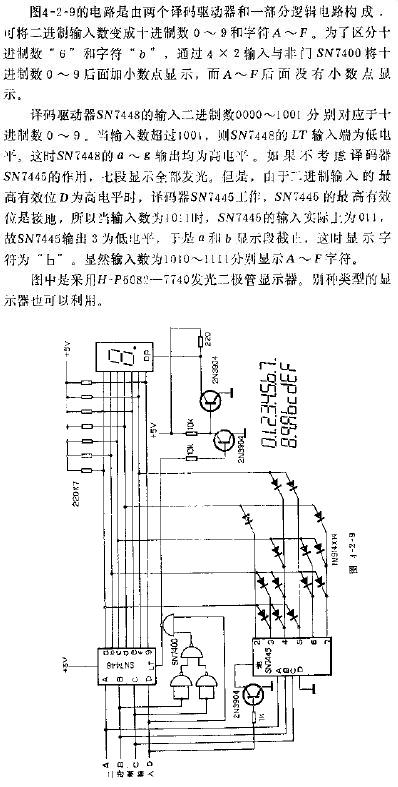

十六種字符譯碼器

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>信號處理電子電路圖>十六種字符譯碼器

相關推薦

684

684

2201

2201

1061

1061

1023

1023

9

9 97073

97073

35527

35527

104354

104354

76265

76265

31418

31418

3676

3676

6

6 15

15 0

0 68

68 37

37 1677

1677

23437

23437 20

20 15826

15826

37

37

評論