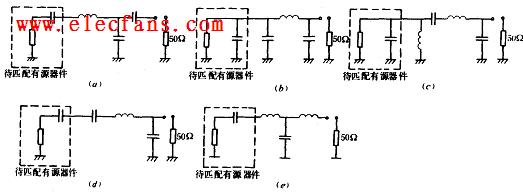

分立元件組成的阻抗匹配電路

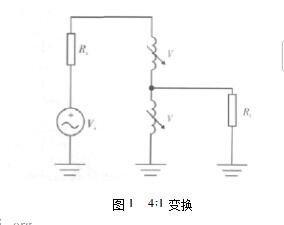

為了找到一種合適的阻抗匹配電路,筆者對幾種阻抗匹配電路進行了調試和比較,其中分別包括分立器件和集成芯片所構成的電路。

應用分立器件的原因是其價格低廉,為此筆者設計了源極輸出器,它的特點是輸入電阻高,而電壓放大倍數(shù)小于且接近于1。

通過實驗觀察發(fā)現(xiàn):分立元器組成的源極輸出器除具上述優(yōu)點外,同時也存在著以下幾點不足:

(1)該源極輸出器輸出的波形很小。

(2)靜態(tài)工作難以設置,致使信號負半周期不能完全輸出。

(3)由于極間電容和導線的電容影響而導致頻帶變窄。

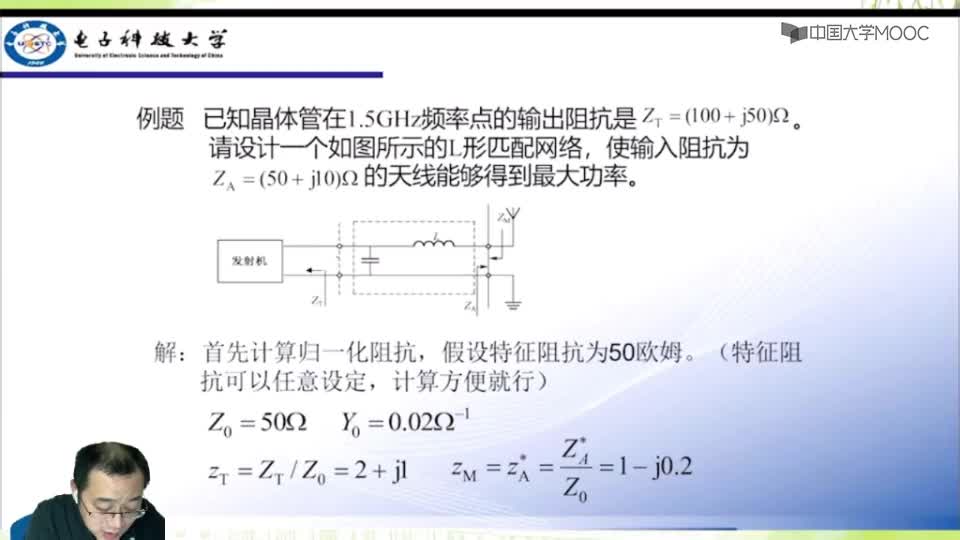

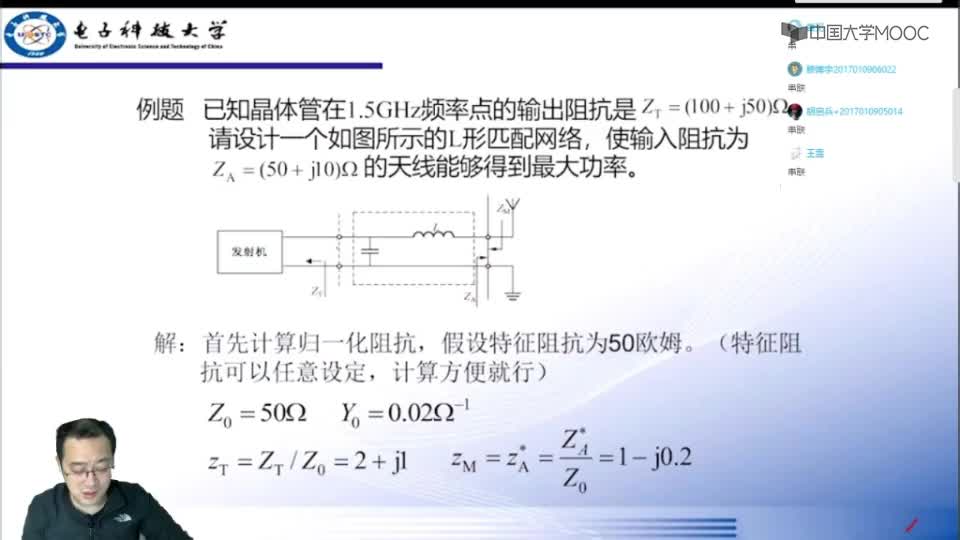

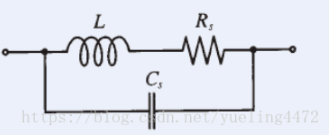

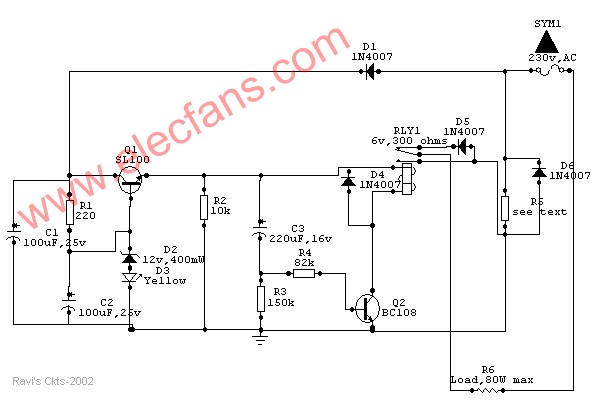

鑒于上述缺點,筆者設計了如圖3所示的偏移電路,該電路采用孿生FET以降低零漂。由于采用恒流源作源極負載,因而增益更趨近于1,且直流工作狀態(tài)極為穩(wěn)定。

但是通過實驗發(fā)現(xiàn),該電路還有以下缺點:

(1)找兩個N溝道結型場效應管特性十分對稱的管子不太容易。

(2)由于極間電容和導線電容的影響,加之源負載的各極間存在的固有電容,致使帶寬變窄。

傳統(tǒng)的模擬示波器的阻抗匹配電路一般均采取上述兩種方式,也可以在源極跟器后設置射極跟隨器或用差分放大等方式來解決上述缺點,但所需用的器件太多,結構復雜。

電子發(fā)燒友App

電子發(fā)燒友App

評論