一站式PCBA智造廠家今天為大家講講pcb設(shè)計(jì)布線解決信號串擾的方法有哪些?PCB設(shè)計(jì)布線解決信號串擾的方法。信號之間由于電磁場的相互而產(chǎn)生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可

2023-10-19 09:51:44 219

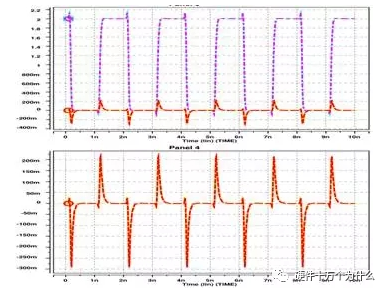

219 現(xiàn)一系列問題,如串擾、反射波、時鐘抖動等。為了確保高速信號傳輸?shù)姆€(wěn)定和可靠性,需要進(jìn)行仿真串擾。本文將詳細(xì)介紹高速信號仿真的串擾以及為什么需要進(jìn)行仿真。 對于高速信號來說,串擾是一種令人頭疼的問題。串擾是指高速信

2023-09-05 15:42:31 249

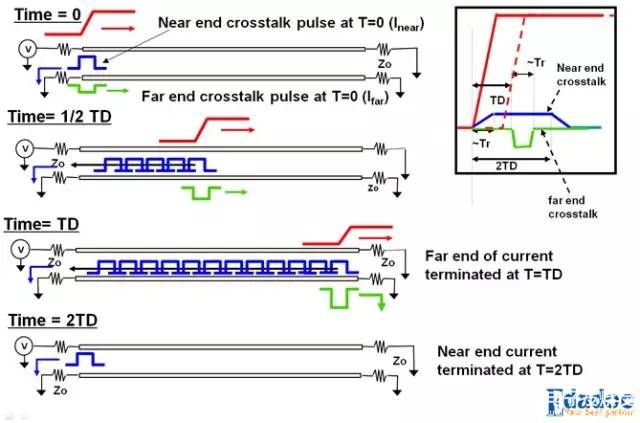

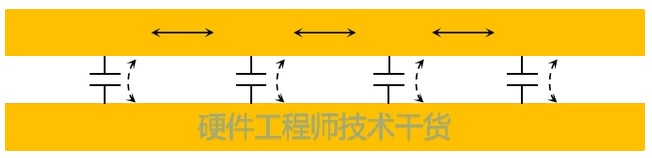

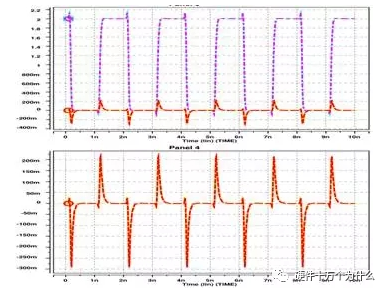

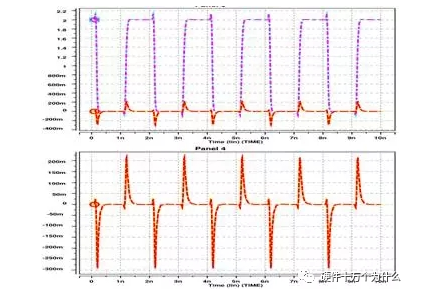

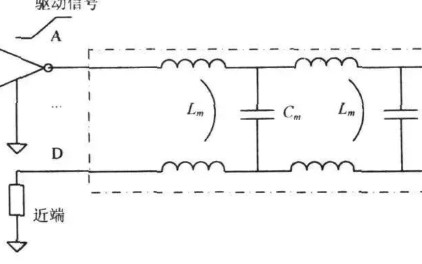

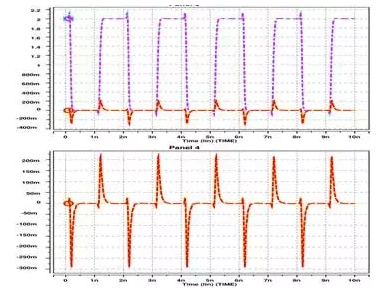

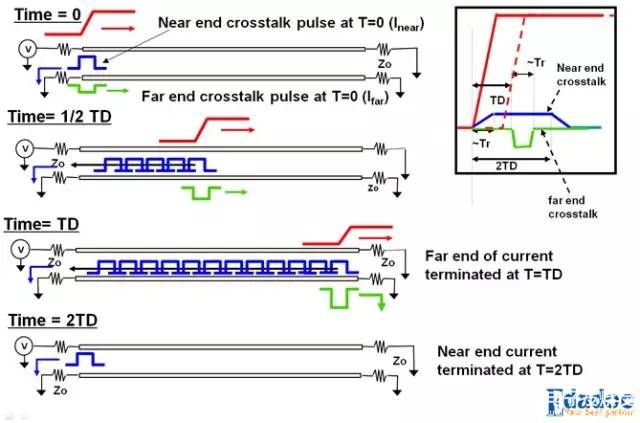

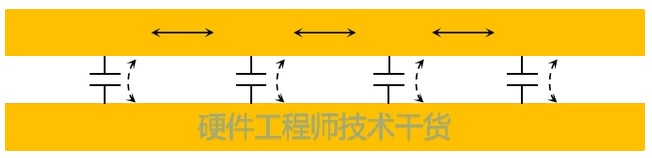

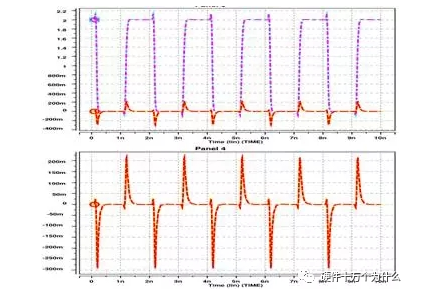

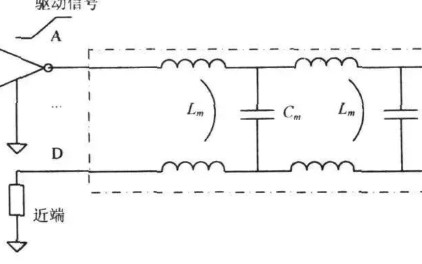

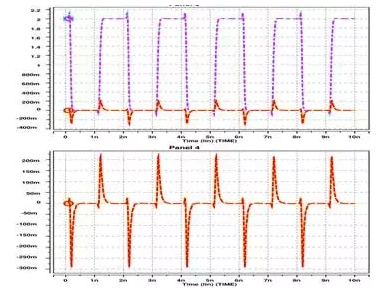

249 空間中耦合的電磁場可以提取為無數(shù)耦合電容和耦合電感的集合,其中由耦合電容產(chǎn)生的串擾信號在受害網(wǎng)絡(luò)上可以分成前向串?dāng)_和反向串擾Sc,這個兩個信號極性相同;由耦合電感產(chǎn)生的串擾信號也分成前向串?dāng)_和反向串擾SL,這兩個信號極性相反。

2023-08-21 14:26:46 140

140 小的成本,快的時間使產(chǎn)品達(dá)到波形完整性、時序完整性、電源完整性的要求;我們知道:電源不穩(wěn)定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產(chǎn)生畸變,

2023-08-17 09:29:30 1263

1263

當(dāng)信號通過電纜發(fā)送時,它們面臨兩個主要的通信影響因素:EMI和串擾。EMI和串擾嚴(yán)重影響信噪比。通過容易產(chǎn)生EMI 和串擾的電纜發(fā)送關(guān)鍵數(shù)據(jù)是有風(fēng)險的。下面,讓我們來看看這兩個問題。

2023-07-06 10:07:03 592

592 串擾 :即兩條信號線之間的耦合引起的線上噪聲干擾。

2023-07-06 09:15:48 392

392

串擾是一種信號干擾現(xiàn)象,表現(xiàn)為一根信號線上有信號通過時,由于兩個相鄰導(dǎo)體之間所形成的互感和互容,導(dǎo)致在印制電路板上與之相鄰線的信號線就會感應(yīng)相關(guān)的信號,稱之為串擾。

2023-07-03 15:45:10 595

595

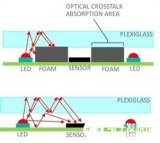

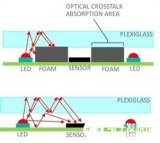

當(dāng) LED、傳感器安裝在玻璃后面時,這種光學(xué)串擾會變得更加嚴(yán)重。光學(xué)串擾會大大降低手勢檢測范圍。 從 LED 到傳感器可以有幾條路徑產(chǎn)生串擾。這些路徑包括:直接路徑、反射路徑和玻璃蓋片的光反射路徑。直接路徑和反射路徑產(chǎn)生的串擾很容易緩解,在LED 和傳感器之間放置一

2023-06-09 18:15:02 217

217

通常以斷斷續(xù)續(xù)或不易重現(xiàn)的方式發(fā)生,對于工程師來說, 盡早解決 PCB 上串擾發(fā)生的所有原因非常重要。 串擾會對時鐘信號、周期和控制信號、數(shù)據(jù)傳輸線和 I/O 產(chǎn)生不良影響。通常來講, 串擾是無法完全消除的,只能盡量減少串擾。 02 . 串擾的機(jī)制 ? 1、耦合

2023-05-23 09:25:59 1079

1079

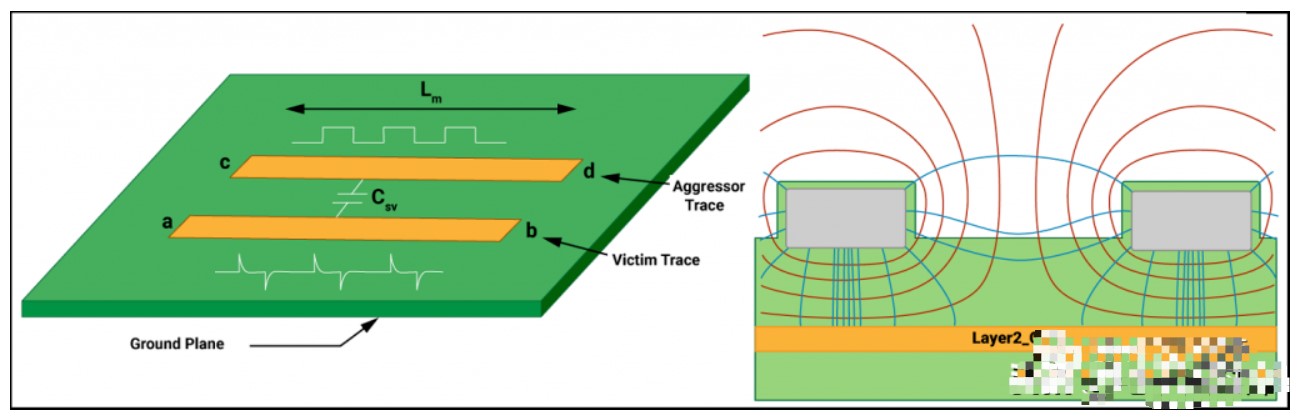

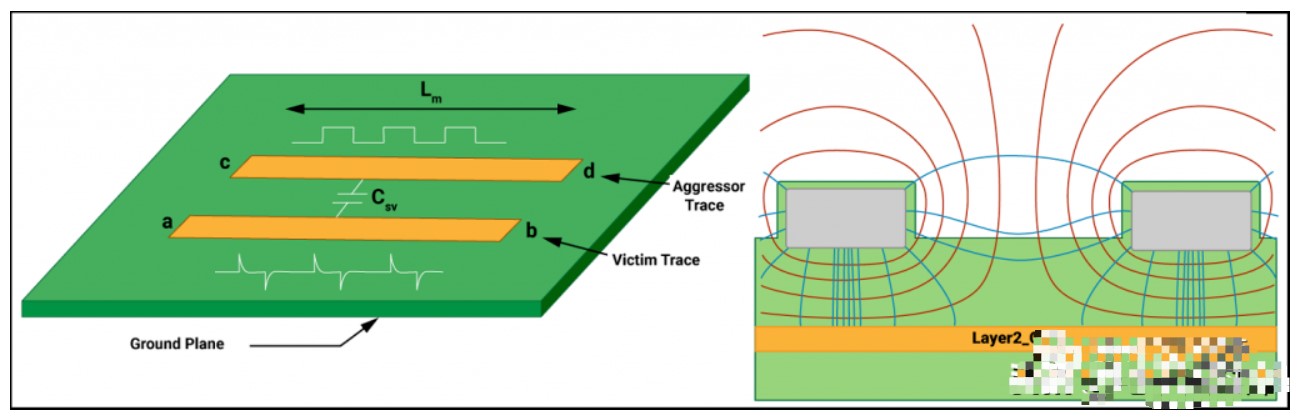

串擾是指有害信號從一個網(wǎng)絡(luò)轉(zhuǎn)移到相鄰網(wǎng)絡(luò)。任何一對網(wǎng)絡(luò)之間都存在串擾。通常把噪聲源所在網(wǎng)絡(luò)稱為動態(tài)網(wǎng)絡(luò)或攻擊網(wǎng)絡(luò)。把受影響的網(wǎng)絡(luò)稱為靜態(tài)網(wǎng)絡(luò)或者受害網(wǎng)絡(luò)。

2023-05-06 11:48:08 672

672

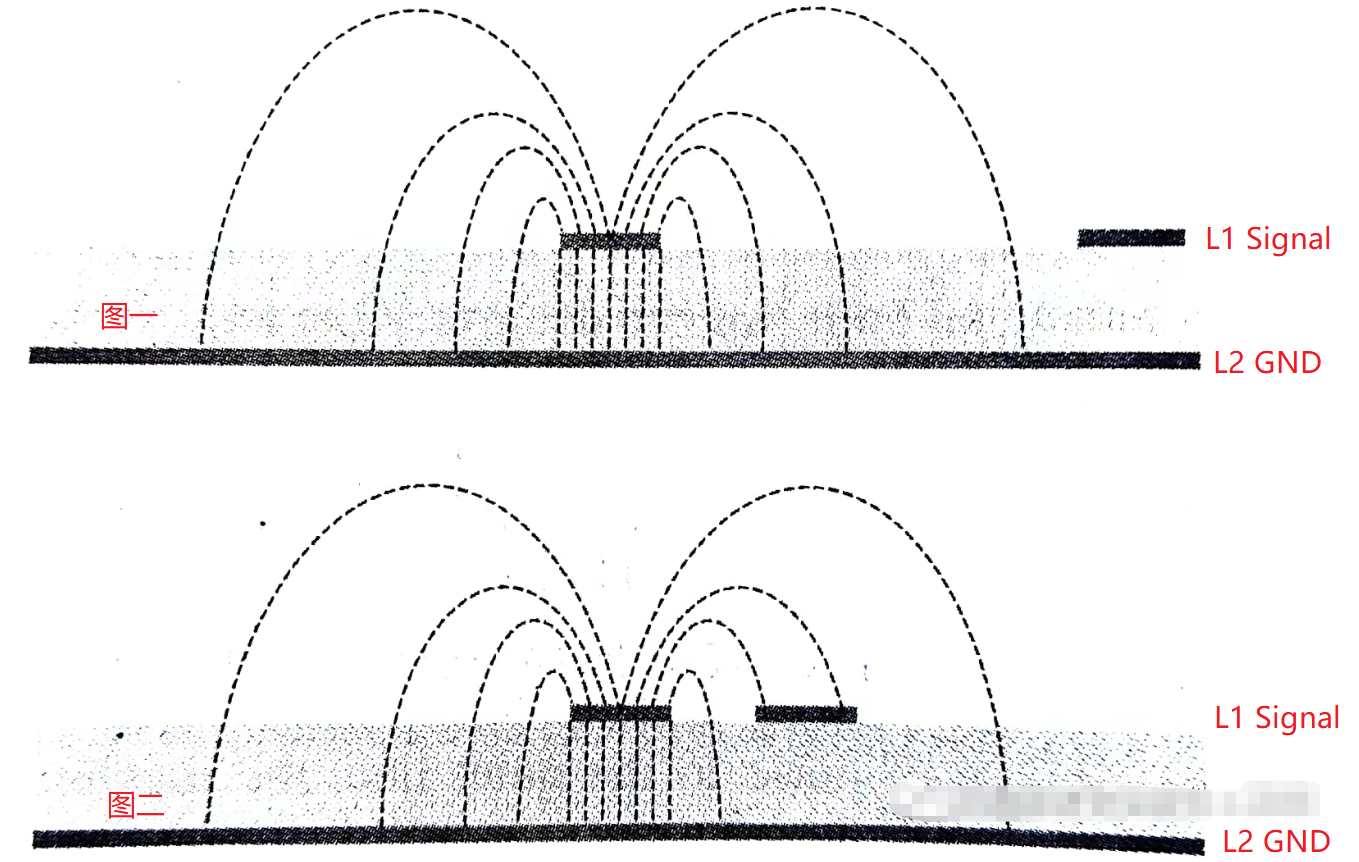

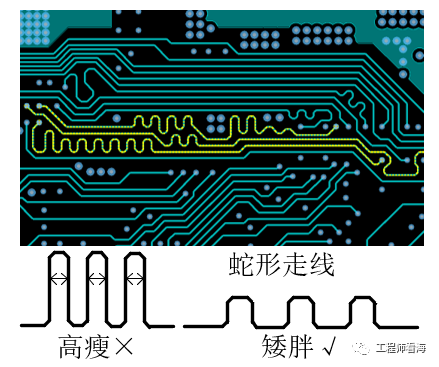

我們經(jīng)常聽說PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾,這就是3W原則,信號線之間的干擾被稱為串擾,串擾是怎么形成的呢?

2023-04-18 11:06:22 787

787

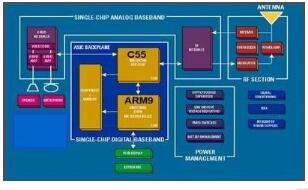

信號完整性仿真重點(diǎn)分析有關(guān)高速信號的3個主要問題:信號質(zhì)量、串擾和時序。對于信號質(zhì)量,目標(biāo)是獲取具有明確的邊緣,且沒有過度過沖和下沖的信號。

2023-04-03 10:40:07 553

553 高速電路信號完整性分析與設(shè)計(jì)—串擾串擾是由電磁耦合引起的,布線距離過近,導(dǎo)致彼此的電磁場相互影響串擾只發(fā)生在電磁場變換的情況下(信號的上升沿與下降沿)[此貼子已經(jīng)被作者于2009-9-12 10:32:03編輯過]

2009-09-12 10:31:08

定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質(zhì)量。差的信號完整性不是由某一單一因素導(dǎo)致的,而是板級設(shè)計(jì)中多種因素共同 引起的。當(dāng)電路中信號能以要求的時序、持續(xù)時間和電壓幅度到達(dá)接收端時,該電路就有很好的信號完整性。當(dāng)信號不能正常響應(yīng)時,就出現(xiàn)了信號完整性問題。

2023-03-02 09:41:06 852

852

C語言中存在這樣一種類型,名叫不完整類型(Incomplete types),雖然我們可能不太理解,或許也沒有仔細(xì)研究過,但是在實(shí)際的編程中,我們卻已經(jīng)用到過很多次了。

2023-02-21 10:03:00 556

556 ____tz_zs 對于 ChatGPT 回答不完整的情況(篇幅限制,沒有說完),可以輸入“繼續(xù)”指令,讓其繼續(xù)回答下去,獲得完整內(nèi)容。 如下圖,發(fā)問 “使用web3js 調(diào)用 eth鏈智能合約” 直到這里才是獲得了剛剛問題 “使用web3js 調(diào)用 eth鏈智能合約” 的完整回答。

2023-02-10 10:48:03 0

0 信號完整性分析的目的就是用最小的成本,最快的時間使產(chǎn)品達(dá)到波形完 整性、時序完整性、電源完整性的要求。

2023-02-03 11:25:55 464

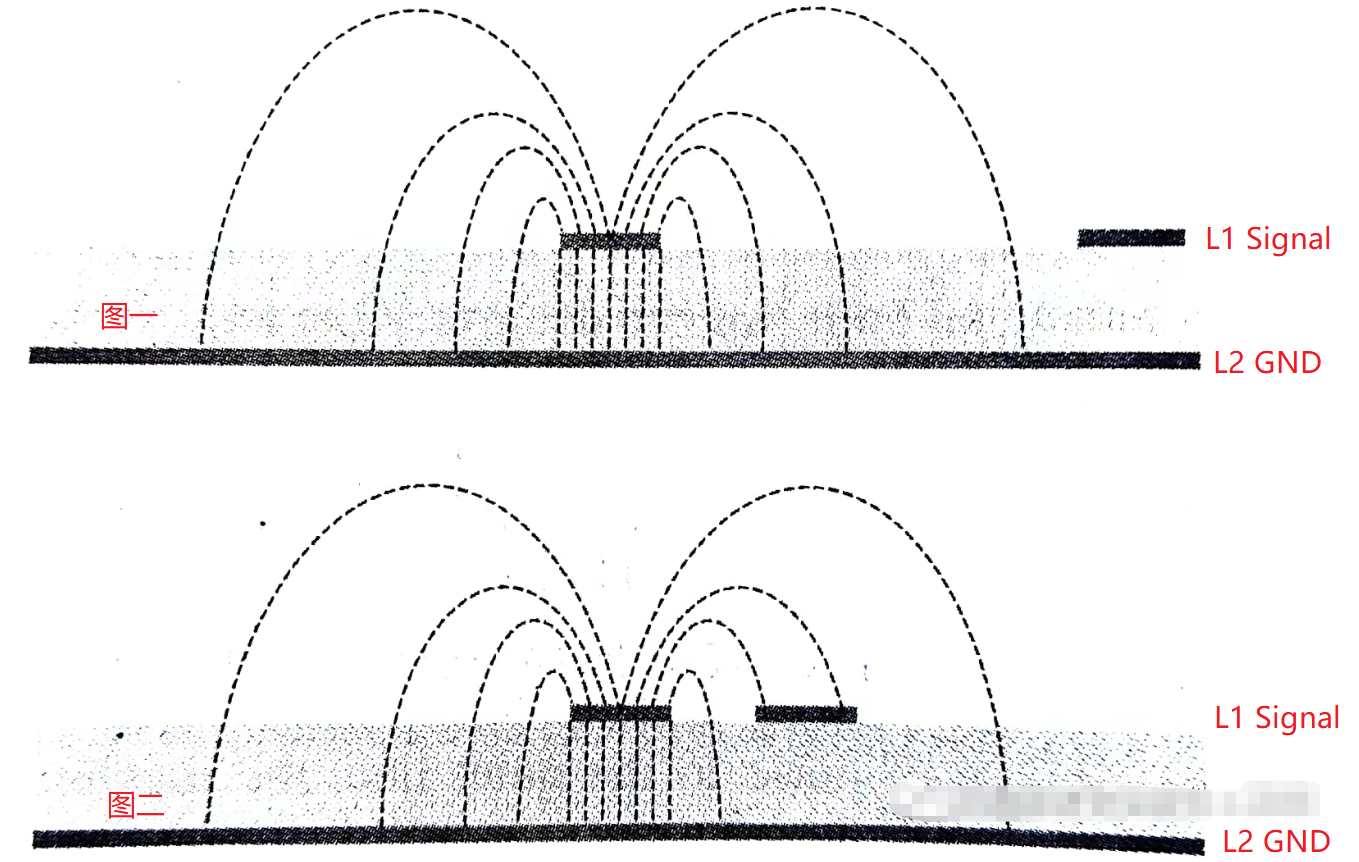

464 關(guān)于兩個公式,我們不需要去記住,我們只需要知道它告訴了我們什么:攻擊信號的幅值影響著串擾的大小;減小串擾的途徑就是減小信號之間的耦合,增加信號與其回流平面之間的耦合。

2023-01-24 16:28:00 1494

1494

本章我們接著介紹信號完整性基礎(chǔ)第三章節(jié)串擾剩余知識。

2023-01-16 09:58:36 1371

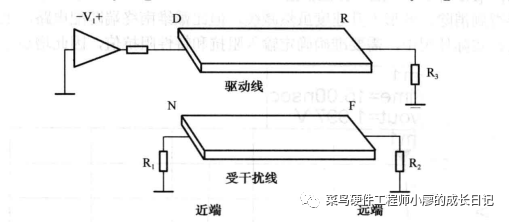

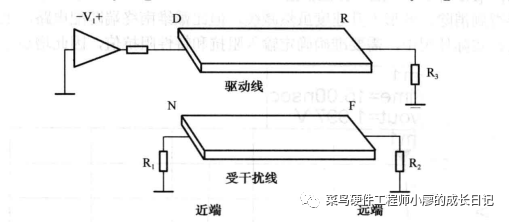

1371 當(dāng)信號在一走線上傳輸時,一部分能量會通過電場容性耦合和磁場感性耦合到相鄰走線上,從而引起串擾噪聲,并以耦合后產(chǎn)生串擾噪聲方向的不同區(qū)分為近端串擾(VNEXT)和遠(yuǎn)端串擾(VFEXT)。

2023-01-09 14:05:52 426

426 不完整類型(Incomplete types)是缺少足夠信息來確定該類型對象大小的對象類型,不完整類型可以在翻譯單元的某些點(diǎn)完整。

2022-12-16 09:52:07 272

272 先來說一下什么是串擾,串擾就是PCB上兩條走線,在互不接觸的情況下,一方干擾另一方,或者相互干擾。主要表現(xiàn)是波形有異常雜波,影響信號完整性(Signal integrity, SI)等等。一般情況下可以分為容性串擾和感性串擾兩種。

2022-11-10 17:00:44 1137

1137

APM32F091RCT6_SPI_從機(jī)接收數(shù)據(jù)不完整

2022-11-09 21:04:03 0

0 在實(shí)際的應(yīng)用場景中,會遇到多種信號完整性問題,典型問題有如下幾種:反射、串擾,電源/地噪,時序等。其中,發(fā)射和串擾是引起信號完整性問題的兩大主要原因。

2022-10-09 10:56:55 2497

2497 通常說的信號完整性就是指信號無失真的進(jìn)行傳輸。前面我們討論很多信號完整性問題,包括時序、串擾、衰減、反射、電源完整性、EMC等等。

2022-09-29 17:00:06 880

880 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。PCB板層的參數(shù)、信號線間距、驅(qū)動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。串擾也可以理解為感應(yīng)噪聲。

2022-09-14 09:49:55 1684

1684

我們知道:電源不穩(wěn)定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產(chǎn)生畸變,看下面這張圖,你就會知道理想的信號,經(jīng)過:反射、串擾、抖動,最后變成什么鬼。

2022-08-24 11:22:17 499

499 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。PCB板層的參數(shù)、信號線間距、驅(qū)動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

2022-08-15 09:32:06 5670

5670 信號完整性測量已成為開發(fā)數(shù)字系統(tǒng)過程中的關(guān)鍵步驟。信號完整性問題,如串擾、信號衰減、接地反彈等,在傳輸線效應(yīng)也很關(guān)鍵的較高頻率下會增加。

2022-07-25 09:59:58 6400

6400

串擾的危害:

降低板內(nèi)信號完整性

時鐘或者信號延遲

產(chǎn)生過沖電壓和突變電流

造成芯片邏輯功能紊亂

2022-07-07 10:35:01 810

810 本文首先介紹了傳輸線理論,詳細(xì)分析了高速PCB設(shè)計(jì)中的信號完整性問題,包括反射、串擾、同步開關(guān)噪聲等,然后利用Mentor Graphics公司的EDA軟件HyperLynx對給定電路模型進(jìn)行了反射

2022-07-01 10:53:00 3

3 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。PCB板層的參數(shù)、信號線間距、驅(qū)動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

2022-02-21 11:35:30 1779

1779

高速電路信號完整性分析與設(shè)計(jì)—串擾

2022-02-10 17:23:04 11

11 stm32串口DMA數(shù)據(jù)接收不完整問題說明最近做了一個項(xiàng)目需要用串口來接收模塊端的應(yīng)答數(shù)據(jù),由于使用了實(shí)時操作系統(tǒng),考慮中斷嵌套或被打斷的問題導(dǎo)致數(shù)據(jù)接收不完整的問題,使用串口dma接收數(shù)據(jù),但

2021-12-24 19:37:57 17

17 介紹了高速PCB設(shè)計(jì)中的信號完整性概念以及破壞信號完整性的原因,從理論和計(jì)算的層面上分析了高速電路設(shè)計(jì)中反射和串擾的形成原因,并介紹了IBIS仿真。

2021-12-17 13:47:07 1

1 臺積電公司CEO張忠謀近日表示:美國半導(dǎo)體供應(yīng)鏈目前并不不完整,在美國建新廠的成本將比中國大陸高出37%至50%。目前臺積電正在美國亞利桑那州廠建廠。

2021-10-28 10:37:15 1575

1575 說這段話時總會覺得很別扭,“我堂堂信號完整性怎么能是區(qū)區(qū)反射就能說明的呢?”之后隨著理論與實(shí)踐的深入,越來越覺得“反射中有黃金屋,反射中有顏如玉”,be the signal,弄清楚反射與串擾就拿到了解開信號完整性謎題的兩

2021-04-13 09:46:29 2190

2190

文章——串擾溯源。 提到串擾,防不勝防,令人煩惱。不考慮串擾,仿真波形似乎一切正常,考慮了串擾,信號質(zhì)量可能就讓人不忍直視了,于是就出現(xiàn)了開頭那驚悚的一幕。下面就來說說串擾是怎么產(chǎn)生的。 所謂串擾,是指有害信號從一

2021-03-29 10:26:08 2663

2663 靜態(tài)網(wǎng)絡(luò)靠近干擾源一端的串擾稱為近端串擾(也稱后向串擾),而遠(yuǎn)離干擾源一端的串擾稱為遠(yuǎn)端串擾(或稱前向串?dāng)_)。

2021-01-24 16:13:00 6444

6444

? 串擾是通過近電場(電容耦合)和磁場(電感耦合)在相鄰導(dǎo)體之間耦合的噪聲。盡管任何相鄰導(dǎo)體都表現(xiàn)出串擾,但是當(dāng)它出現(xiàn)在強(qiáng)干擾信號和敏感信號之間時,對信號完整性將造成很大的影響。 串擾的再定

2020-12-25 15:12:29 1968

1968 串擾是信號完整性中最基本的現(xiàn)象之一,在板上走線密度很高時串擾的影響尤其嚴(yán)重。我們知道,線性無緣系統(tǒng)滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會疊加在受害線上的信號,從而使其信號產(chǎn)生畸變。

2020-11-12 10:39:00 2

2 本文主要介紹串擾的概念,及其FEXT、NEXT等,以及串擾的消除措施。 串擾串擾是指當(dāng)信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產(chǎn)生的不期望的電壓噪聲干擾。這種干擾是由于兩條信號線間的耦合,即

2020-10-19 17:54:49 5160

5160

Altium中的信號完整性分析包括檢查信號上升時間,下降時間,提供終端方案和進(jìn)行串擾分析的能力。您還可以定義模型并設(shè)置規(guī)則和約束以及信號完整性分析相關(guān)的其它設(shè)置。一旦確認(rèn)了串擾問題,就可以根據(jù)需要修改相同層或相鄰層的布線路徑。

2020-08-25 15:50:00 8673

8673

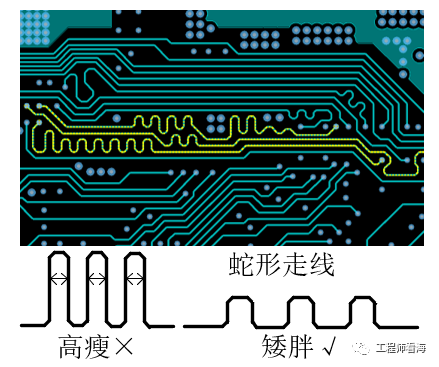

高速PCB設(shè)計(jì)中,信號之間由于電磁場的相互耦合而產(chǎn)生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可能引發(fā)電路誤動作從而導(dǎo)致系統(tǒng)無法正常工作,解決PCB串擾問題可以從以下幾個方面考慮。

2020-07-19 09:52:05 1991

1991 這個短暫的網(wǎng)絡(luò)研討會將指導(dǎo)您完成避免反射和串擾問題的方法在你的董事會設(shè)計(jì)pre-layout和布線后的設(shè)計(jì)階段。

2019-10-23 07:04:00 2870

2870 串擾是信號完整性中最基本的現(xiàn)象之一,在板上走線密度很高時串擾的影響尤其嚴(yán)重。我們知道,線性無緣系統(tǒng)滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會疊加在受害線上的信號,從而使其信號產(chǎn)生畸變。

2019-09-18 15:10:37 13741

13741

信號完整性的問題主要包括傳輸線效應(yīng),如反射、時延、振鈴、信號的過程與下沖以及信號之間的串擾等,涉及傳輸線上的信號質(zhì)量及信號定時的準(zhǔn)確性。

良好的信號質(zhì)量是確保穩(wěn)定時序的關(guān)鍵。由于反射和串擾造成

2019-06-24 15:27:25 1102

1102

出的AFT基本推導(dǎo)規(guī)則BRR的完備性.此外還對基于不完整AFT進(jìn)行拓?fù)浒l(fā)現(xiàn)的NP難問題進(jìn)行了討論,深入剖析了任意實(shí)際的局域網(wǎng)絡(luò)的不完整AFT通過BRR推導(dǎo)完成后的各種可能情況,并分析了單純依靠AFT進(jìn)行拓?fù)浒l(fā)現(xiàn)的局限性.該工作對于基于AFT進(jìn)

2018-01-12 16:28:03 0

0 本文通過介紹信號完整性理論,對串擾和反射的成因進(jìn)行探討。利用Cadence公司的軟件SpecctraQuest,以基于ARM11架構(gòu)的S3C6410為主處理器嵌入式系統(tǒng)為載體進(jìn)行信號完整性仿真分析

2017-12-01 17:16:01 963

963

引起的。主要的信號完整性問題包括反射、振鈴、地彈、串擾等。 源端與負(fù)載端阻抗不匹配會引起線上反射,負(fù)載將一部分電壓反射回源端。如果負(fù)載阻抗小于源阻抗,反射電壓為負(fù),反之,如果負(fù)載阻抗大于源阻抗,反射電壓為正。布線的幾何形狀、不正確的線端接、經(jīng)過連接器的傳輸及電源平面

2017-11-16 13:24:51 36

36 介紹信號完整性的四個方面,EMI,串擾,反射,電源等。

2016-08-29 15:02:03 26

26 串擾是不同傳輸線之間的能量耦合。當(dāng)不同結(jié)構(gòu)的電磁場相互作用時,就會發(fā)生串擾。在數(shù)字設(shè)計(jì)中,串擾現(xiàn)象是非常普遍的。串擾可能出現(xiàn)在芯片、PCB板、連接器、芯片封裝和連接器

2012-05-28 09:09:38 2368

2368 通過端接電路在抑制攻擊線上反射的同時,減小了受害線上信號的串擾,從而使信號在兩條耦合線上的傳輸質(zhì)量得到改善。最后進(jìn)行了多組數(shù)據(jù)的串擾比較研究,分析了串擾減小的原因。

2011-12-12 14:31:21 28

28 文章介紹了數(shù)字電路設(shè)計(jì)中的信號完整性問題, 探討了振鈴、邊沿畸變、反射、地彈、串擾和抖動等各種信號完整性問題的成因和抑制措施。針對常見的反射和串擾給出了較為詳細(xì)的分

2011-09-07 16:14:58 104

104 串擾是 高速電路板 設(shè)計(jì)中干擾信號完整性的主要噪聲之一;為有效地抑制串擾噪聲,保證系統(tǒng)設(shè)計(jì)的功能正確,有必要分析串擾問題。針對實(shí)際PCB中互連線拓?fù)浜?b style="color: red">串擾的特點(diǎn),構(gòu)

2011-06-22 15:58:54 31

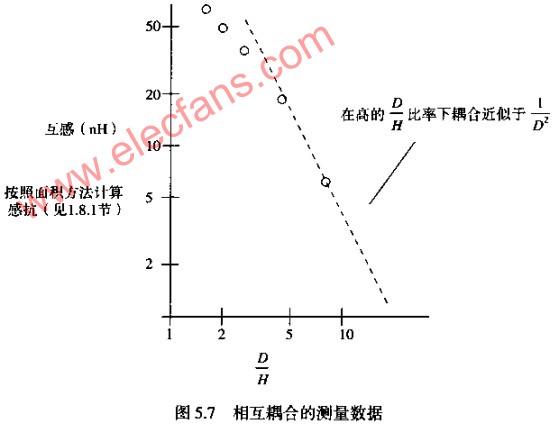

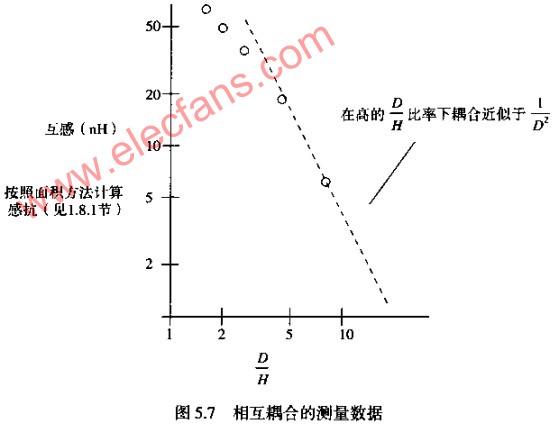

31 兩個導(dǎo)體之間的串擾取決于它們之間的互感和互容。通常在數(shù)字設(shè)計(jì)中,感性串擾相當(dāng)于或大于容性串擾,因此在這里開始我們主要討論感性耦合的機(jī)制。

2010-06-10 16:22:46 1426

1426

高速電路信號完整性分析與設(shè)計(jì)—串擾串擾是由電磁耦合引起的,布線距離過近,導(dǎo)致彼此的電磁場相互影響串擾只發(fā)生在電磁場變換的情況下(信號的上升沿與下降沿)

2009-10-06 11:10:15 115

115

電子發(fā)燒友App

電子發(fā)燒友App

評論