電路描述

VGA和現代ADC的功能已遠遠超越早期ADC設計所用的傳統運算放大器。在本例所用的VGA中,增益由外部控制。針對10位或12位轉換器映射的增益值可通過引腳選擇,低噪聲級的阻抗則可通過一個串聯R-C網絡調整,以獲得各種不同的阻抗值。借助簡單的引腳搭接便可使用高速轉換器產品。

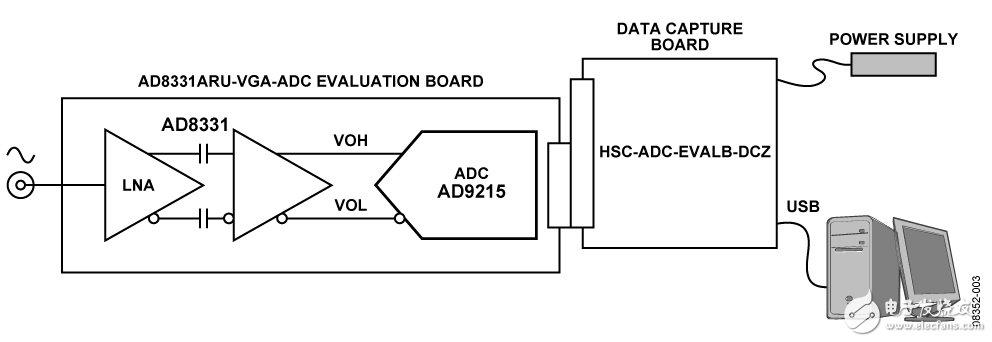

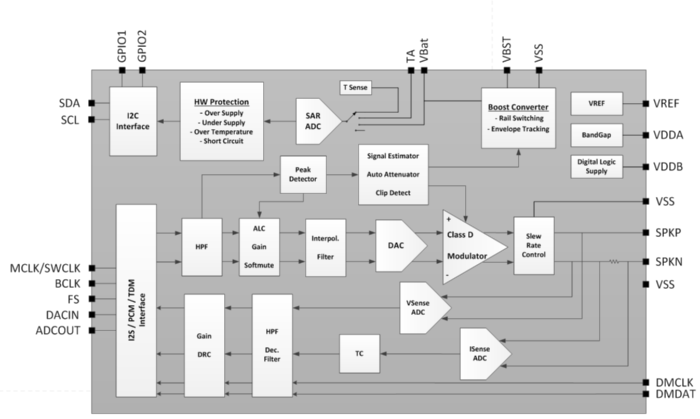

圖1所示電路展現了典型VGA與ADC的互連情況。對于本例,AD8331 VGA與AD9215 ADC在頻率范圍和差分接口匹配方面兼容。為簡明起見,圖中未顯示電源去耦。

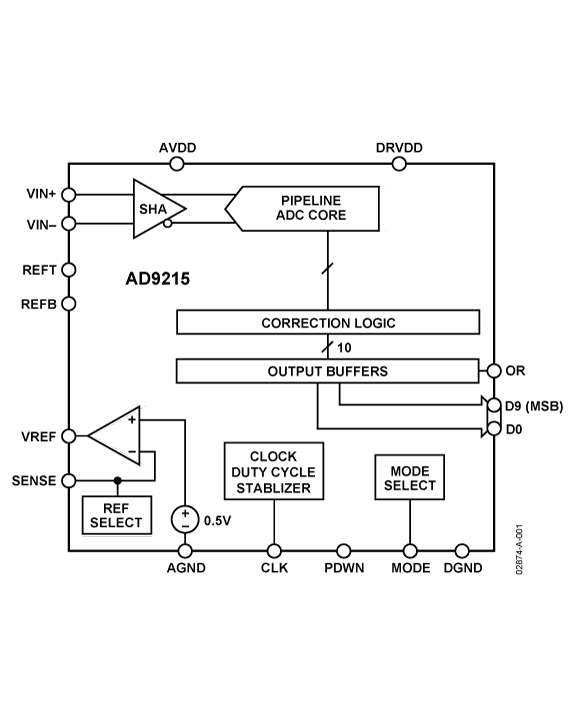

AD8331內置一個低噪聲前置放大器,后接一個差分衰減器和增益級。此VGA僅需5 V單電源供電。ADC的低噪聲3 V電源可由與5 V電源相連的LDO提供,例如ADP3339。該VGA的差分輸出用于驅動具有差分輸入的ADC,其輸入范圍為1 V峰峰值至約4.5 V峰峰值。AD9215的輸入范圍可以設置在1 V峰峰值差分與2 V峰峰值差分之間。對于本電路,ADC輸入范圍設置為2 V峰峰值差分。

與大多數單電源器件一樣,AD8331需要一個電壓為供電電壓中間值的內部基準電壓源,用于一對鏡像放大器,它可在輸出端(折合到共模電壓CMV)提供相等但極性相反的信號。關于此功能的更多信息,請參考AD8331數據手冊 。VGA的引腳11 (VCM)既可以作為輸入,也可以作為輸出。作為輸出時,VCM電路可以在引腳11上進行去耦,或者可以通過一個電壓源驅動該引腳,以修改共模電壓的值,從而適應具有不同輸入范圍的各種ADC。如果保持浮地,VCM電壓將為電源電壓的一半,這對于交流耦合應用是最佳值。

引腳12 (CLMP)將輸出擺幅箝位在ADC差分輸入的限制內,從而避免出現可能會嚴重影響轉換器的過驅問題。利用一個簡單的電阻控制箝位幅度。如果CLMP引腳上沒有任何連接,則箝位電壓為以2.5 V共模電壓為中心的差分4.5V峰峰值。

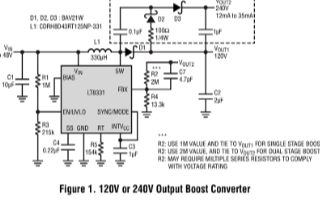

測試波形選擇1 MHz正弦波,利用 ADC Analyzer?軟件恢復的波形如圖2所示。采樣頻率為65 MSPS,對應于AD9215的65 MSPS版本。LNA輸入信號為70 mV峰峰值,經過外部低通和高通濾波器處理,可濾除信號發生器的雜散。VGA增益為29 dB,可將信號放大到大約ADC滿量程輸入電壓的一半。VGA與ADC之間的高通和低通濾波組合可衰減50 kHz以下的低頻噪聲(33 Ω和100 nF可產生48 kHz的低頻截止頻率),以及100 MHz以上的頻率(42 pF和33 Ω可產生114 MHz的高頻截止頻率)。

圖2:重建的滿量程2 V峰峰值1 MHz正弦波,采樣速率為65 MSPS

通過減小LNA輸入端以及LNA與VGA輸入端之間的串聯電容值,可以進一步實現高通濾波。

如果VOH和VOL上的PCB走線雜散電容約超過25 pF,則可能需要一個輸出去耦網絡,它由100 Ω固定電阻與AD8331各輸出端串聯插入的一個鐵氧體磁珠并聯組成。否則,便不需要這一網絡。

大部分現代ADC都可以通過引腳接入內部基準電壓源。AD9215的內部基準電壓為1 V,外部電阻使共模輸入電壓偏置3 V電源電壓的一半。

數據捕捉板與筆記本電腦接口。ADC Analyzer軟件可啟動轉換器,并提供波形或FFT顯示。關于AD9215配置的詳細信息,請參考AD9215數據手冊。

圖3是該測試設置的簡化框圖。評估板上裝有一個20引腳、雙排接頭,它與轉換器接口板上的連接器一半相結合。評估板由標準筆記本電腦上運行的ADC Analyzer軟件進行控制。

圖3:測試配置框圖

本電路必須構建在具有較大面積接地層的多層電路板上。為實現最佳性能,必須采用適當的布局、接地和去耦技術(請參考 教程MT-031——“實現數據轉換器的接地并解開AGND和DGND的謎團”,以及 教程MT-101 ——“去耦技術”)。

常見變化

其它單通道、10位ADC包括AD9214(適合較低輸入頻率)或AD9411(適合較高采樣速度應用)。

電子發燒友App

電子發燒友App

評論