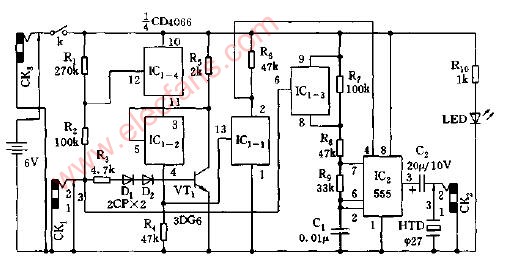

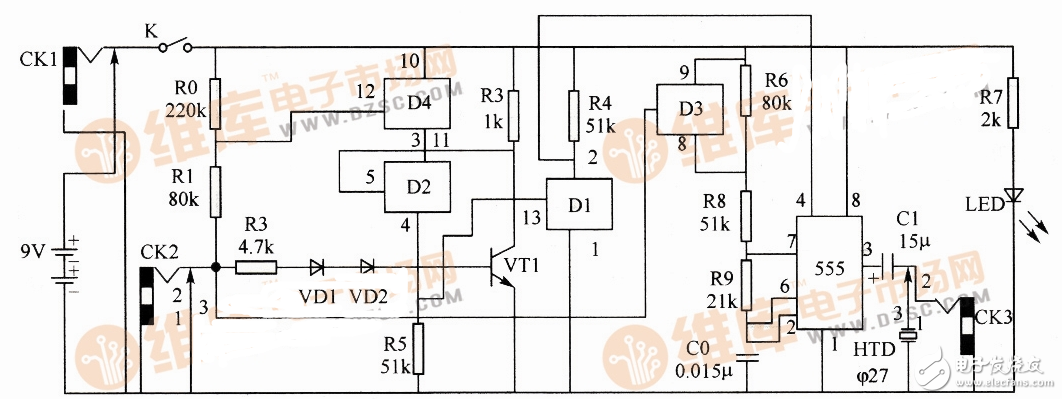

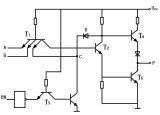

五用途三態聲頻邏輯比電路圖

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>電工儀表電路圖>五用途三態聲頻邏輯比電路圖

相關推薦

389

389 440

440 213

213

904

904 1828

1828

10760

10760 13

13 1593

1593

6304

6304 3339

3339 7465

7465 21629

21629 66152

66152 32926

32926 1172

1172 51792

51792

4838

4838

113066

113066

69342

69342

20313

20313

7000

7000 48

48 76

76 109

109 27

27 13

13 16

16 1685

1685 59

59 29

29 41856

41856

評論