?

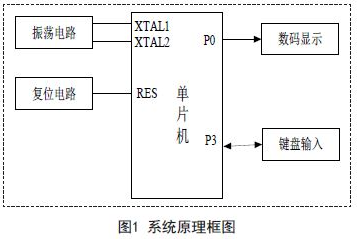

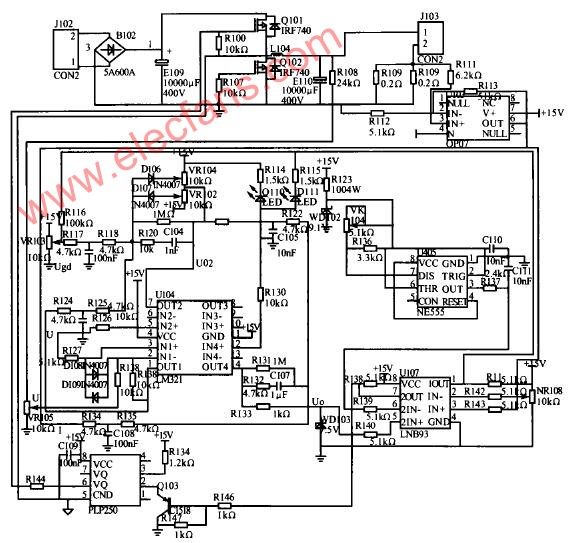

系統(tǒng)設(shè)計(jì)原理及電路圖

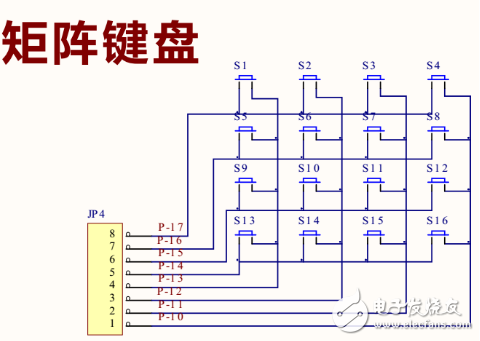

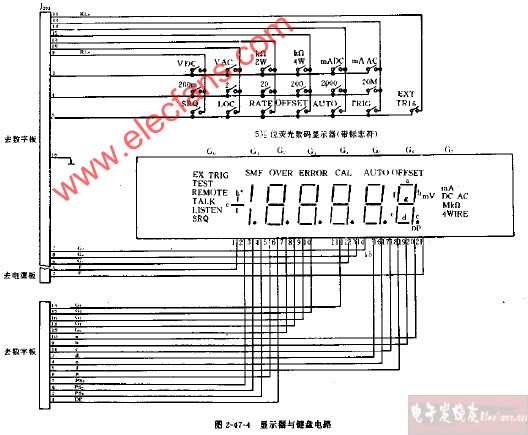

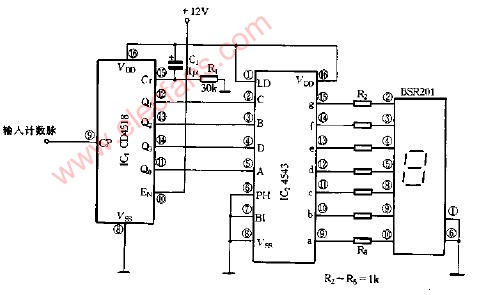

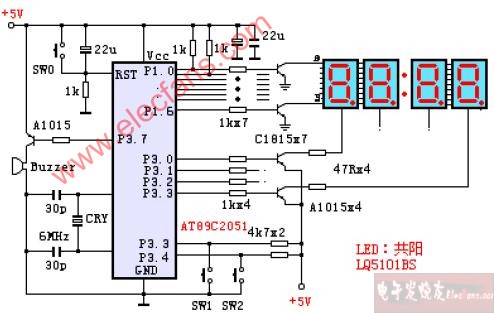

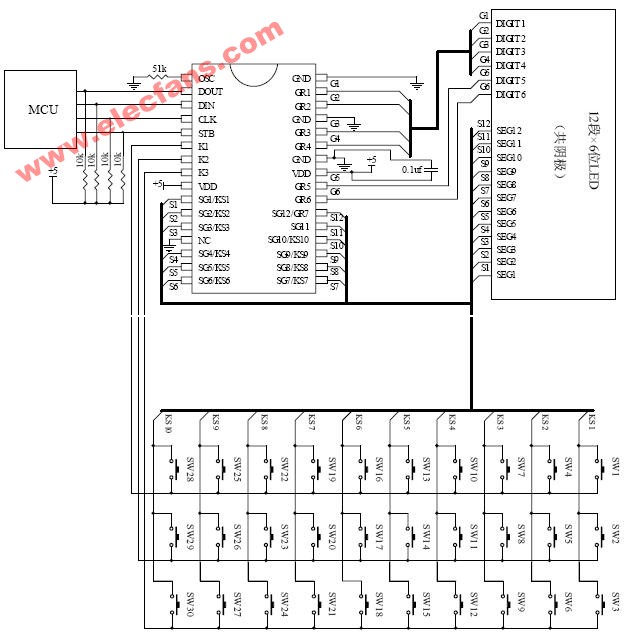

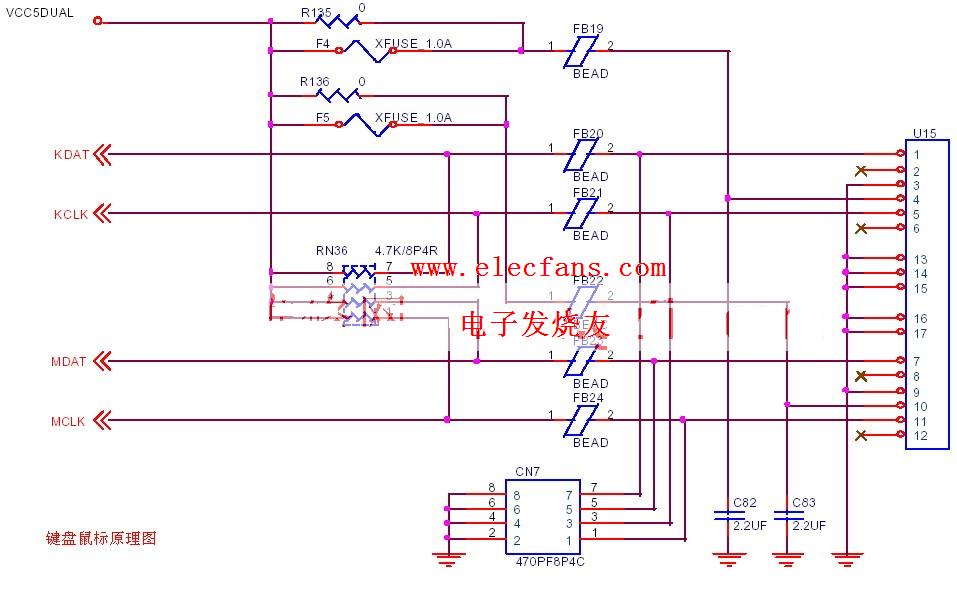

圖1為基于FPGA的預(yù)置數(shù)可控計(jì)數(shù)顯示頂層設(shè)計(jì)電路原理圖,共由3部分組成:鍵盤掃描控制電路key_board;BCD碼計(jì)數(shù)電路CNT;4位數(shù)碼管動(dòng)態(tài)掃描顯示電路scan_LED。首先,由鍵盤掃描電路完成對(duì)鍵盤的掃描和鍵值的譯碼,當(dāng)計(jì)數(shù)電路置數(shù)端LOAD為上升沿時(shí),將鍵盤掃描電路讀取的數(shù)據(jù)經(jīng)P3-P0并行置入到計(jì)數(shù)器中做為其計(jì)數(shù)范圍,計(jì)數(shù)器的輸出通過動(dòng)態(tài)掃描譯碼模塊驅(qū)動(dòng)4位數(shù)碼管顯示。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論