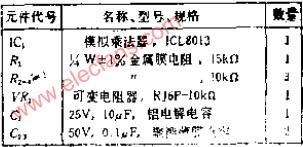

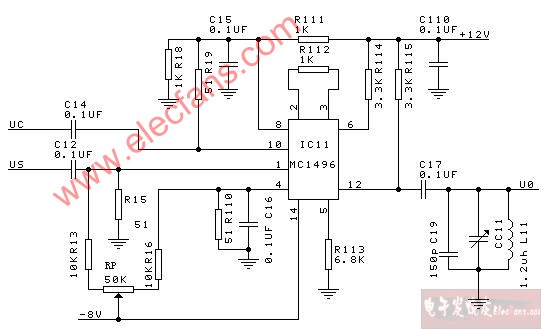

一種模擬乘法器原理圖

- 模擬乘法器(16566)

相關推薦

模擬乘法器AD834的原理與應用

模擬乘法器AD834的原理與應用:AD834是美國ADI公司推出的寬頻寬、四象限、高性能的模擬乘法器。它工作穩定,計算誤差小,并具有低失真和微功耗的特點,本文介紹了AD834模擬乘法器

2009-09-29 10:49:21 180

180

180

180怎么設計基于FPGA的WALLACETREE乘法器?

在數字信號處理中,乘法器是整個硬件電路時序的關鍵路徑。速度和面積的優化是乘法器設計過程的兩個主要考慮因素。由于現代可編程邏輯芯片FPGA的集成度越來越高,及其相對于ASIC設計難度較低和產品設計

2019-09-03 07:16:34

一種用于PFC的模擬乘法器設計

為了實現變頻控制,產生一個與輸入信號同頻同相的電壓信號,使輸入電流跟隨輸入電壓,設計了一種基于BCD工藝的模擬乘法器,并闡述了該電路設計的工作原理和結

2010-07-10 16:35:56 20

20

20

20模擬乘法器AD834的原理與應用

AD834是美國ADI公司推出的寬頻寬、四象限、高性能的模擬乘法器.它工作穩定,計算誤差小,并具有低失真和微功耗的特點,本文介紹了AD834模擬乘法器的主要特性、工作原理、應用考慮和

2009-04-27 16:36:57 84

84

84

84模擬乘法器:The Analog Multiplier

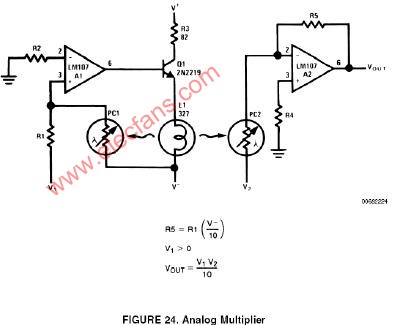

模擬乘法器:The Analog MultiplierA simple embodiment of the analog multiplier is shown in Figure 24.

2009-05-16 16:18:58 3592

3592

3592

3592

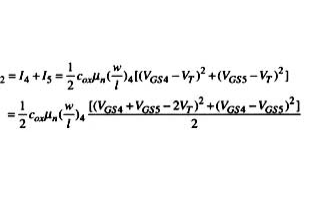

采用Gillbert單元如何實現CMOS模擬乘法器的應用設計

在集成電路系統中,模擬乘法器在信號調制解調、鑒相、頻率轉換、自動增益控制和功率因數校正控制等許多方面有著非常廣泛的應用。實現模擬乘法器的方法有很多,按采用的工藝不同,可以分為三極管乘法器和CMOS乘法器。

2021-03-23 09:40:19 3460

3460

3460

3460

高速四象限模擬乘法器AD834原理

AD834具有的800MHz的可用帶寬是此前所有 模擬乘法器 所無法相比的。在推出AD834之前,ADI公司已經有了大約20年設計模擬乘法器的歷史,也推出過其他的模擬乘法器產品,如:AD734四象限模

2011-07-18 15:33:21 241

241

241

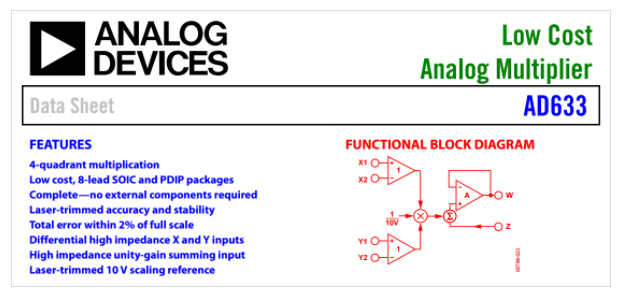

241基于四象限的AD633低成本模擬乘法器

在 MPY634U 四象限模擬乘法器 中給出了四象限模擬乘法器的性能,很奇怪的是它的輸入,輸出之間呈現了很大的非線性。

2021-01-18 15:16:01 6151

6151

6151

6151

模擬乘法器輸出與輸入的關系式

模擬乘法器是輸出電壓與兩路輸入電壓之積成正比的有源網絡。理想的乘法器具有無限大的輸入阻抗及零輸出阻抗,其標尺因子不隨頻率變化并且與電壓的大小無關。如果理想的乘法器的任意一路輸入電壓為零時,則輸出電壓就為零。換句話說,它的失調、漂移和噪聲電壓均為零。

2021-02-18 17:21:19 5188

5188

5188

5188

模擬乘法器ADL5391的原理與應用

簡單介紹了ADI公司推出的新一代高性能模擬乘法器ADL5391的主要特性和工作原理。給出了基于ADL5391的寬帶乘法器的典型應用電路,并對其進行了測試。最后設計了基于ADL5391的二倍頻電路

2013-06-08 17:56:58 185

185

185

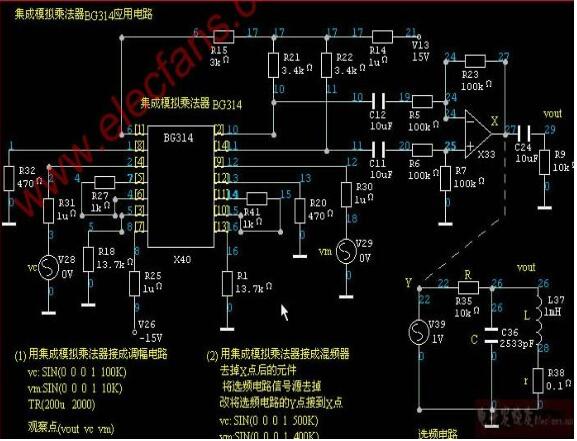

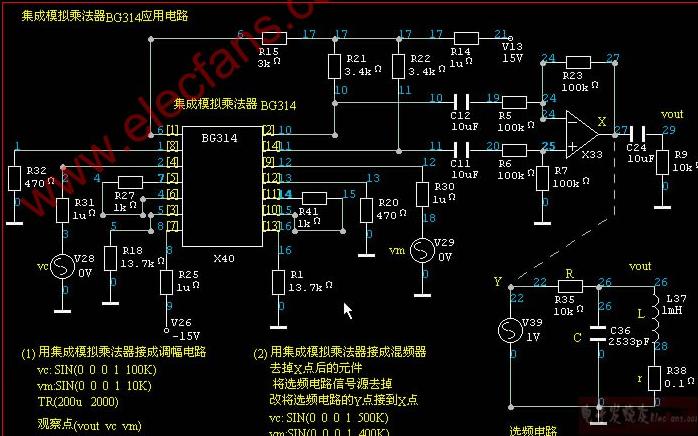

185集成電路模擬乘法器的應用

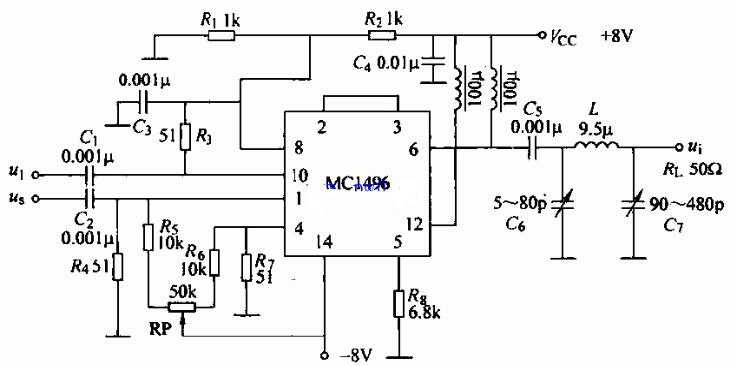

一、實驗目的1、了解模擬乘法器(MC1496)的工作原理,掌握其調整與特性參數的測量方法。2、掌握利用乘法器實驗混頻,平衡調幅,同步檢波,鑒頻等幾種頻率變換電路

2009-03-22 11:21:31 350

350

350

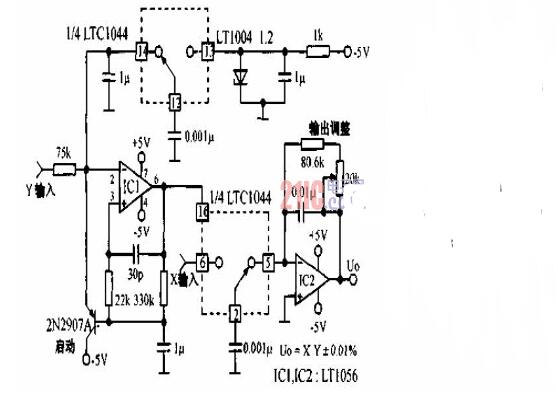

350模擬乘法器電路圖

精密模擬乘法囂電路由精密電容器開關LTC1043及運算放大器LT1056等可組成精密模擬乘法器。精度可達0.01%。電阻選用金屬膜電阻,與LIC1043相連的電容器選用聚苯乙烯的,并盡量靠近器件的管腳安裝。

2021-02-18 15:46:41 14757

14757

14757

14757

模擬乘法器提高高邊電流檢測的測量精度

將模擬乘法器和高邊電流檢測放大器相結合,能夠在筆記本電腦或其它便攜儀器中實現電池充、放電電流的測量。本文討論將模/數轉換器(ADC)的基準電壓加到模擬乘法器的一

2010-01-08 23:00:05 26

26

26

26模擬乘法器提高高邊電流檢測的測量精度

摘要:將模擬乘法器和高邊電流檢測放大器相結合,能夠在筆記本電腦或其它便攜儀器中實現電池充、放電電流的測量。本文討論將模/數轉換器(ADC)的基準電壓加到模擬乘法器的一

2009-05-06 11:07:25 492

492

492

492

模擬乘法器提高高邊電流檢測的測量精度

模擬乘法器提高高邊電流檢測的測量精度

將模擬乘法器和高邊電流檢測放大器相結合,能夠在筆記本電腦或其他便攜儀器中實現電池充、放電電流的測量。本文討論將

2009-12-18 10:19:02 1101

1101

1101

1101畢業設計_基于Multisim_11的模擬乘法器應用設計與仿真

主要內容為基于 Multisim 的模擬乘法器應用設計與仿真。闡述了雙邊帶調幅

及普通調幅、同步檢波、混頻、乘積型鑒相電路的原理,并在電路設計與仿真平

臺 Multisim11 仿真環境中創建

2017-02-07 21:04:01 25

25

25

25乘法器原理_乘法器的作用

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。乘法器不僅作為

2021-02-18 15:08:01 22932

22932

22932

22932

AD835模擬乘法器

AD835是一款完整的四象限電壓輸出模擬乘法器,采用先進的介質隔離互補雙極性工藝制造。它產生X和Y電壓輸入的線性乘積,?3 dB輸出帶寬為250 MHz(小信號上升時間為1 ns)。滿量程(?1 V

2015-11-30 10:32:54 103

103

103

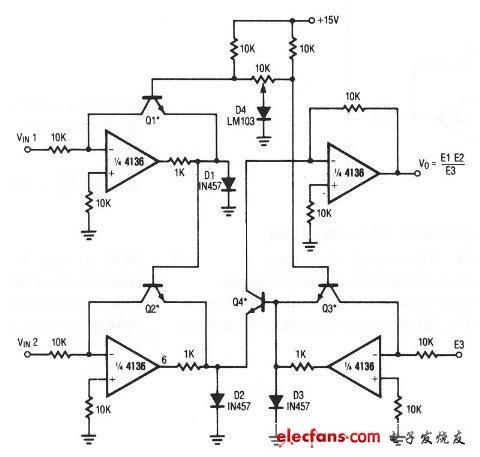

103雙平衡模擬乘法器的基本原理

雙平衡模擬乘法器的基本原理

基本原理

雙平衡式四象限乘法電路如圖1(a)所示,該電路由兩個并聯工作的差分式電路T1、T2和T3、T4及T5、T6

2010-03-24 13:55:51 2531

2531

2531

2531基于CMOS工藝下的Gillbert單元乘法器的研究

在集成電路系統中,模擬乘法器在信號調制解調、鑒相、頻率轉換、自動增益控制和功率因數校正控制等許多方面有著非常廣泛的應用。實現模擬乘法器的方法有很多,按采用的工藝不同,可以分為三極管乘法器和CMOS乘法器。

2019-05-31 08:20:00 2299

2299

2299

2299

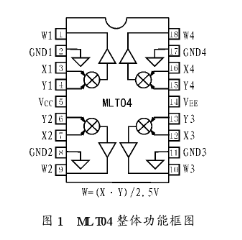

四通道四象限模擬乘法器MLT04的功能特點和應用電路分析

在高頻電子線路中,振幅調制、同步檢波、混頻、倍頻、鑒頻等調制與解調的過程均可視為兩個信號相乘的過程,而集成模擬乘法器正是實現兩個模擬量電壓或電流相乘的電子器件。采用集成模擬乘法器實現上述功能比用分立器件要簡單得多,而且性能優越,因此集成模擬乘法器在無線通信、廣播電視等方面應用較為廣泛。

2020-07-21 10:03:55 2911

2911

2911

2911

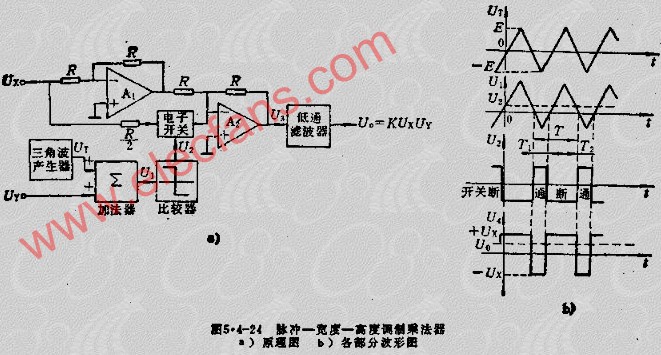

脈沖-寬度-高度調制乘法器

脈沖-寬度-高度調制乘法器

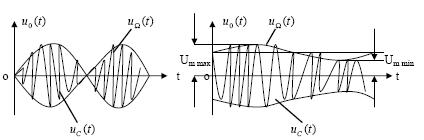

脈沖-寬度-高度調制乘法器雙稱為時間分割乘法器。這類乘法器電路原理圖如圖5.4-24A所示。圖中,三角波電壓UT和模擬輸入電壓UY

2010-05-18 14:23:53 1653

1653

1653

1653

mc1496中文資料 (模擬乘法器)

集成模擬乘法器是完成兩個模擬量(電壓或電流)相乘的電子器件。在高頻電

子線路中,振幅調制、同步檢波、混頻、倍頻、鑒頻、鑒相等調制與解調的過程,

均

2009-03-22 11:32:16 1141

1141

1141

1141AD633,pdf (低成本模擬乘法器)

AD633是一款功能完整的四象限模擬乘法器,包括高阻抗差分X和Y輸入以及高阻抗求和輸入(Z)。低阻抗輸出電壓為10 V標稱滿量程,由一個嵌入式齊納二極管提供。AD633是首款采用價格

2010-10-02 09:44:16 363

363

363

363模擬乘法器的應用詳細資料說明

隨著電子技術的發展,集成模擬乘法器應用也越來越廣泛,它不僅應用于模擬量的運算,還廣泛應用于通信、測量儀表、自動控制等科學技術領域。用集成模擬乘法器可以構成性能優良的調幅和檢波電路,其電路元件參數通常

2019-04-16 08:00:00 6

6

6

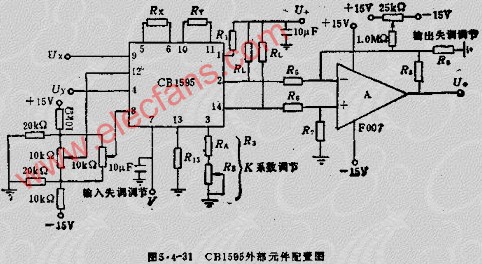

6可變跨導乘法器的品種

可變跨導乘法器的品種

模擬乘法器就基單片結構的形式來說,基本上分為兩大類,即用于處理交流小信號的如圖5.4-27所示的基本電路,以及適用于模擬運算

2010-05-18 15:51:40 1552

1552

1552

1552

如何實現一個四輸入乘法器的設計

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機算數技術來實現。

2019-11-28 07:06:00 2848

2848

2848

2848一種用于SOC中快速乘法器的設計

本文設計了適用于 SOC(System On Chip)的快速乘法器內核。通過增加一位符號位,可以支持24×24 無符號和有符號乘法。在乘法器的設計中,采用了改進的Booth 算法來減少部分積的數目

2009-09-21 10:40:42 20

20

20

20模擬乘法器的一些簡單應用詳細資料說明

隨著電子技術的發展,集成模擬乘法器應用也越來越廣泛,它不僅應用于模擬量的運算,還廣泛應用于通信、測量儀表、自動控制等科學技術領域。用集成模擬乘法器可以構成性能優良的調幅和檢波電路,其電路元件參數通常

2019-03-25 08:00:00 6

6

6

6AD633四象限模擬乘法器的詳細數據手冊免費下載

AD633是功能齊全的四象限模擬乘法器。它包括高阻抗、差分X和Y輸入以及高阻抗求和輸入(Z)。低阻抗輸出電壓是由掩埋齊納提供的標稱10V全量程。AD633是第一個提供這些功能的產品,價格適中的8引腳PDIP和SOIC封裝。

2018-11-30 08:00:00 33

33

33

33使用verilogHDL實現乘法器

本文在設計實現乘法器時,采用了4-2和5-2混合壓縮器對部分積進行壓縮,減少了乘法器的延時和資源占 用率;經XilinxISE和QuartusII兩種集成開發環境下的綜合仿真測試,與用

2018-12-19 13:30:25 10152

10152

10152

10152

ADL5391: DC至2.0 GHz乘法器

ADL5391: DC至2.0 GHz乘法器

ADL5391凝聚了ADI公司三十年的先進模擬乘法器技術經驗,以下通用數學函數經實踐證明,在函數合成方面擁有出色廣泛的

2010-10-02 09:52:51 1453

1453

1453

1453一種高速流水線乘法器結構

設計了一種新穎的3232位高速流水線乘法器結構.該結構所采用的新型Radix-16 Booth算法吸取了冗余Booth編碼與改進Booth編碼的優點,能簡單、快速地產生復雜倍數.設計完成的乘法器只

2018-03-15 13:34:00 6

6

6

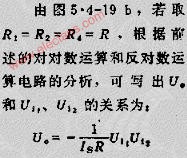

6乘法器對數運算電路應用

乘法器對數運算電路應用

由對數電路實現乘法運算的數學原理是:UO=EXP(INU11+INU12)=U11+U12

圖5.4-19示出了滿足上式的乘法器的方框

2010-04-24 16:03:19 2115

2115

2115

2115

基于FPGA的WALLACE TREE乘法器設計

本文著重介紹了一種基于WALLACETREE優化算法的改進型乘法器架構。根據FPGA內部標準獨特slice單元,有必要對WALLACE TREE部分單元加以研究優化,從而讓在FPGA的乘法器設計中的關鍵路徑時延

2011-11-17 10:50:18 4715

4715

4715

4715

基于IP核的乘法器設計

實驗目的 1、熟悉Xilinx的ISE 軟件的使用和設計流程; 2、掌握Modelsim仿真軟件的使用方法; 3、用乘法運算符實現一個16*16 乘法器模塊; 4、用IP核實現一個16*16 乘法器模塊; 5、用例化語

2011-05-20 17:00:14 66

66

66

66 電子發燒友App

電子發燒友App

評論