為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過? 異步FIFO中讀地址同步在寫時鐘域時序分析不通過的原因可能有以下幾個方面: 1. 讀地址同步在寫時鐘域時序分析未覆蓋完全 在時序分析時,可能

2023-10-18 15:23:55 55

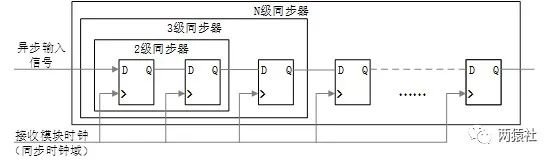

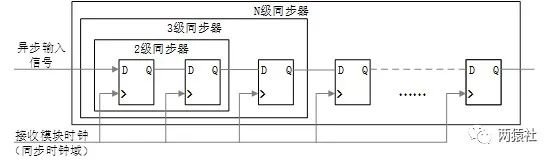

55 摘要:FPGA異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

同步電路與異步電路有何區別 同步電路和異步電路是數字電路中兩種類型的電路,兩種電路在功能、結構、時序要求等方面都存在差異。同步電路和異步電路分別適用于不同類型的應用場景,因此在設計數字電路時要根據

2023-08-27 16:57:02 1852

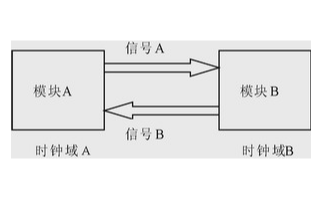

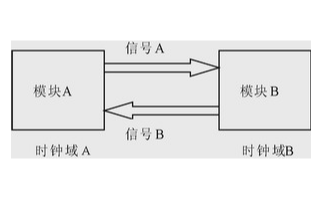

1852 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2023-08-23 16:10:01 161

161 大部分開發者使用 BUFGCTRL 或 BUFGMUX進行時鐘切換,它們在時鐘切換上可以提供無毛刺輸出。

2023-08-16 09:05:15 500

500

同步電路:存儲電路中所有觸發器的時鐘輸入端都接同一個時鐘脈沖源,因而所有觸發器的狀態的變化都與所加的時鐘脈沖信號同步。

2023-08-09 10:04:19 1134

1134

在ASIC設計或者FPGA設計中,我們常常使用異步fifo(first in first out)(下文簡稱為afifo)進行數據流的跨時鐘,可以說沒使用過afifo的Designer,其設計經歷是不完整的。廢話不多說,直接上接口信號說明。

2023-07-31 11:10:19 504

504

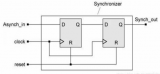

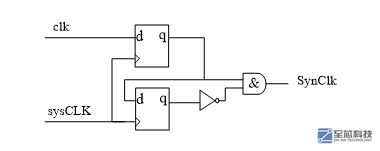

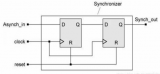

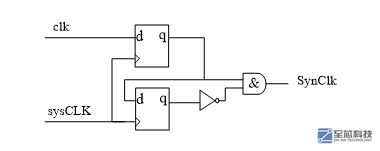

對于從FPGA外部進來的信號,我們通常采用“異步復位同步釋放的策略”,具體電路如下圖所示。

2023-07-20 09:04:21 892

892

異步電路不能根據時鐘是否同源來界定,時鐘之間沒有確定的相位關系是唯一準則。

2023-06-27 10:32:24 367

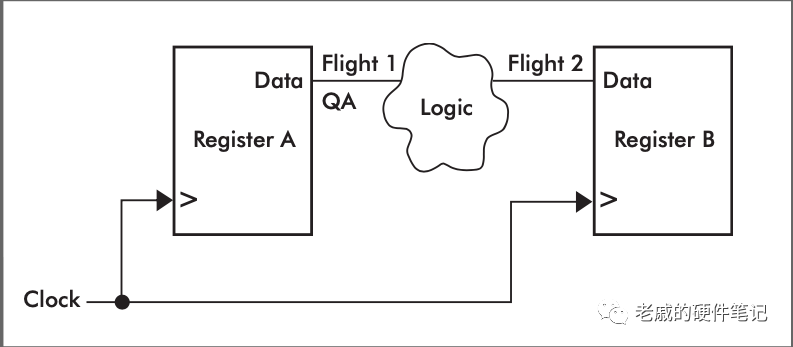

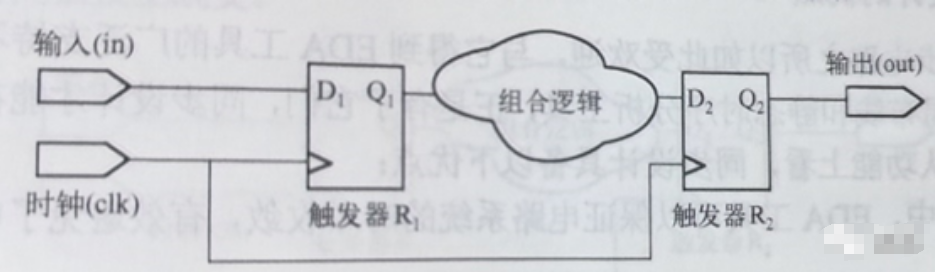

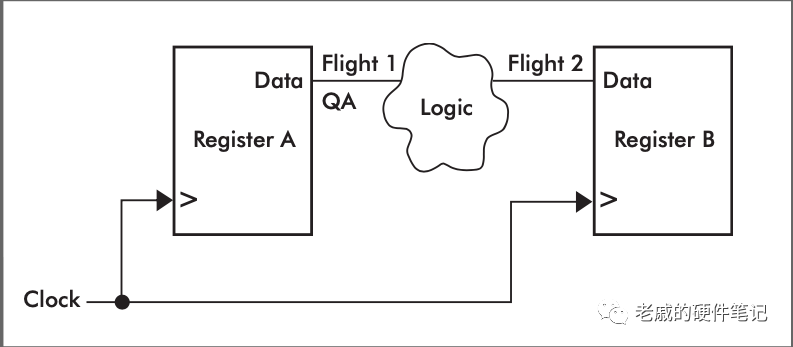

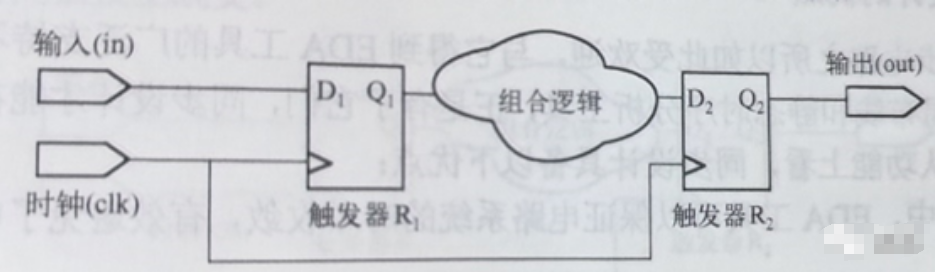

367 、保持(hold)時間的時序關系,電路的輸出(布爾值)就是可預測的,這是數字邏輯電路設計的基礎。如果 不能滿足建立保持時間 ,我們認為輸入是 異步 (asynchronous) 信號 。一個時鐘域的同步信號輸出到另一個時鐘域通常被認為是異步信號。

2023-06-23 17:53:00 449

449

在異步系統中,由于數據和時鐘的關系不是固定的,因此會出現違反建立和保持時間的現象。

2023-06-05 14:34:56 1169

1169

關于異步電路,是面試里被問的最多的部分,網上也有很多很多的總結文章。這里有兩個原因。第一,這是一種比較成熟的通用設計手段,電路結構也比較經典。第二是因為這塊設計在項目中真的很重要。

2023-05-18 11:24:20 1469

1469 跨時鐘域操作包括同步跨時鐘域操作和異步跨時鐘域操作。

2023-05-18 09:18:19 262

262

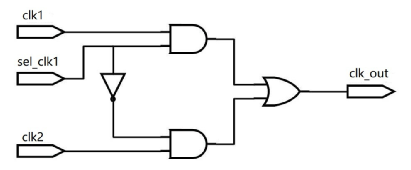

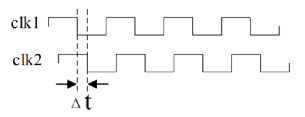

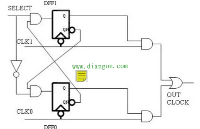

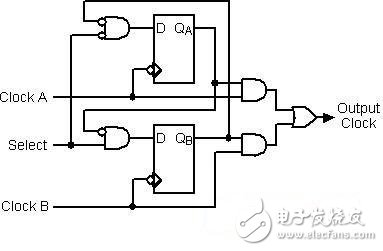

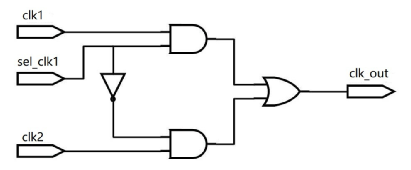

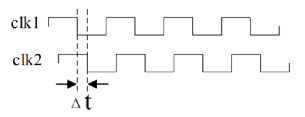

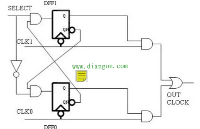

隨著各種應用場景的限制,芯片在運行時往往需要在不同的應用下切換不同的時鐘源,例如低功耗和高性能模式就分別需要低頻率和高頻率的時鐘。兩個時鐘源有可能是同源且頻率比呈倍數關系,也有可能是不相關的。直接使用選擇邏輯進行時鐘切換大概率會導致分頻時鐘信號出現毛刺現象,所以時鐘切換邏輯也需要進行特殊的處理。

2023-03-29 11:41:29 482

482

當觸發器輸入端的數據和觸發器的時鐘不相關時,很容易導致電路時序約束不滿足。本章主要解決模塊間可導致時序 violation 的異步問題。

2023-03-28 13:46:46 3638

3638

同步和異步時序電路都是使用反饋來產生下一代輸出的時序電路。根據這種反饋的類型,可以區分這兩種電路。時序電路的輸出取決于當前和過去的輸入。時序電路分為同步時序電路和異步時序電路是根據它們的觸發器來完成的。

2023-03-25 17:29:52 10208

10208

: ·同步電路與異步電路; ·時鐘/時鐘樹的屬性:偏移(skew)與時鐘的抖動(jitter)、延時(latency)、轉換(transition)時間; ·內部時鐘; ·多路復用時鐘; ·門控時鐘

2023-01-28 07:53:00 1328

1328

同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。

2023-01-17 16:53:16 2692

2692

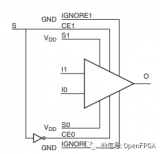

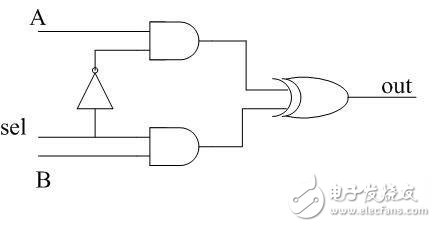

mux啊,可事實真的如此嗎? 如上圖,大家會很自然而想到的一種時鐘切換電路,可是,你仔細分析,你會發現該電路會出現如下的問題,毛刺!這個毛刺無論對于clk0還是clk1都不是好事,它不屬于任何一個時鐘域,它的脈寬根本無法確定,你切換

2023-01-16 11:22:04 1617

1617

FIFO用于為匹配讀寫速度而設置的數據緩沖buffer,當讀寫時鐘異步時,就是異步FIFO。多bit的數據信號,并不是直接從寫時鐘域同步到讀時鐘域的。

2023-01-01 16:48:00 764

764 有幾個因素會影響電路的功耗。邏輯門具有靜態或泄漏功率,只要對其施加電壓,該功率大致恒定,并且它們具有由切換電線產生的動態或開關功率。Flip-flop觸發器非常耗電,大約占總功率的 20%。時鐘消耗

2022-12-12 11:06:44 374

374 同步FIFO的意思是說FIFO的讀寫時鐘是同一個時鐘,不同于異步FIFO,異步FIFO的讀寫時鐘是完全異步的。同步FIFO的對外接口包括時鐘,清零,讀請求,寫請求,數據輸入總線,數據輸出總線,空以及滿信號。

2022-11-01 09:58:16 1028

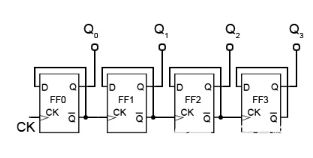

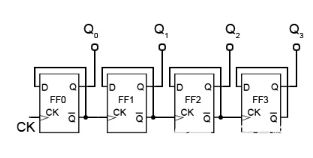

1028 異步計數器是那些輸出不受時鐘信號影響的計數器。由于異步計數器中的觸發器提供有不同的時鐘信號,因此在產生輸出時可能會有延遲。設計異步計數器所需的邏輯門數量非常少,所以它們的設計很簡單。異步計數器的另一個名稱是“波紋計數器”。

2022-10-11 17:16:44 3105

3105

外部晶振+內部時鐘震蕩器+內部PLL +內部分頻器產生時鐘,性能高一點的MCU基本都采用這種方案。

2022-08-31 18:04:08 682

682 在大規模ASIC或FPGA設計中,多時鐘系統往往是不可避免的,這樣就產生了不同時鐘域數據傳輸的問題,其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數據傳輸的緩沖區,這樣既可以使相異時鐘域數據傳輸的時序要求變得寬松,也提高了它們之間的傳輸效率。此文內容就是闡述異步FIFO的設計。

2022-03-09 16:29:18 2075

2075 復位中的同步復位和異步復位問題:恢復時間是指異步復位信號釋放和時鐘上升沿的最小距離,在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,也就是說這個異步控制

2022-01-17 12:25:49 0

0 在STM32f407XX系列中,系統時鐘(SYSTEM)默認的是HSE提供的,這里舉例我們就將默認HSE切換成HSI提供。我們先來看一下時鐘樹(建議保存此圖)首先、在系統中時鐘都是設置好的,如果不是

2021-12-24 19:33:02 5

5 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2021-09-23 16:39:54 2575

2575 AN-291:異步時鐘與AD7878的接口

2021-05-19 19:02:10 0

0 AD9576:雙鎖相環異步時鐘發生器數據表

2021-05-16 12:57:55 0

0 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。 FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2021-05-10 16:51:39 3513

3513

電子發燒友網為你提供基本時鐘切換術語和標準輸入時鐘切換配置資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-05 08:40:34 7

7 同步電路是由時序電路(寄存器和各種觸發器)和組合邏輯電路構成的電路,其所有操作都是在嚴格的時鐘控制下完成的。這些時序電路共享同一個時鐘CLK,而所有的狀態變化都是在時鐘的上升沿(或下降沿)完成的。

2021-01-04 10:53:37 13650

13650 本發明提供了一種將異步時鐘域轉換成同步時鐘域的方法,直接使用同步時鐘對異步時鐘域中的異步寫地址狀態信號進行采樣,并應用預先設定的規則,在特定的讀地址位置對同步時鐘域中的讀地址進行調整,使得在實現

2020-12-21 17:10:55 5

5 異步電路 1. 電路的核心邏輯是組合電路,比如異步的FIFO/RAM讀寫信號、地址譯碼信號等電路; 2. 電路的輸出不依賴于某一個時鐘,也就說不是由時鐘信號驅動觸發器產生的; 3. 異步電路非常容易

2020-12-05 11:53:41 9613

9613 首先肯定是在本時鐘域內的clk_en會先變低(invalid),之后才會使得另外時鐘域內的clk_en變高(valid),這時另外一個時鐘域內的時鐘才能和clk_en相與輸出。

2020-11-10 15:06:59 1709

1709 1、什么是同步邏輯和異步邏輯,同步電路和異步電路的區別是什么? 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。 電路設計可分類為同步電路和異步電路設計。同步電路利用時鐘

2020-11-09 14:58:34 8729

8729 在多時鐘設計中可能需要進行時鐘的切換。由于時鐘之間可能存在相位、頻率等差異,直接切換時鐘可能導致產生glitch。

2020-09-24 11:20:38 5061

5061

在數字電路設計中,大部分設計都是同步時序設計,所有的觸發器都是在同一個時鐘節拍下進行翻轉。這樣就簡化了整個設計,后端綜合、布局布線的時序約束也不用非常嚴格。但是在設計與外部設備的接口部分時,大部分

2020-07-24 09:52:24 3655

3655

異步 FIFO 讀寫分別采用相互異步的不同時鐘。在現代集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘,多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO

2020-07-16 17:41:46 953

953

異步時序電路是指電路中除以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路中沒有統一的時鐘;電路狀態的改變由外部輸入的變化直接引起.

2019-11-27 07:04:00 1510

1510 時鐘同步問題講完了,下面就開始講講soc中另一種常見的情況,有時為了考慮到功耗,性能的問題,某個模塊可能在某一種情況下工作在一個頻率,另一種情況下工作在另一種頻率,這個時候就需要進行mux的切換,有的人就會說了,哪簡單啊,加個mux啊,可事實真的如此嗎?

2019-09-13 15:31:00 4069

4069 同步復位和異步復位都是狀態機的常用復位機制,圖1中的復位電路結合了各自的優點。同步復位具有時鐘和復位信號之間同步的優點,這可以防止時鐘和復位信號之間發生競爭條件。但是,同步復位不允許狀態機工作在直流時鐘,因為在發生時鐘事件之前不會發生復位。與此同時,未初始化的I/O端口可能會遇到嚴重的信號爭用。

2019-08-12 15:20:41 6574

6574

跨時鐘域的問題:前一篇已經提到要通過比較讀寫指針來判斷產生讀空和寫滿信號,但是讀指針是屬于讀時鐘域的,寫指針是屬于寫時鐘域的,而異步FIFO的讀寫時鐘域不同,是異步的,要是將讀時鐘域的讀指針與寫時鐘域的寫指針不做任何處理直接比較肯定是錯誤的,因此我們需要進行同步處理以后進行比較。

2018-09-05 14:29:36 5390

5390 在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 7656

7656

SDI II動態TX時鐘切換功能實現和硬件驗證

2018-06-20 00:34:00 5030

5030 異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 1877

1877 大家好,又到了每日學習的時候了。今天我們來聊一聊異步電路中的時鐘同步處理方法。 既然說到了時鐘的同步處理,那么什么是時鐘的同步處理?那首先我們就來了解一下。 時鐘是數字電路中所有信號的參考,沒有時鐘

2018-05-21 14:56:55 12462

12462

現在的硬件設計中,大量的時鐘之間彼此相互連接是很典型的現象。為了保證Vivado優化到關鍵路徑,我們必須要理解時鐘之間是如何相互作用,也就是同步和異步時鐘之間是如何聯系。 同步時鐘是彼此聯系的時鐘。

2018-05-12 10:15:00 19165

19165 言歸正傳,我們還是重點看看異步電路。異步電路有時也稱為無時鐘(clockless)或者自定時(self-timed)電路,顧名思義,就是沒有全局時鐘的電路,如下圖所示。在異步電路中,大家沒有一個統一的時鐘,前后級直接告知對方能否接收數據。

2018-05-01 16:24:00 28963

28963

時鐘是數字電路中所有信號的參考,特別是在FPGA中,時鐘是時序電路的動力,是血液,是核心。

2018-03-28 17:12:20 12787

12787 針對變繞組異步電機繞組結構與普通異步電機的差異性,為反映繞組切換的暫態過程,并為電機控制系統和繞組切換電路設計提供參考,提出了一種新的變繞組異步電機的建模方法。通過對電機繞組切換前后的兩套繞組

2018-03-02 15:56:35 1

1 在現代的集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘。多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個

2018-02-07 14:22:54 0

0 異步電路:主要是組合邏輯電路,用于產生地址譯碼器、FIFO或RAM的讀寫控制信號脈沖,但它同時也用在時序電路中,此時它沒有統一的時鐘,狀態變化的時刻是不穩定的,通常輸入信號只在電路處于穩定狀態時才

2017-11-30 09:35:40 30261

30261

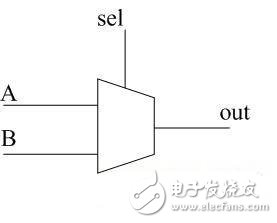

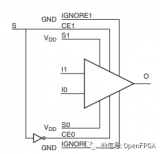

對于一個時鐘切換電路,輸入兩個異步時鐘 clk0、clk1,以及一個選擇信號 sel。 (1) 假設不考慮 glitch,直接使用Mux 就可以完成切頻。電路如下: 由于 clk0/clk1/sel

2017-09-29 16:36:06 9

9 切換型異步電動機雙饋調速系統_馬小亮

2016-12-13 22:20:48 1

1 STM8的C語言編程(11)--+切換時鐘源

2016-11-15 16:44:22 2

2 現代集成電路芯片中,隨著設計規模的不斷擴大。一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現

2014-05-28 10:56:41 3264

3264 FPGA 異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 異步電路主要是組合邏輯電路,用于產生地址譯碼器、FIFO或RAM的讀寫控制信號脈沖,但它同時也用在時序電路中,此時它沒有統一的時鐘,狀態變化的時刻是不穩定的,通常

2011-05-25 15:28:36 132

132 工業頻率在一臺變頻器控制多臺大功率異步電動機軟啟動的情況下,必然涉及到異步電動機變頻轉工頻的切換過程,在此過程中被切換電機就可能出現定子繞組電壓過大從而產生過

2010-10-25 16:57:20 37

37 相較純粹的單一時鐘的同步電路設計,設計人員更多遇到的是多時鐘域的異步電路設計。因此,異步電路設計在數字電路設計中的重要性不言而喻。本文主要就異步設計中涉及到的

2010-07-31 16:51:41 56

56 高速異步FIFO的設計與實現

引言

現代集成電路芯片中,隨著設計規模的不斷擴大.一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設

2010-04-12 15:13:08 2722

2722

矩陣切換器,矩陣切換器電路原理

電路原理:切換原理上就是選擇,選擇的方式有很多種,最簡單的就是將信號線直接

2010-03-26 11:50:54 4619

4619 異步傳輸,異步傳輸是什么意思

異步傳輸方式并不要求發送方和接收方的時鐘完全一樣,字符與字符間的傳輸是異步的。

在網絡通信過程中,

2010-03-17 16:30:18 7324

7324 在大規模集成電路設計中,一個系統包含了很多不相關的時鐘信號,當其目標域時鐘與源域時鐘不同時,如何在這些不同域之間傳遞數據成為了一個重要問題。為了解決這個問題,

2009-12-14 10:19:07 14

14 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態改變方式不同的特殊性出發, 系統的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 59

59 相對與同步切換,異步切換會對切換掉話率有多少影響

同步切換需要網絡中的基站間同步,異步切換則不需要網絡中基站間的同步。基站

2009-06-18 00:13:40 743

743 AD7878用于微處理器的異步時鐘接口方法:

2009-06-10 11:48:59 31

31

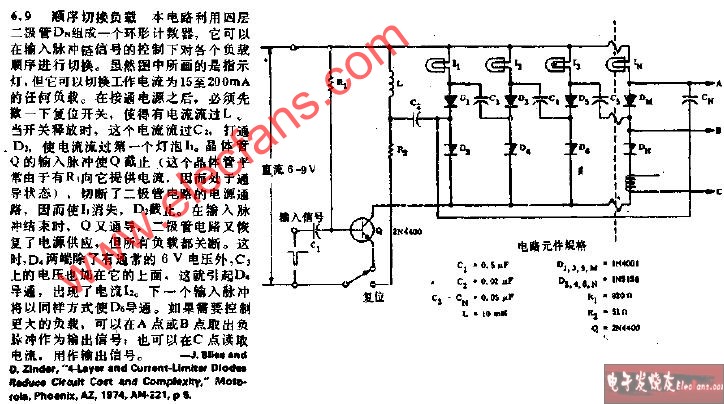

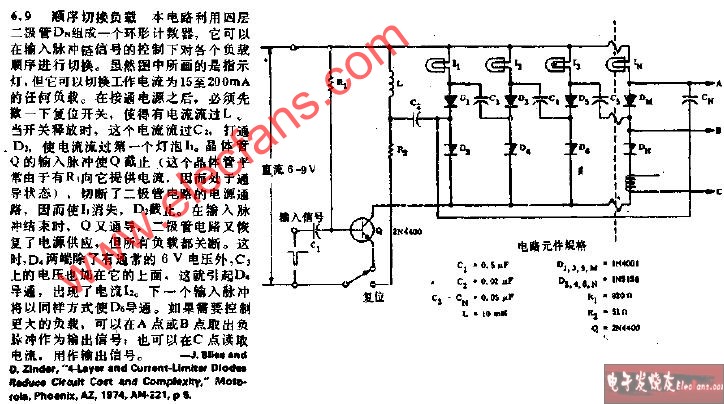

順序切換負載電路

2009-01-17 14:09:02 688

688

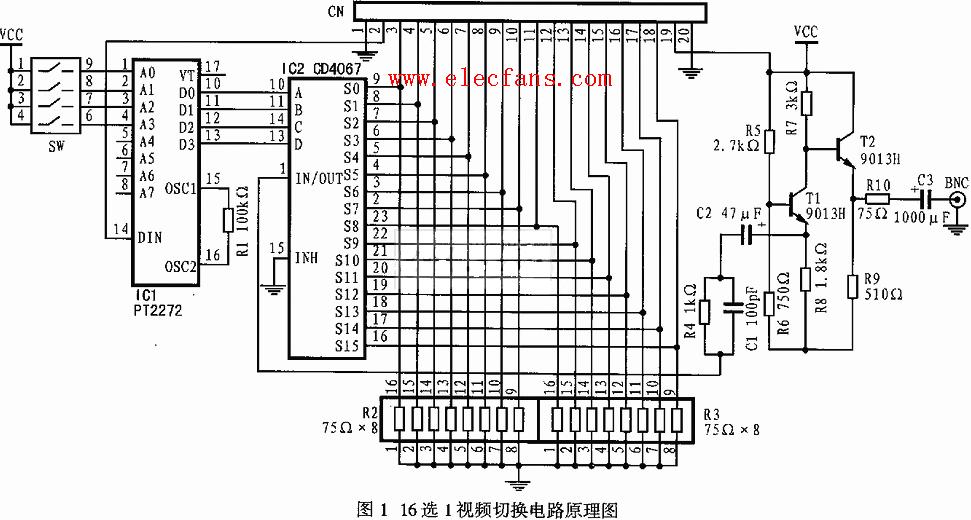

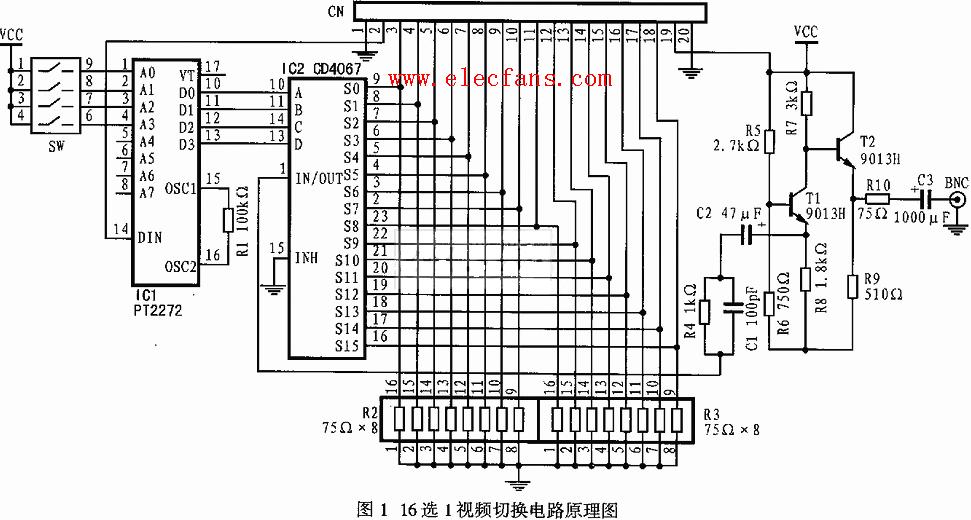

視頻切換電路圖:上圖為16路選1的視頻切換電路

2008-05-23 12:33:10 1251

1251

正在加载...

電子發燒友App

電子發燒友App

評論