摘要:介紹了一種基于VXI總線的四通道智能化任意波發生器及波形調制模塊。本模塊采用DSP+FPGA實現智能控制,應用先進的DDS(直接數字頻率合成器)技術產生任意波,輸出波形可加載波進行調制;本模塊具有四個獨立的通道,相互之間進行電氣隔離,可輸出幅度連續可調的電壓和電流信號。

VXI總線是VMEbus extensions for Instrumentation的縮寫。VXI主機箱有13個插槽,其中,零槽控制器為系統的管理者。VXI模塊根據其本身的性質、特點和所支持的通信規程可以分為寄存器基、消息基、存儲器和擴展模塊四種類型。每個模塊的地址空間有A16、A16/A24和A16/A32三種類型。

本文介紹利用DDS(直接數字頻率合成器)技術實現具有任意波發生以及調幅功能的模塊。與傳統的頻率合成技術相比,DDS技術具有很多優點:頻率切換時間短、工作頻率范圍寬、頻率分辨率高、相位變化連續和容易對輸出信號實現調制等。一些公司先后推出了各種各樣的DDS專用芯片,這些DDS專用芯片為電路設計提供了很大方便,但是并不能滿足所有要求。例如,在實現調頻及調幅等復雜功能時,利用現有的DDS專用芯片就會很不方便。利用可編程邏輯器件(CPLD)或現場可編程門陣列(FPGA)實現DDS具有很大的靈活性,能夠很好地滿足電路設計要求。

1 DDS基本原理

DDS在基本原理框圖如圖1所示。它主要由標準參考頻率源、相位累加器、波形存儲器、數/模轉換器、低通平滑濾波器等構成。其中,參考頻率源一般是一個高穩定度的晶體振蕩器,其輸出信號用于DDS中各部件同步工作。DDS的實質是對相位進行可控等間隔的采樣。

相位累加器的結構如圖2所示。它是實現DDS的核心,由一個N位字長的加法器和一個由固定時鐘脈沖取樣的N位相位寄存器組成。將相位寄存器的輸出和外部輸入的頻率控制字K作為加法器的輸入,在時鐘脈沖到達時,相位寄存器對上一個時鐘周期內相位加法器的值與頻率控制字K之和進行采樣,作為相位累加器在此刻時鐘的輸出。相位累加器輸出的高M位作為波形存儲器查詢表的地址,從波形存儲器中讀出相應的幅度值送到數/模轉換器。

當DDS正常工作時,在標準參考頻率源的控制下,相位累加器不斷進行相位線性累加(每次累加值為頻率控制字K),當相位累加器積滿時就會產生一次溢出,從而完成一個周期性的動作,這個周期就是DDS合成信號的頻率周期。輸出信號波形的頻率為:

顯而易見,當K=1時輸出最小頻率,即頻率分辨率為fmin=fc/2N。式中,fout為輸出信號頻率;K為頻率控制字;N為相位累加器字長;fc為標準參考頻率源工作頻率。

2 波形發生器模塊的實現

2.1 硬件部分

波形發生器模塊結構框圖如圖3所示。

硬件主要可分為總線接口、DSP及邏輯控制電路、四通道DDS波形發生及調制電路、信號調理和輸出接口等幾部分。其中,零槽控制器與DSP之間用雙口RAM作為通訊中介,雙口RAM采用IDT709289L,其容量為64K×16Bit。

根據零槽控制器和模塊交換信息的特點,本模塊采用寄存器基的A16/A24的操作模式,數據為16Bit。在A16的尋址方式下,每個模塊都具有一組配置寄存器,系統可以通過訪問這些寄存器來獲得器件的種類、型號、生產廠家、地址空間及存儲器需求等。在A24模式下,零槽控制器可為一個模塊配置的存儲空間,最大為256n×2 23-m,其中,n在A32模式下為1,在A24模式下為0,m為器件型號寄存器高四位所定義的數值。在本模塊中,m取值為6,存儲器地址空間為128Kbyte。總線接口采用ALTERA公司的EPM3256A實現。板內接口邏輯和所有控制邏輯均采用Verilog硬件描述語言完成。

接口電路中的雙口RAM用作命令、參數和數據傳輸,分為命令參數區和數據區。雙口RAM被均分為16頁,每頁為4K×16Bit,前15頁作為自定義的波形傳輸區,第16頁為命令參數區。雙口RAM的采用使模塊的設計相對于VXI系統而言具有很大的獨立性,從而使波形發生電路能夠方便地移植到其它總線上。

板內主控CPU芯片選用了TI公司的TMS320F206。它主要起智能控制作用,接收通過VXI總線發來的各種命令,然后分析命令,執行命令,協調模塊各部分的工作。與非智能模塊相比,本模塊具有明顯的優越性。除了自定義波形以外,零槽控制器只需向模塊發簡單的命令和參數,DSP就能完成所有的功能。這樣就大大減少了上位機和控制器的時間開銷,使它們有更多的時間處理其它事件,有利于保證整個VXI系統可靠、協調地工作。

DSP外擴數據存儲器包括一片IDT709289L和四片IDT7025S,IDT9289L的每一頁映射到DSP數據區0x7000~0x7FFF,用于接口電路,頁面的切換用DSP的I/O譯碼控制。4個IDT7025S均映射到DSP數據區0x8000~0x9FFF,分別用作四路DDS的波形存儲器,4個IDT7025S的片選由DSP進行控制。DSP相關的譯碼及控制電路用一片EP1K10來實現。

圖3

單個通道DDS波形發生及輸出部分功能框圖如圖4所示。

每通道的累加器及邏輯控制電路均采用一片EP1K30,用于實現累加器和步長控制字寄存器并完成板上地址譯碼、兩級DAC控制、波形抖動補償以及本通道的繼電器控制等功能。累加器字長32位,時鐘基準源頻率為DSP輸出頻率的兩倍頻。第一級DAC用于波形的產生,第二級DAC用于控制輸出幅度和波形正反相,并對第二級DAC輸出進行了平滑濾波和放大處理。

根據系統的性能要求,輸出端采用了電壓隔離放大器,與總線隔離,并且四個通道各自獨立。本模塊總共有一個數字地和四個模擬輸出地。這樣,既可以保證VXI系統和其它通道的安全,又減少了模塊負載和VXI系統的相互干擾。

波形數據存儲器IDT7025S被等分為A、B兩頁,可以實現不同波形之間的無抖動切換,每頁為4k×16bit。當DDS開始工作時,DSP先鋒主A頁寫入波形數據,并在DSP的控制下產生波形;當要切換到另一種波形時,只需往B頁寫入另一種波形的數據,將32位累加器所產生的地址(累加器高12位)切換到B頁即可。這樣,可實現幅值和相位均連續的波形無抖動切換。

每個通道采用兩級12Bit DAC,它們均設置為雙極性電壓輸出。第一級DAC的參考電壓源可以接內部基準或外部載波,第二級DAC的參考電壓源可以接內部基準、外部載波或第一級DAC電壓輸出。通過對兩級DAC所接參考電壓源的不能設置(通過繼電器進行切換),可以分別實現如下功能:

(1)用作直接輸出,第二級DAC的參考電壓源接內部基站。第二級DAC電壓輸出為:V2out=(Din2-2048)/2 12,可通過輸入不同的Din2控制直流輸出幅值和正負極性。

(2)用作函數發生器,第一級DAC參考電壓源接內部基,第二級DAC參考電壓源接第一級DAC電壓輸出,波形存儲器存放不同函數波形數據可輸出不同的函數波形。此時,第一級DAC輸出電壓為:V1out=Vref×(Din1-2048)/2 12,其中,Vlout為第一級DAC雙向輸出電壓,Vref為DAC參考電壓源,Dinl為第一級DAC輸入數據。在這里Vref為常值2V,式中只有Dinl為變量,Din1對應波形存儲器中4096個波形幅值數據(一個周期)。當波形數據以500kHz的速率依次裝載到DAC時,由公式(1)得DAC輸出波形的頻率為:fout=K×(10 6/2 33)。第二級DAC輸出電壓為:V2out=Vlout×(Din2-2048)/2 12,其中,V2out為第二級DAC輸出電壓,Din2為第二級DAC輸入數據。

(3)用作自定義波形發生器,第一級DAC和第二級DAC的設置為(2)所述,不同的是波形存儲器的內容。零槽控制器按一定的規約向雙口RAM(IDT709289L)的前15頁寫入自定義的波形數據,DSP亦按一定的規約取出數據并送往指定通道的IDT7025S,IDT7025S的A和B兩頁進行交替切換,從而連接輸出自定義波形。

(4)外加載波進行調制,第一級DAC參考電壓源接外部載波,第二級DAC參考電壓源接第一級DAC電壓輸出。外加載波為正弦信號Vsin(αx+θ) ,其中,V為載波最大電壓值,α為自變量x的系數,θ為初始相位。第一級DAC電壓輸出為:Vlout=Vsin(αx+θ) ×Dinl/2 12,這樣即實現了載波的幅度調制。第二級DAC用來控制整個幅度,其輸出電壓V2out=Vsin(αx+θ) ×Din1/2 12×(Din2-2048)/ 2 12,Din2為第二級DAC的輸入數據。

(5)載波直接輸出,只需第二級DAC的參考電壓源接外部載波,第二級DAC電壓輸出為:V2out=Vsin(αx+θ) ×(Din2-2048)/2 12。

由于隔離放大器有一定的輸出噪聲,所以把信號放大器放在隔離放大器之前,低通濾波器放在隔離放大器之后,這樣,既避免把隔離入大器的噪聲放大,又有效地進行了平滑濾波。

電壓輸出采用功率運放OPA445進行放大,實現±12V輸出。而電流輸出則采用電壓/電流轉換器AD694實現,電流輸出量程為0~20mA或4~20mA。

2.2 軟件部分

軟件主要包括兩部分:DSP程序和VXI系統主機底層驅動函數及測試程序。

DSP程序采用C語言和匯編語言混合編程。控制部分的程序采用了匯編語言,提高了程序的效率。而數據的產生部分采用了實現起來比較簡單的C語言,避免了采用匯編處理數據的復雜編程。

上位機測試程序采用NI公司的LabWindows/CVI編制。LabWindows/CVI基于C語言的編程環境,具有豐富的用戶界面控件和VXI總線系統函數,使編程簡捷方便。面向本模塊的操作函數打包生成.dll文件即可供系統調用。

3 實現結果及分析

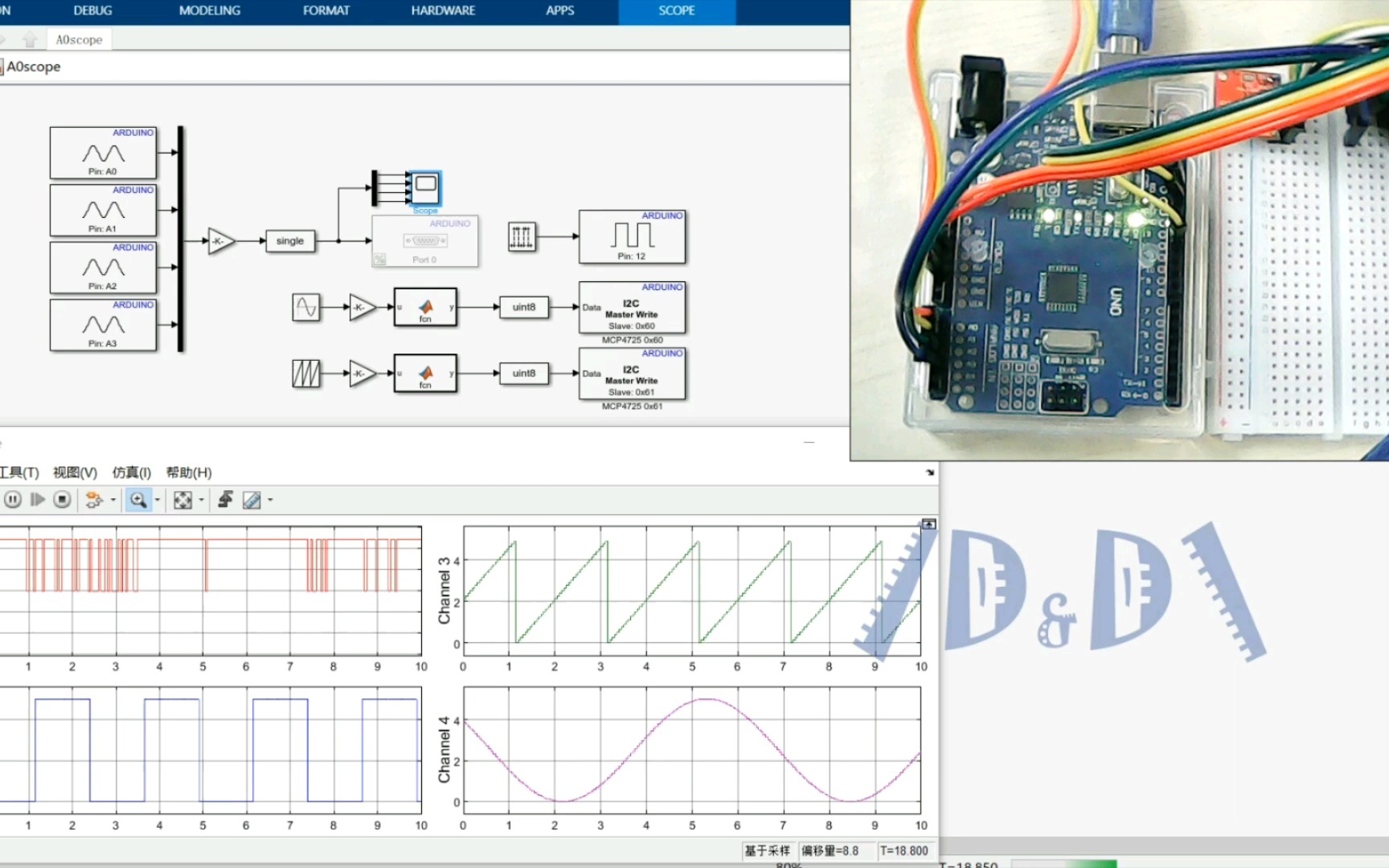

圖5所示為輸出頻率為10kHz的方波、鋸齒波、正弦波和三角波的輸出波形,其峰-峰值均為24V。圖6所示為調制波輸出波形,10kHz外部正弦波作為載波信號,1kHz正弦波信號作為調制信號,峰-峰值為24V。圖5和圖6均由Tektronix公司的TDS210型示波器采樣所得。

經實驗所得的波形輸出的頻率分辨率為0.1%左右,顯然大于理論的頻率分辨率fmin=10 6/2 33=0.0001164Hz。經分析,系統誤差包括:(1)相位截尾誤差;(2)電路板布局布線因素帶來的干擾而導致的誤差;(3)標準參考頻率源穩定性的影響帶來的誤差;(4)D/A轉換器引入的誤差;(5)波形幅值存儲數據有限字長引入的量化誤差。

本模塊中實現的DDS相對于傳統方法具有種種優點。由于DSP強大的數據處理能力和靈活的控制功能,再加上FGPA具有的高性能、高集成度等特點,使模塊具有優良的性能。另外,DDS的這種實現方法有很大的靈活性,可以進行復雜的濾形調制。

由于DDS數字化實現過程的固有特點,如累加器相位截斷、波形幅度量化和數/模轉換器的非線性等特性,使得輸出信號頻譜的雜散性較大,這一點當輸出頻率較高時尤為突出。因此,在設計的過程中要采取一定的改進措施。如對DDS的結構加以改進、優化波形存儲器的結構、選擇合適的數/模轉換器件、使用抖動注入技術等,盡量減少其雜散性,從而使DDS系統具有更優良的性能。

電子發燒友App

電子發燒友App

評論