摘????要:本文介紹了應用于磁軸承的雙DSP熱備容錯控制方案,該方案采用時鐘同步技術,由總線表決模塊實現系統的容錯處理,硬件判決模塊實現硬件故障判斷。由中心仲裁模塊根據兩判決模塊的結果進行復雜的仲裁,并完成切換和完善的報警邏輯,從而提高了磁軸承控制系統的可靠性。

關鍵詞:容錯;磁軸承;?控制器;?CPLD;?DSP

引言

電磁軸承(AMB)是利用可控電磁吸力將轉子懸浮起來的一種新型高性能軸承,具有無接觸、無摩擦、高速度、高精度、不需潤滑和密封等一系列特點,在交通、超高速超精密加工、航空航天等高科技領域有著廣闊的前景。

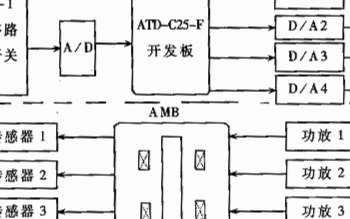

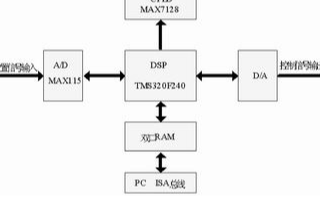

由于磁懸浮系統本征不穩定,控制系統的好壞將會直接決定磁軸承的性能。近年來國內外在數字控制方面發展很快,數字控制器將是未來的磁軸承控制的主流,圖1為數字磁軸承控制系統結構框圖。本文從工業應用的要求和成本考慮,對圖1虛線方框內的控制器進行了容錯設計,提出了雙DSP容錯控制器的方案,而對于傳感器、線圈和功率放大器部分的容錯設計本文不進行討論。

磁懸浮控制器的容錯設計分析

冗余是實現容錯和提高可靠性的一種有效方法,對于磁軸承DSP控制系統來說,其本身的時間余量和程序空間余量都非常有限,故主要是采用硬件冗余,即采用多DSP冗余設計來提高系統的可靠性。

在多機冗余系統設計中,關鍵問題是多機的重構策略、多機的仲裁切換邏輯及多機運行的同步等。小規模的終端系統相對于功能強大的中央控制系統有四個明顯的特點:系統結構較簡單、成本較低;軟硬件資源比較缺乏;必須具備很好的實時性能;運行時間余度太小。通過以上分析與對成本的考慮,本文提出了針對工業應用的雙機熱備冗余控制系統設計方案。

設計原理

本控制系統結構如圖2所示,其中冗余核心控制功能是通過CPLD來實現的。模擬信號分別輸入到兩個DSP進行運算,由中心仲裁模塊選擇主DSP,然后由主DSP來處理輸出到D/A轉換的數據、時序和RS-232的輸出信號。

輸入緩沖模塊

為了消除輸入端輸入阻抗帶來的影響,對于數字信號增加一級緩沖器,可以減小外圍電路的干擾。本系統中,主要是進行RS-232和晶振、復位、外部中斷輸入信號的緩沖(RS-232的輸出接口由主DSP進行控制)。另外,對于模擬信號本設計通過電壓跟隨器來實現阻抗匹配,并減小了誤差和A/D轉換的時間。

DSP時鐘同步的實現

由于本設計方案是通過DSP的完全同步來實現冗余控制的,故采用雙DSP共同使用一個晶振信號的方式。系統工作時,要待電源穩定和晶振完全起振后,才能對DSP進行復位。通過對實驗室現有的控制系統的測試,電源穩定和晶振穩定起振的時間大概是40ms,故復位時間應選擇大于該值。此外,為了提高其抗干擾性,復位后的信號經過施密特觸發器后最好先經過CPLD緩沖,然后再接到DSP的復位端。

硬件故障判決模塊

本設計中使用每個DSP?CLKOUT引腳的輸出信號作為判決硬件故障的基本條件。如果DSP硬件正常工作,CLKOUT引腳將輸出固定的時鐘波形;如果系統的CLKOUT沒有時鐘波形輸出,將認為該DSP硬件不正常,然后由中心仲裁模塊來隔離該DSP。其具體實現方法就是CLKOUT信號經CPLD實現的分頻器后送到單穩態觸發器74LS123,若系統的CLKOUT信號不正常,74LS123會產生跳變,驅使中心仲裁模塊隔離不正常DSP。

輸出總線表決模塊

輸出總線表決模塊主要實現系統的容錯,解決系統的軟故障。當兩DSP的總線輸出信號進行比較時,如果不相同,則表明某個DSP或者兩個DSP都產生了軟故障,系統抑止錯誤輸出,并由中心仲裁模塊對此情況進行處理,使系統實現容錯功能。考慮到A/D轉換的誤差,本設計只對輸出數據總線的高8位進行表決。?

中心仲裁模塊

中心仲裁模塊主要是分析由輸出總線表決模塊和硬件故障判決模塊輸出的結果,并做出判斷,確定主DSP。主DSP的功能主要是控制對外的輸出,包括控制D/A轉換輸出和RS-232的輸出。

中心仲裁模塊的仲裁方式

當硬件判決模塊和軟件表決模塊都沒有報錯,則系統采用默認的DSP1為主DSP;如果硬件判決模塊有一塊DSP報錯,則隔離出錯的DSP,另一個為主DSP?,并且報警;如果兩個DSP都報錯,則會報告系統的錯誤,并提供控制系統產生錯誤的接口信號,讓系統在最短的時間里啟動安保系統。當兩個DSP都沒有產生DSP硬件報錯時,如果軟件表決模塊報錯,則通過CPLD啟動復位信號,重新復位兩個DSP,并由CPLD核心控制模塊記錄復位次數,如果系統連續復位次數超過四次且沒有出現一次正確的輸出總線結果或兩個DSP在線自檢均沒有通過,將會啟動安保系統;如果有一個DSP自檢不通過,則隔離該DSP,系統會輸出報警信號,同時主DSP控制權交給另一DSP;如果復位次數小于四次,且出現了正確的輸出總線結果,CPLD模塊會清除復位計數次數,主DSP依然是DSP1。

DSP軟件實現

系統的軟件流程框圖如圖3所示,其中虛線方框內是通過CPLD實現的。在DSP系統中,使用了看門狗模塊,來解決系統程序跑飛問題。系統復位后,通過檢測看門狗電路復位標志位來檢測系統程序狀態,如果是系統看門狗復位,通過軟件使DSP產生輸出總線報錯,其結果與輸出總線報錯處理方式一樣;否則為由仲裁模塊引起的復位,并且執行在線自檢。如果在線自檢不通過,CPLD會自動隔離硬件。設計中為減小系統的復位時間和控制系統的連續性,存儲數據的時候采用了雙口RAM?idt7133,這樣可以在復位后快速的采用前一次計算的暫存數據(相互取對方數據,并且與自己的數據進行平均),從而使復位對系統的影響降到最小。

在線自檢的實現

通過CPLD中心仲裁模塊來控制信號傳輸控制門,實現A/D轉換,轉換成基準電平(本設計采用2.5V)后再通過實際的控制算法來計算,并將結果輸出到CPLD與離線計算好的結果(存儲在CPLD上)進行比較,如果實時計算結果和離線結果相同,則表示系統自檢通過,否則,自動隔離自檢不通過的DSP。

系統的可靠性評估

系統的中心控制模塊是采用CPLD實現的,其可靠性遠高于基于程序實現的DSP,本系統中把CPLD的故障率近似認為是0,即平均無故障時間遠大于DSP。

根據電子系統模型可知,單機的可靠性隨時間變化服從指數分布,即為Ri(t)=e-lit(li為故障率),所以單機系統的平均無故障時間為1/l,而本方案的無平均故障時間為:

顯然,本系統的無故障時間為單機運行的1.5倍,較大的提高了控制器系統的可靠性。

結語

本文提出的磁懸浮容錯控制器方案,采用了軟硬件協同設計,實現了故障診斷和系統重建的功能,較大的提高了控制器的可靠性,為磁軸承的工業推廣應用提供了性能保障。?

關鍵詞:容錯;磁軸承;?控制器;?CPLD;?DSP

引言

電磁軸承(AMB)是利用可控電磁吸力將轉子懸浮起來的一種新型高性能軸承,具有無接觸、無摩擦、高速度、高精度、不需潤滑和密封等一系列特點,在交通、超高速超精密加工、航空航天等高科技領域有著廣闊的前景。

由于磁懸浮系統本征不穩定,控制系統的好壞將會直接決定磁軸承的性能。近年來國內外在數字控制方面發展很快,數字控制器將是未來的磁軸承控制的主流,圖1為數字磁軸承控制系統結構框圖。本文從工業應用的要求和成本考慮,對圖1虛線方框內的控制器進行了容錯設計,提出了雙DSP容錯控制器的方案,而對于傳感器、線圈和功率放大器部分的容錯設計本文不進行討論。

磁懸浮控制器的容錯設計分析

冗余是實現容錯和提高可靠性的一種有效方法,對于磁軸承DSP控制系統來說,其本身的時間余量和程序空間余量都非常有限,故主要是采用硬件冗余,即采用多DSP冗余設計來提高系統的可靠性。

在多機冗余系統設計中,關鍵問題是多機的重構策略、多機的仲裁切換邏輯及多機運行的同步等。小規模的終端系統相對于功能強大的中央控制系統有四個明顯的特點:系統結構較簡單、成本較低;軟硬件資源比較缺乏;必須具備很好的實時性能;運行時間余度太小。通過以上分析與對成本的考慮,本文提出了針對工業應用的雙機熱備冗余控制系統設計方案。

設計原理

本控制系統結構如圖2所示,其中冗余核心控制功能是通過CPLD來實現的。模擬信號分別輸入到兩個DSP進行運算,由中心仲裁模塊選擇主DSP,然后由主DSP來處理輸出到D/A轉換的數據、時序和RS-232的輸出信號。

輸入緩沖模塊

為了消除輸入端輸入阻抗帶來的影響,對于數字信號增加一級緩沖器,可以減小外圍電路的干擾。本系統中,主要是進行RS-232和晶振、復位、外部中斷輸入信號的緩沖(RS-232的輸出接口由主DSP進行控制)。另外,對于模擬信號本設計通過電壓跟隨器來實現阻抗匹配,并減小了誤差和A/D轉換的時間。

DSP時鐘同步的實現

由于本設計方案是通過DSP的完全同步來實現冗余控制的,故采用雙DSP共同使用一個晶振信號的方式。系統工作時,要待電源穩定和晶振完全起振后,才能對DSP進行復位。通過對實驗室現有的控制系統的測試,電源穩定和晶振穩定起振的時間大概是40ms,故復位時間應選擇大于該值。此外,為了提高其抗干擾性,復位后的信號經過施密特觸發器后最好先經過CPLD緩沖,然后再接到DSP的復位端。

硬件故障判決模塊

本設計中使用每個DSP?CLKOUT引腳的輸出信號作為判決硬件故障的基本條件。如果DSP硬件正常工作,CLKOUT引腳將輸出固定的時鐘波形;如果系統的CLKOUT沒有時鐘波形輸出,將認為該DSP硬件不正常,然后由中心仲裁模塊來隔離該DSP。其具體實現方法就是CLKOUT信號經CPLD實現的分頻器后送到單穩態觸發器74LS123,若系統的CLKOUT信號不正常,74LS123會產生跳變,驅使中心仲裁模塊隔離不正常DSP。

輸出總線表決模塊

輸出總線表決模塊主要實現系統的容錯,解決系統的軟故障。當兩DSP的總線輸出信號進行比較時,如果不相同,則表明某個DSP或者兩個DSP都產生了軟故障,系統抑止錯誤輸出,并由中心仲裁模塊對此情況進行處理,使系統實現容錯功能。考慮到A/D轉換的誤差,本設計只對輸出數據總線的高8位進行表決。?

中心仲裁模塊

中心仲裁模塊主要是分析由輸出總線表決模塊和硬件故障判決模塊輸出的結果,并做出判斷,確定主DSP。主DSP的功能主要是控制對外的輸出,包括控制D/A轉換輸出和RS-232的輸出。

中心仲裁模塊的仲裁方式

當硬件判決模塊和軟件表決模塊都沒有報錯,則系統采用默認的DSP1為主DSP;如果硬件判決模塊有一塊DSP報錯,則隔離出錯的DSP,另一個為主DSP?,并且報警;如果兩個DSP都報錯,則會報告系統的錯誤,并提供控制系統產生錯誤的接口信號,讓系統在最短的時間里啟動安保系統。當兩個DSP都沒有產生DSP硬件報錯時,如果軟件表決模塊報錯,則通過CPLD啟動復位信號,重新復位兩個DSP,并由CPLD核心控制模塊記錄復位次數,如果系統連續復位次數超過四次且沒有出現一次正確的輸出總線結果或兩個DSP在線自檢均沒有通過,將會啟動安保系統;如果有一個DSP自檢不通過,則隔離該DSP,系統會輸出報警信號,同時主DSP控制權交給另一DSP;如果復位次數小于四次,且出現了正確的輸出總線結果,CPLD模塊會清除復位計數次數,主DSP依然是DSP1。

DSP軟件實現

系統的軟件流程框圖如圖3所示,其中虛線方框內是通過CPLD實現的。在DSP系統中,使用了看門狗模塊,來解決系統程序跑飛問題。系統復位后,通過檢測看門狗電路復位標志位來檢測系統程序狀態,如果是系統看門狗復位,通過軟件使DSP產生輸出總線報錯,其結果與輸出總線報錯處理方式一樣;否則為由仲裁模塊引起的復位,并且執行在線自檢。如果在線自檢不通過,CPLD會自動隔離硬件。設計中為減小系統的復位時間和控制系統的連續性,存儲數據的時候采用了雙口RAM?idt7133,這樣可以在復位后快速的采用前一次計算的暫存數據(相互取對方數據,并且與自己的數據進行平均),從而使復位對系統的影響降到最小。

在線自檢的實現

通過CPLD中心仲裁模塊來控制信號傳輸控制門,實現A/D轉換,轉換成基準電平(本設計采用2.5V)后再通過實際的控制算法來計算,并將結果輸出到CPLD與離線計算好的結果(存儲在CPLD上)進行比較,如果實時計算結果和離線結果相同,則表示系統自檢通過,否則,自動隔離自檢不通過的DSP。

系統的可靠性評估

系統的中心控制模塊是采用CPLD實現的,其可靠性遠高于基于程序實現的DSP,本系統中把CPLD的故障率近似認為是0,即平均無故障時間遠大于DSP。

根據電子系統模型可知,單機的可靠性隨時間變化服從指數分布,即為Ri(t)=e-lit(li為故障率),所以單機系統的平均無故障時間為1/l,而本方案的無平均故障時間為:

顯然,本系統的無故障時間為單機運行的1.5倍,較大的提高了控制器系統的可靠性。

結語

本文提出的磁懸浮容錯控制器方案,采用了軟硬件協同設計,實現了故障診斷和系統重建的功能,較大的提高了控制器的可靠性,為磁軸承的工業推廣應用提供了性能保障。?

電子發燒友App

電子發燒友App

評論