思維再縝密的程序員也不可能編寫完全無缺陷的C語言程序,測試的目的正是盡可能多的發(fā)現(xiàn)這些缺陷并改正。這里說的測試,是指程序員的自測試。前期的自測試能夠更早的發(fā)現(xiàn)錯誤,相應(yīng)的修復(fù)成本也會很低,如果你不徹底測試自己的代碼,恐怕你開發(fā)的就不只是代碼,可能還會聲名狼藉。

2023-09-19 16:24:41 270

270

具有三級輸出電壓的電源電路圖

2019-05-29 09:33:55

具有極性自動轉(zhuǎn)換電路圖相關(guān)資料分享

2021-05-24 06:40:05

有上節(jié)點電路圖和下節(jié)點電路圖,和一個程序,怎么仿真呢?

2015-06-03 13:26:11

A8810S1具有哪些特性應(yīng)用?

2021-10-09 07:57:12

AD7810具有哪些功能參數(shù)?AD7810的典型應(yīng)用

2021-04-21 06:14:25

本文介紹了ADRF6807主要特性,方框圖, 基本的連接電路, 評估板電路圖和材料清單(BOM), 評估板元件布局圖以及評估板通用特性,噪音特性別和相位噪音特性測試圖。

2021-05-25 07:06:47

AH6956具有哪些參數(shù)特性?

2022-02-23 06:40:42

AH8676具有哪些功能參數(shù)?

2022-02-23 07:46:08

BK3266具有什么特性?

2021-09-28 07:47:14

bq76920具有哪些特性功能?BQ76920EVM電路圖中DNP標(biāo)識的含義是什么?

2021-09-26 08:57:20

CRS10具有什么功能?怎么使用?基于LMS8962與CRSl0的傾角測量系統(tǒng)的原理與設(shè)計

2021-04-15 06:28:23

CX26824/8具有哪些特性參數(shù)應(yīng)用?

2021-05-11 06:41:19

CYPRESS2131具有什么特點?CYPRESS2131在圖像采集中的應(yīng)用是什么?

2021-06-02 07:05:53

DA14580具有哪些功能特性優(yōu)勢?

2021-10-09 07:29:40

自己做的板子,現(xiàn)在用F28069調(diào)試CAN通信,應(yīng)用controlsuite例程自測試功能,可以運行,收發(fā)正常,將自測試改成正常模式,就無法正常工作

2018-09-07 11:24:11

FBT測試儀電路圖原理圖

2008-12-07 10:31:23

GP8502具有哪些特性應(yīng)用?

2021-06-22 06:07:18

HC32F4A0具有哪些特性?

2022-01-26 07:18:21

HT1621具有哪些功能特性參數(shù)?

2022-01-27 06:01:40

法是一種針對時序電路芯片的DFT方案.其基本原理是時序電路可以模型化為一個組合電路網(wǎng)絡(luò)和帶觸發(fā)器(Flip-Flop,簡稱FF)的時序電路網(wǎng)絡(luò)的反饋。內(nèi)建自測試 內(nèi)建自測試(BIST)設(shè)計技術(shù)通過在

2011-12-15 09:35:34

IMC300具有哪些特性?

2021-06-16 06:32:32

LMV831電壓跟隨器電路圖LMV831具有哪些特性?

2021-03-11 08:12:07

8章中提到的寄存器都沒有引用這個自測試位。能否指出這個自測試位在哪個寄存器中。#lsm330dlc自檢以上來自于谷歌翻譯以下為原文 Hello, For a project we

2019-02-20 06:41:24

本文介紹了LTC5569主要特性, 方框圖, 下變換器測試電路圖以及多種應(yīng)用電路。

2021-06-01 06:23:21

應(yīng)用程序: 此示例代碼是MA35D1系列微處理器的實時處理器( RTP) 的自測試庫。 此庫執(zhí)行芯片的自測試功能, 以滿足市場要求的安全要求。 當(dāng)芯片出現(xiàn)錯誤時, 可以實時檢測, 系統(tǒng)可以保持功能

2023-08-29 07:04:24

MAX1200具有什么功能特點?MAX1200是什么工作原理? MAX1200與DSP的接口電路

2021-04-21 06:22:10

MS1656具有什么特性?

2021-11-09 06:21:09

MS1850具有哪些參數(shù)?

2022-02-11 07:03:10

MS35775具有哪些特點應(yīng)用?

2021-10-28 08:01:22

MS9282具有哪些特點?

2022-02-11 08:14:37

MSP430具有什么優(yōu)勢?

2021-11-08 08:53:21

NRF24L01具有哪些參數(shù)特性?如何使用?

2021-12-20 06:17:18

Nordic nRF51822具有哪些功能特性?

2021-10-08 06:53:13

RK3288具有哪些參數(shù)?

2022-03-03 07:01:26

RK3399具有哪些特性參數(shù)應(yīng)用?

2022-03-07 07:04:00

RS-485具有哪些特點應(yīng)用?

2021-12-10 06:33:03

STC8951單片機不斷電下載的方法(親自測試過)對于STC89C51系列單片機如果要下載程序,我們需要先斷電,點擊下載,再給單片機上電這時,他就會自動下載程序。這是因為單片機在冷啟動時,首先執(zhí)行

2013-04-30 01:04:20

STM32具有哪幾個時鐘源?

2021-11-23 07:14:17

TPS5430具有哪些特性?怎樣去設(shè)計一種基于TPS5430的輸入電壓應(yīng)用電路?

2021-10-14 07:13:33

USB電路圖集 (有鼠標(biāo),U盤,MP3電路圖)USB鼠標(biāo)原理圖USB鼠標(biāo)原理圖紅外線遙控鼠標(biāo)電路圖u***光電鼠標(biāo)電路圖u***轉(zhuǎn)rs232接口電路圖采用USB芯片及M8的ISP接口轉(zhuǎn)接電路圖紅外線遙控鼠標(biāo)電路圖

2009-04-15 18:51:12

WM8994具有哪些特征?

2022-02-23 07:30:11

XM8A51216具有哪些特點功能?

2021-10-21 06:04:37

msp430x14x用TINERB產(chǎn)生6路PWM信號,親自測試可行

2016-07-19 21:52:22

nRF51422具有哪些特點?

2021-06-22 06:11:09

電子設(shè)備中有各種各樣的圖。能夠說明它們工作原理的是電原理圖,簡稱電路圖。電路圖有兩種,一種是說明模擬電子電路工作原理的。它用各種圖形符號表示電阻器、電容器、開關(guān)、晶體管等實物,用線條把元器件和單元

2021-07-29 08:00:28

我修改了add.S文件,想讓make run_test SIM=iverilog后出現(xiàn)file.可是編譯不了,add.S文件也沒顯示更新。

可是我在測試自測試用例的時候,make compile

2023-08-12 06:50:38

先鋒PIONEER PD-206音響電路圖文件下載

2021-07-06 06:56:38

本帖最后由 eehome 于 2013-1-5 10:06 編輯

具有電阻調(diào)諧的3500-3600KHZ可變頻率振蕩器電路圖2012-11-01shangziyun頻率和脈寬可變的波形發(fā)生器

2012-11-15 16:30:21

1、整機電路圖功能 整機電路圖具有下列一些功能: (1)它表明整個機器的電路結(jié)構(gòu)、各單元電路的具體形式和它們之間的連接方式,從而表達了整機電路的工作原理,這是電路圖中最復(fù)雜的一張電路圖。 (2

2017-08-29 14:06:51

畫電路圖:教材上的電路圖是用什么軟件畫的,畫電路圖的軟件哪個最容易學(xué)。

2022-03-24 16:07:36

請問ADXL345具備自測功能的主要作用是什么?是為了檢驗加速度傳感器本身的性能?進行自測之前是否應(yīng)將offset X、Y、Z全部清零?

2024-01-02 06:07:05

EMI7064具有什么特征?

2021-04-19 06:50:11

GP8311具有哪些特性應(yīng)用?

2021-06-22 06:53:48

本帖最后由 一只耳朵怪 于 2018-6-14 10:25 編輯

eCan 自測試模式下可以產(chǎn)生中斷嗎? F2812

2018-06-14 01:20:48

nRF52833具有哪些功能優(yōu)勢?

2021-06-15 07:13:47

請問誰有電容在線測試的電路圖?? 共享一下,謝謝了!!

2012-12-19 12:21:08

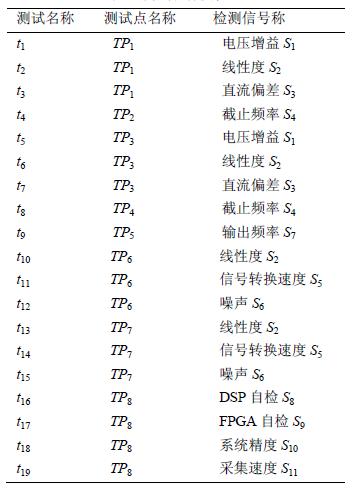

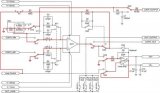

繼電器來選擇所需的測試。圖 1 是整體測試電路。在圖 2 至圖 13 中,信號路徑以紅色顯示,以便與前兩篇文章中所介紹的方法進行比較。圖 1.該電路整合了用于測試運算放大器的自測試電路及雙運算放大器環(huán)路

2018-09-07 11:04:41

這個電路圖的元器件原理圖電容電阻設(shè)置多少,原理圖和實用電路圖有什么關(guān)系?

2017-05-18 11:33:41

霍爾元件AR127具有哪些特性及優(yōu)點?

2022-02-23 06:56:34

電工技術(shù)(電工學(xué)I)典型題解析及自測試題是根據(jù)國家教育部(前國家教委)1995年修訂的“高等工業(yè)學(xué)校電工技術(shù)(電工學(xué)Ⅰ)課程教學(xué)基本要求“編寫的學(xué)習(xí)指導(dǎo)書,主要內(nèi)容是

2008-09-20 21:46:12 0

0 嵌入式存儲器內(nèi)建自測試的一種新型應(yīng)用孫華義 鄭學(xué)仁 閭曉晨王頌輝吳焯焰 華南理工大學(xué)微電子研究所廣州 510640摘要:當(dāng)今,嵌入式存儲器在SoC 芯片面積中所占的比例越來

2009-12-20 09:26:11 38

38 芯片間的互連速率已經(jīng)達到GHz量級,相比較于低速互連,高速互連的測試遇到了新的挑戰(zhàn)。本文探討了高速互連測試的難點,傳統(tǒng)互連測試方法的不足,進而介紹了互連內(nèi)建自測試(I

2010-07-31 17:00:16 15

15 內(nèi)建自測試是一種有效的測試存儲器的方法。分析了NOR型flash存儲器的故障模型和測試存儲器的測試算法,在此基礎(chǔ)上,設(shè)計了flash存儲器的內(nèi)建自測試控制器。控制器采用了一種23

2010-07-31 17:08:54 35

35 介紹了用于IP核測試的內(nèi)建自測試方法(BIST)和面向測試的IP核設(shè)計方法,指出基于IP核的系統(tǒng)芯片(SOC) 的測試、驗證以及相關(guān)性測試具有較大難度,傳統(tǒng)的測試和驗證方法均難以滿足

2010-12-13 17:09:11 10

10

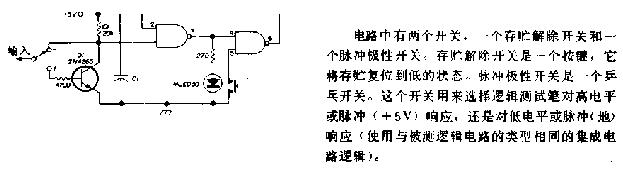

具有存貯功能的邏輯測試筆電路圖

2009-04-07 09:15:28 623

623

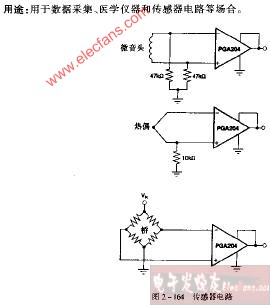

PGA204 PGA206傳感器電路圖

2009-06-26 15:45:21 1628

1628

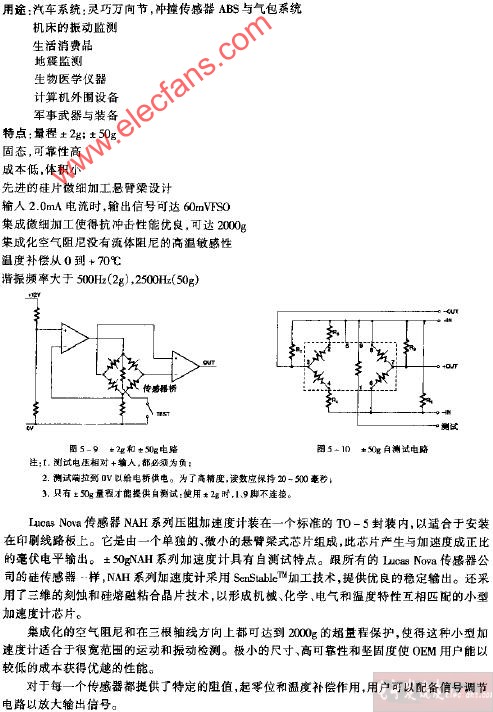

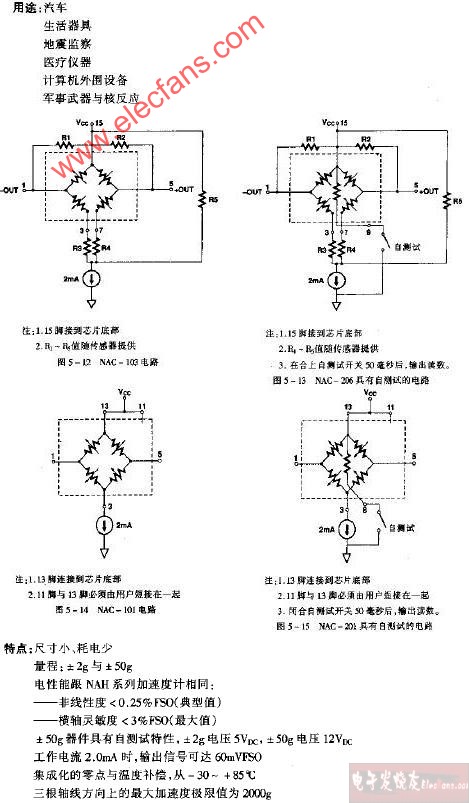

±50g自測試電路圖

2009-07-03 12:03:06 405

405

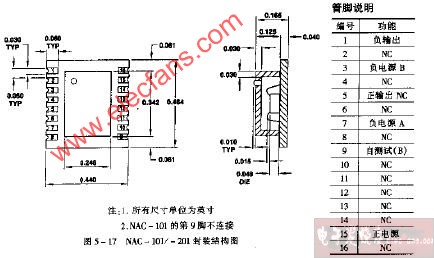

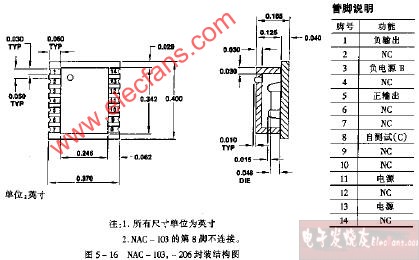

NAC-101 NAC-201封裝結(jié)構(gòu)電路圖

2009-07-03 13:03:13 433

433

NAC-103電路圖

2009-07-03 13:03:48 767

767

NAC-103 NAC-206封裝結(jié)構(gòu)電路圖

2009-07-03 13:04:26 526

526

NAC-101電路圖

2009-07-03 13:06:56 1011

1011

NAC-201具有自測試的電路圖

2009-07-03 13:09:10 399

399

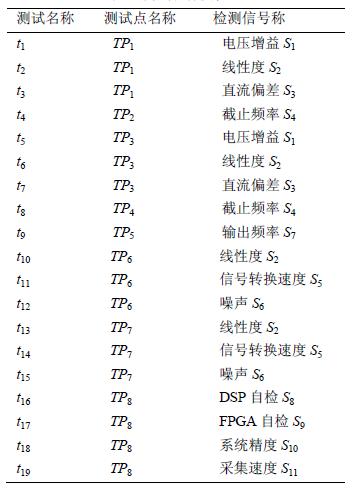

1.引言

在工業(yè)現(xiàn)場、國防軍事、航空航天等領(lǐng)域需要利用電路自身資源進行快速的故障診斷,即要求電路具有自測試功能。為了使復(fù)雜的電路具有自測試功能

2010-11-17 10:34:48 1075

1075

在集成電路內(nèi)建自測試的過程中,電路的測試功耗通常顯著高于正常模式產(chǎn)生的功耗,因此低功耗內(nèi)建自測試技術(shù)已成為當(dāng)前的一個研究熱點。為了減少被測電路內(nèi)部節(jié)點的開關(guān)翻轉(zhuǎn)活

2012-02-01 14:00:36 21

21 一種基于包的邏輯內(nèi)置自測試電路設(shè)計方法

2017-02-07 16:14:56 12

12 在本系列的第 1 部分中,我們?yōu)榇蠹医榻B了三種運算放大器測試電路:自測試電路、雙運算放大器環(huán)路以及三運算放大器環(huán)路。這些電路有助于測試失調(diào)電壓 (VOS)、共模抑制比 (CMRR)、電源抑制

2017-04-08 06:06:34 4796

4796

TMS570LS系列微控制器與可編程內(nèi)置自測試(pbist)實現(xiàn)建筑。的pbist架構(gòu)提供了一種存儲器BIST引擎不同的覆蓋水平在許多嵌入式內(nèi)存實例中。TMS570LS系列微控制器可分為兩類:130

2018-04-16 16:03:38 12

12 仿真結(jié)果:為了評價BIC監(jiān)測儀用于新型并行模擬自測試的可行性,進行了故障仿真。全差分電流傳送器被用作被測器件。在監(jiān)視通過/失敗輸出(圖2)的同時,將每個典型的MOS晶體管的終端故障(短路和開路)分別

2019-11-26 16:36:30 0

0 LBIST (Logic build-in-self test), 邏輯內(nèi)建自測試。和MBIST同理,在關(guān)鍵邏輯上加上自測試電路,看看邏輯cell有沒有工作正常。BIST總歸會在芯片里加入自測試邏輯,都是成本。

2022-08-29 15:33:30 2169

2169 UM2986 STM32U5系列IEC 60730自測試庫用戶指南

2022-11-22 08:21:45 0

0

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

270

270

0

0 38

38 15

15 35

35 10

10 1075

1075

21

21 4796

4796

12

12 0

0 2169

2169

評論